### NASA John H. Glenn Research Center at Lewis Field

## Packaging Technology for 500°C SiC Microsystems

Liang-Yu Chen<sup>\*</sup>, Gary W. Hunter, and Philip G. Neudeck \*Ohio Aerospace Institute/NASA John H. Glenn Research Center at Lewis Field Cleveland, OH 44135

# Outline

- Background: motivations

- Electrical and mechanical characterization facilities

- Thick-film metallization based electrical interconnections

Validation results

- 500°C operable low electrical resistance die-attach

- Method and evaluation results

- Summary

- High temperature MEMS packaging

- Thermal mechanical stability of die-attach

- Acknowledgements

# Background

- 500°C operable sensors/electronics have many applications in NASA aerospace missions

- Sensors/electronics for combustion monitoring and control

- Pressure sensor, gas chemical sensor, and flow sensor for aeronautic engine diagnosis and control

- Sensors/electronics for space probes to inner solar planets

- Atmosphere profile for Venus

- SiC excellent high temperature semiconductor

- SiC electronic devices/sensors/MEMS demonstrated ~ 600°C, most in test probe station

- Systematically validated packaging technology for T > 350°C not available

- 500°C device packaging technology needed

- In situ device testing and commercialization

# NEPP High Temperature SiC Packaging Project

- Collaborating efforts between NASA, industry, university

- GRC: Material selection, package design and fabrication, testing, SiC device

- JPL: NDE of die-attach

- MSFC: Engine test

- UTRC: Dynamic thermal environment tests, FEA evaluation

- CWRU: Assistance in fabrication

# High Temperature SiC Microsystem Packaging

- Electrical interconnection system

- 500°C operable substrates

- Ceramics: Al<sub>2</sub>O<sub>3</sub> and AlN

- 500°C operable electrical interconnection

- Precious metal thick-film metallization

- Au wire-bond

- Conductive die-attach

- Conductive, low electrical resistance

- Thermal mechanical stability

- Mechanical system

- Thermal mechanical reliability of die-attach

# **Test Facilities**

- Testing systems for 500°C packaging materials/ components tests

- Electrical/electronic tests

- Computerized

- Simultaneous measurement of multi-parameters for multi-samples

- Temperature programming

- Mechanical/materials tests

- Die shear (T<sub>R</sub> 500°C) and die tensile (T<sub>R</sub>)

- Wire loop test (T<sub>R</sub>, 500°C later this year)

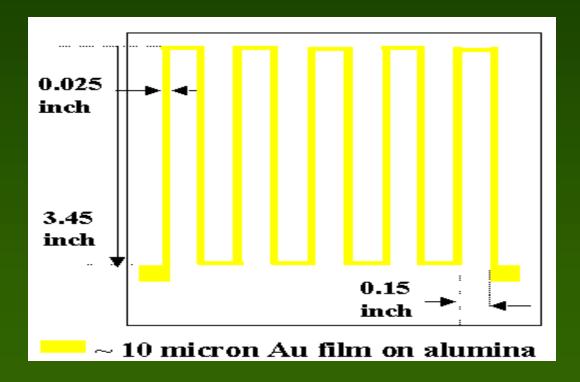

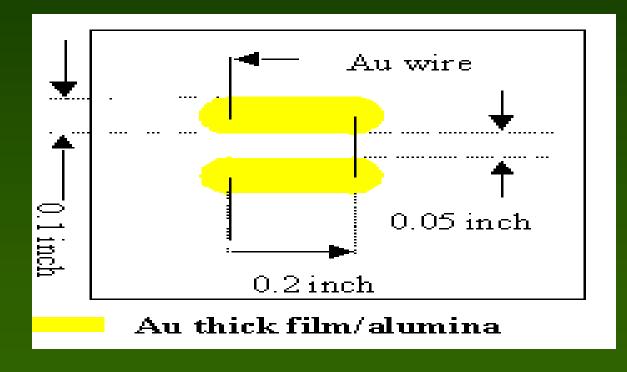

# Au Thick-film Based Interconnections

- Au based thick film metallization

- Screen-printed thick-film wire/pads

- Good adhesion to various ceramic substrates

- Stable in corrosive ambience at high temperatures

- Au thin wire-bond

- Printed thick-film wire/pad and Au wire-bond

- Tested at 500°C with electrical bias

# **Thick Film Based Interconnections**

## **Thick Film Printed Wire**

# **Thick Film Based Interconnections**

**Unit Circuit**

## **Thick-Film Metallization Based Au Wirebond**

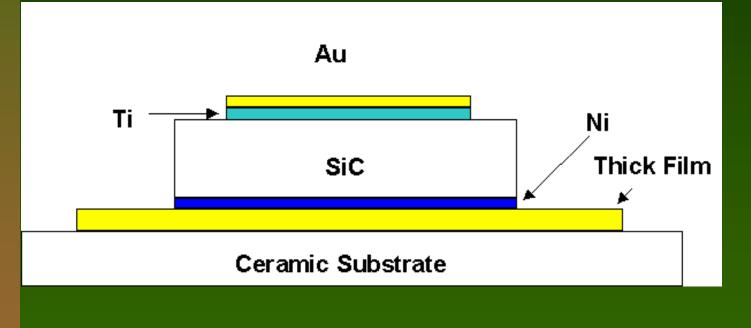

# Conductive Die-attach

- SiC test device

- Backside: Ni/4H-SiC ohmic contact after annealing at high temperature in Ar

- Front-side: Au/Ti/4H-SiC **rectifying** contact

- Au thick-film used as conductive attaching material

Two stops process allowing low ouring temperature

- Two steps process allowing low curing temperature

- AIN substrate: high thermal conductivity and a CTE matches SiC

# **Optimized Die-Attach Process**

- Thick film suggested be cured at 850°C

Best bonding to ceramic substrates

- 850°C may not be comfortable to die

- Optimize thick-film process for die-attach

- Scanning Electron Microscopy (SEM) and Auger Electron Spectroscopy (AES) were used to study the thick film surfaces cured at various temperatures

## **Conductive Die-attach Structure**

# Two-Step Thick Film Process

- AES results indicate

- High curing temperature (~ 850°C) preferred for binder migration to Au/ceramic interface

- SEM results indicate

- Coherent thick film formation at  $\geq$  600°C

- Best adhesion and low temperature exposure to die

- First screen-printed layer cured at 850°C

- Die attached at 600°C with minimal amount of thick film materials

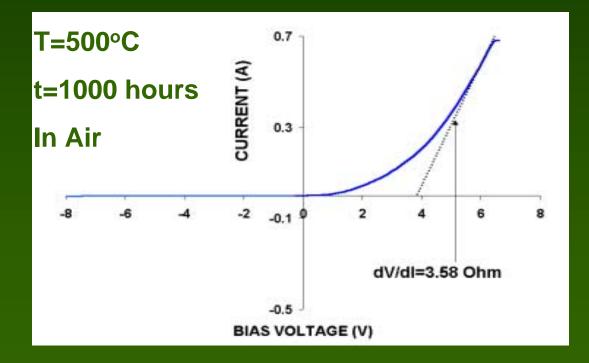

#### I-V Curve of an Attached SiC Diode at 500°C

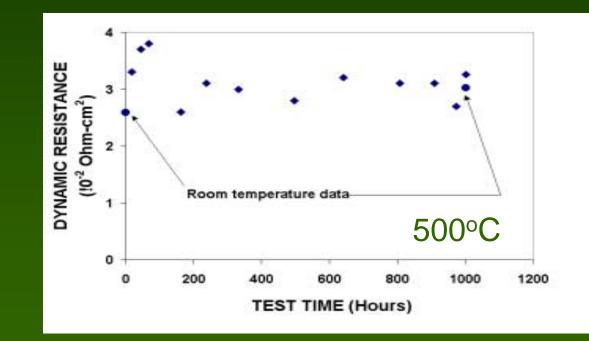

#### **Dynamic Resistance of Attached SiC Diode**

## Test Results

- Attached SiC test chip

- Diode I-V curves characterized at both  $T_R$  and 500°C

- Dynamic resistance of I-V curves indicated die-attach resistance less than  $3.5*10^{-2} \Omega \text{ cm}^2$  at T<sub>R</sub> and  $500^{\circ}\text{C}$  tested for over 1000 hours

- Sufficient shear strength measured at T<sub>R</sub>

- Thick-film based interconnections validated at 500°C

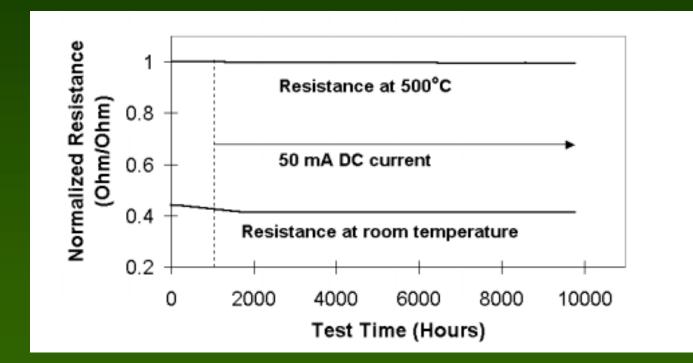

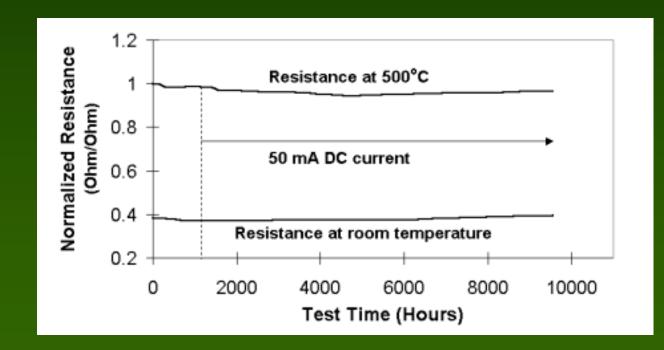

- Thick film printed wires stable at  $T_R$  500°C, with/ without 50mA DC, for ~10000 hours.

- Thick film metallization based wire bond stable at  $T_R$  500°C, with/ without 50 mA DC, for ~10000 hours.

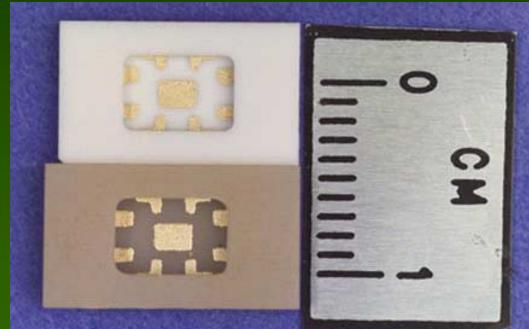

# 500°C Chip Level Package

- AIN and AI<sub>2</sub>O<sub>3</sub> substrates

- Au thick-film metallization based wire-bond

- Au thick-film based low resistance conductive SiC die attach scheme

- T<sub>R</sub> 500°C operable

- Tested in oxidizing environment

- Basic elements electrically tested at T<sub>R</sub> 500°C for ~10000 hours

- Packaging HT SiC sensors and circuits

## High Temperature Chip Level Package

**AIN** based

# Summary

- AIN and 96% Al<sub>2</sub>O<sub>3</sub> selected as substrates

- Au thick-film based interconnections validated at T<sub>R</sub> and 500°C for ~10000 hours with/without DC bias

- Au thick-film based conductive SiC die-attach scheme evaluated for 500°C operation

- Attached SiC diode electrically tested at 500°C for >1000 hours in oxidizing environment

- The upper limit of die-attach resistance <  $3.5^{*}10^{-2} \Omega$ -cm<sup>2</sup> at both T<sub>R</sub> and 500°C

## High Temperature MEMS Packaging

- Wide operation temperature range

- ✤ T<sub>R</sub> 500°C

- MEMS devices are sensitive to thermal mechanical stress

- Device mechanical operation

- CTE mismatch of die-attach materials

- Non-electrical interactions between the device and environment

- Chemical, mechanical, magnetic, optical

- Thermal mechanical optimization of die-attach is critical to the reliability of packaged devices

### Acknowledgements

- 2<sup>nd</sup> NEPP Annual Conference Committee

- Thick-film test samples fabricated in Case Western Reserve University

- Jih-Fen Lei and Lawrence G. Matus at GRC

- The technical support team at GRC

- Phillip J. Zulueta and David Mih at JPL

- High temperature SiC device packaging efforts at GRC are currently supported by NEPP and GMI