# NEPP Electronic Technology Workshop June 11-13, 2012

National Aeronautics and Space Administration

# **NAND Flash Qualification Guideline**

#### **Jason Heidecker**

Jet Propulsion Laboratory, California Institute of Technology

© 2012 California Institute of Technology. Government sponsorship acknowledged.

# NASA

# **Table of Contents**

- **1. NAND Overview**

- 2. Floating Gate Memory

- 3. Array Organization

- 4. Operation

- **5.** Applications

- 6. Reliability Issues

- 7. Failure Modes

- 8. Screening & Qualification

- 9. System Level Considerations

- **10.** Other Recommendations

- **11.** End of the Road for Flash?

- **12.** Sources/References

# What is NAND Flash?

- Unique architecture.

- PROGRAM/READ by PAGE.

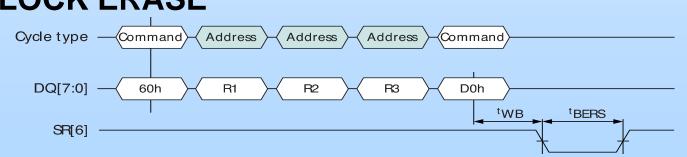

- ERASE by BLOCK.

- Built on CMOS. TSOP packages.

- Nonvolatile; low standby power.

- VERY high density.

- Mature technology, billions of chips produced over decades.

#### Only memory to offer both Gb density and nonvolatility.

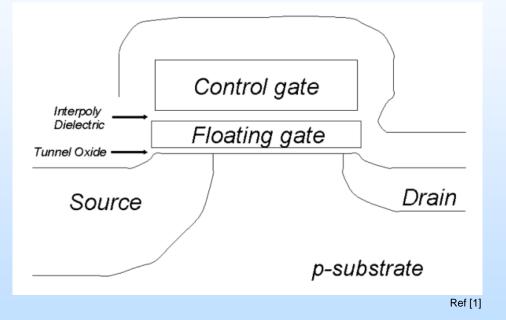

### **Floating Gate Memory Cell**

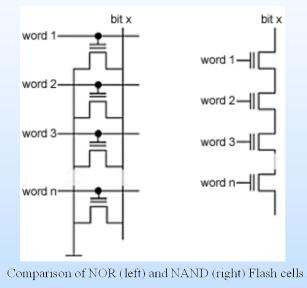

### **Array Organization**

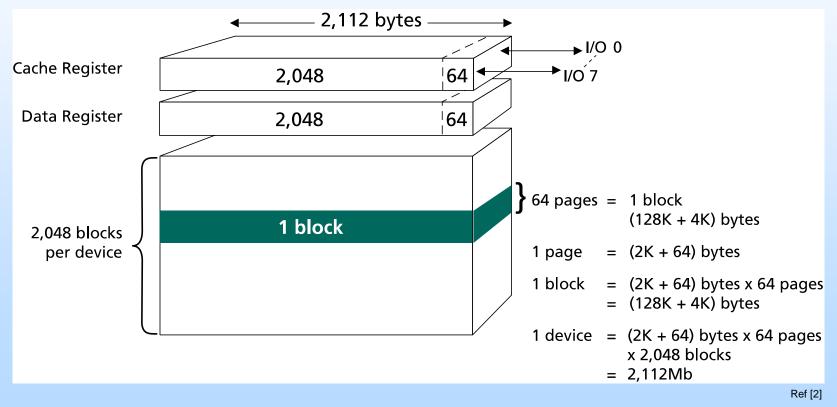

Bits, Bytes, Pages, and Blocks

#### **Array Organization for 4 Gb Micron Device**

#### **Operation**

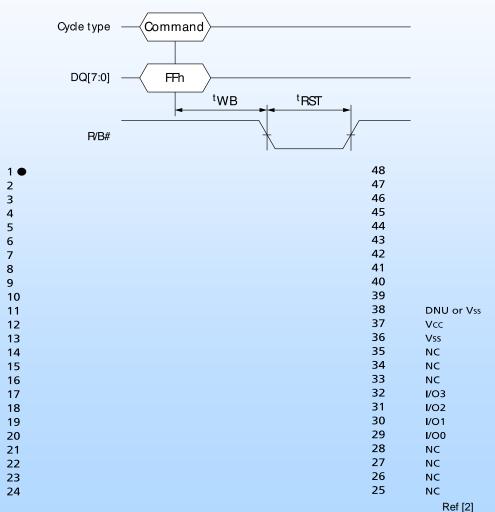

#### Commands, Addresses, and Data On Same I/O

RESET (FFh) Operation

To be presented at the 3rd NASA Electronic Parts and Packaging (NEPP) Program Electronic Technology Workshop June 11-13, 2012, NASA GSFC, Greenbelt, MD.

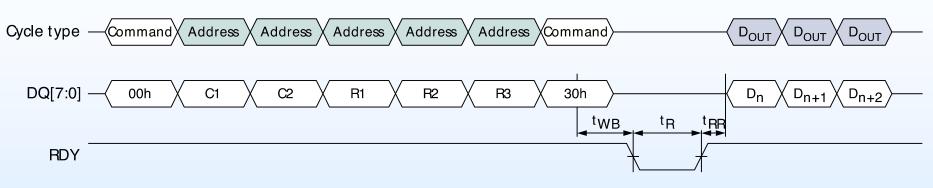

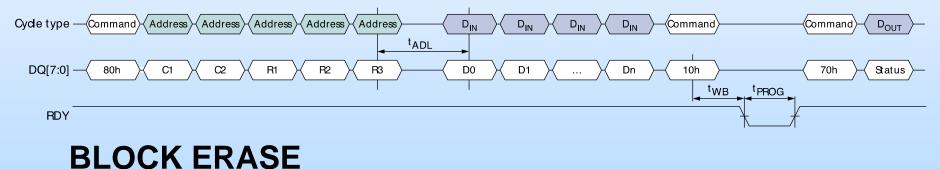

### **Operation**

#### **PAGE READ**

#### **PAGE PROGRAM**

# **Applications**

#### COMMERCIAL

#### Mobile Computing

- Cell Phones

- MP3

- "Thumb" Drives

- Hard Drives

- "Instant On" discs

#### SPACE

- NVM Data Storage

- Engineering & Science Data

10 x 128 Gb MLC NAND Flash parts on space project (JPL)

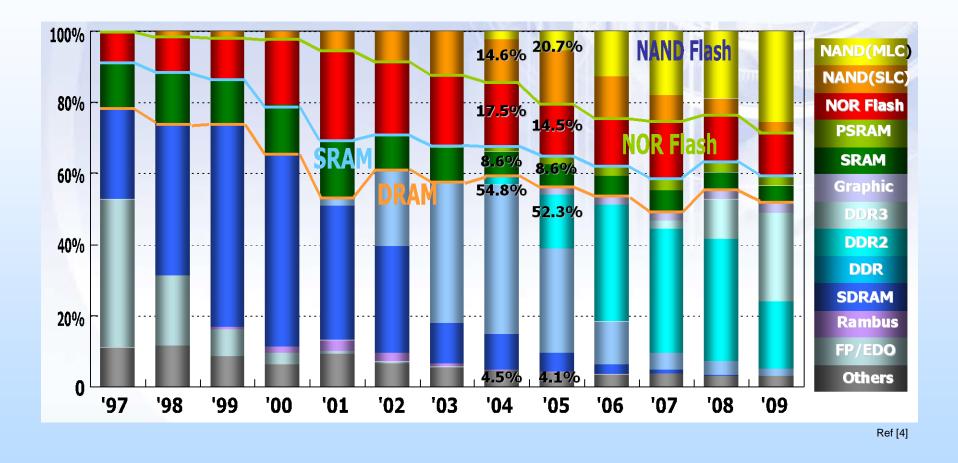

#### **NVM Market**

# **Reliability Issues**

Reliability (bit errors) is getting • NAND Flash Memory worse with newer NAND technologies. Floating Gate Scaled Plastic NAND Memory Cell CMOS Packaging Architecture NAND Reliability Smaller Vth/level = More Errors • Fowler-Nordheim Tunneling • High Voltage High Voltage High Voltage 011 for Erase and Program 01 010 uses destructive high voltages 0 000 MLC Flash SLC Flash TLC Flash 00 ~20 V 001 1 Bit Per Cell 2 Bits Per Cell 3 Bits Per Cell 101 2 States 4 States 8 States 10 100 1 Four Areas of Focus: 110 11 111 1. Bad Blocks Low Voltage Low Voltage Low Voltage Ref [5] 2. Endurance **Smaller Margins Means Less Reliability** (Susceptibility to disturb and Stress Induced 3. Retention Leakage Current (SILC)) 4. Disturb

### **Bad Blocks**

- Devices are expected to ship with a specified number of bad blocks.

- Specification can be as high as 5%.

- Parts may be shipped with 1% bad blocks, but spec says device should not exceed 5% bad blocks (in this case) before endurance specification is met.

- Blocks will "go bad" with use.

- Bad block is defined as having a certain bit error rate (BER).

For example, a particular 64 Gb Micron TLC device has 2736 blocks:

- Spec says: it has an

- endurance specification of 500 cycles

- minimum number of valid block of 2626

- 60-bit ECC required per 1146 bytes of data

Therefore, the user should never see more than 60 bit errors per 1146 bytes of data in more than 110 blocks, up to 500 cycles.

#### **Data Retention**

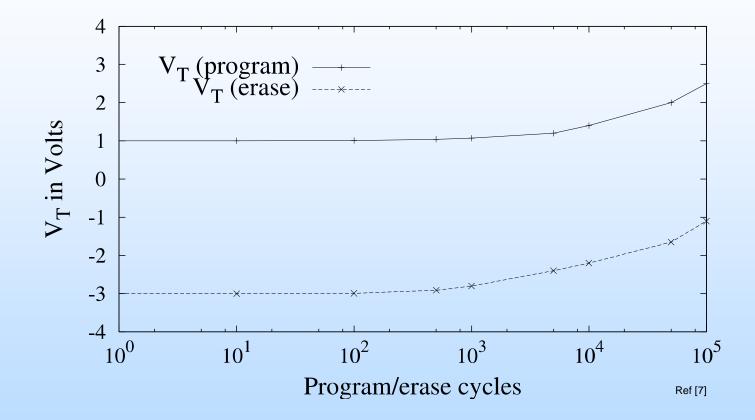

#### **Endurance**

### **Read Disturb**

- Flash also susceptible to Program and Erase Disturb, but only Read disturb is prevalent in modern devices

- Read Disturb confined to block being operated on

- Stressed cells are in unselected pages

- Nondestructive

- Disturb occurs when charge collects on the floating gate, causing the cell to appear weakly programmed

#### **Failure Modes**

| Failure Mode             | Detection Method           | Countermeasure    |

|--------------------------|----------------------------|-------------------|

| Erase Failure            | Check status after erase   | Block replacement |

| Program Failure          | Check status after program | Block replacement |

| Bit Errors (within spec) | Verify ECC                 | ECC correction    |

| Bit Errors (beyond spec) | Verify ECC                 | Block replacement |

# **Screening & Qualification**

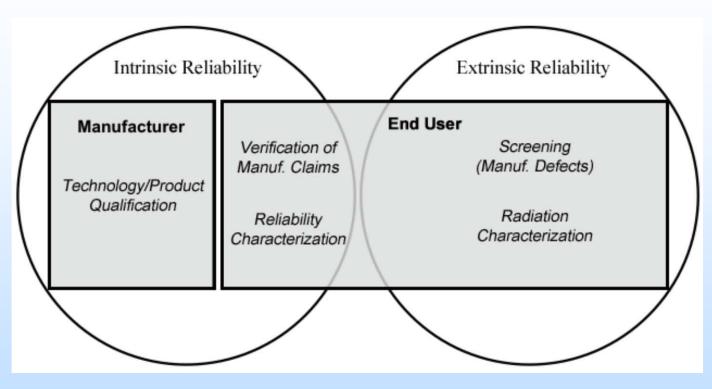

Diagram depicting the roles of the manufacturer and space project in screening and qualifying an EEE device for space application.

# **Screening**

| Step | Test                                             | Requirements                                                               | Sample Size & Notes |                    |

|------|--------------------------------------------------|----------------------------------------------------------------------------|---------------------|--------------------|

|      |                                                  |                                                                            | Level 1<br>Mission  | Level 2<br>Mission |

| 1    | Glass transition temperature, Tg                 | Thermal Mechanical Analysis<br>(TMA)                                       | 3 pc                | 3 pc               |

| 2    | Serialization                                    |                                                                            | 100%                | 100%               |

| 3    | Electricals (AC, DC, Functional)                 | Test to datasheet.<br>Read & record data.<br>Tri-temp (-40°C, 25°C, 85°C). | 100%                | 100%               |

| 4    | Dynamic Burn-In                                  | MIL-STD-883, Method 1015, 125°C                                            | 100%<br>240 hrs     | 100%<br>160 hrs    |

| 5    | Electricals (AC, DC, Functional)                 | Test to datasheet.<br>Read & record data.<br>Tri-temp (-40°C, 25°C, 85°C). | 100%                | 100%               |

| 6    | Delta Calculations                               | 25°C                                                                       | 100%                | 100%               |

| 7    | Percent Defective Allowable<br>(PDA) Calculation |                                                                            | 5% PDA <sup>1</sup> | 5% PDA             |

| 8    | Stabilization Bake                               | 125°C, 24 hours                                                            | 100%                | 100%               |

| 9    | Flight Part Storage                              | In accordance with [5].                                                    | 100%                | 100%               |

<sup>1</sup> 3% PDA for functional parameters at 25°C.

# NASA

## Qualification

|      |                                           |                                                                            | Sample Size & Notes  |                      |

|------|-------------------------------------------|----------------------------------------------------------------------------|----------------------|----------------------|

| Step | Test                                      | Requirements                                                               | Level 1              | Level 2              |

|      |                                           |                                                                            | Mission              | Mission              |

| 12   | Temp Cycling                              | MIL-STD-883, Method 1010,<br>Condition B                                   | 22 pc,<br>300 cycles | 22 pc,<br>100 cycles |

| 13   | Electricals (AC, DC, Functional)          | Test to datasheet.<br>Read & record data.<br>Tri-temp (-40°C, 25°C, 85°C). |                      |                      |

| 14   | High Temperature Operating Life<br>(HTOL) | MIL-STD-883, Method 1005, 125°C                                            | 45 pc                | 22 pc                |

| 15   | Electricals (AC, DC, Functional)          | Test to datasheet.<br>Read & record data.<br>Tri-temp (-40°C, 25°C, 85°C). |                      |                      |

| 16   | Destructive Physical Analysis<br>(DPA)    | 2 pc from temp cycled samples,<br>rest from life tested samples            | 5 pc                 | 3 pc                 |

| 17   | Reliability Characterization              | See Table 4                                                                | 10 pc                |                      |

| 18   | Radiation Characterization                | TID and SEE per radiation specialist recommendation                        | Per rad s            | pecialist            |

## **Reliability Characterization**

| Step | Test                        | Requirements                                                                         |

|------|-----------------------------|--------------------------------------------------------------------------------------|

| 1    | Endurance Cycling           | Up to 1.5x application endurance requirement                                         |

| 2    | Data Retention Bake         | Three temperatures; at 1.5x application endurance requirement                        |

| 3    | Read Disturb                | Multiple reads after 0, 0.5x, 1.0x,<br>and 1.5x application endurance<br>requirement |

| 4    | Worst Case UBER Calculation | At 1.5x application endurance requirement                                            |

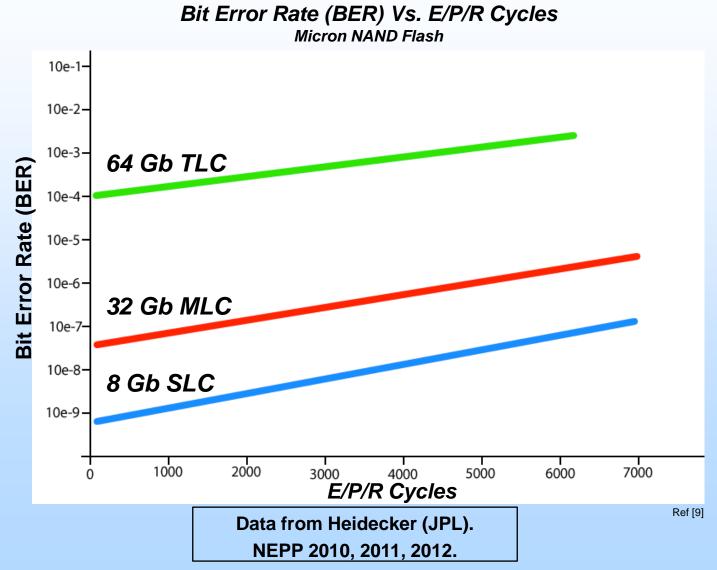

#### **Endurance Cycling**

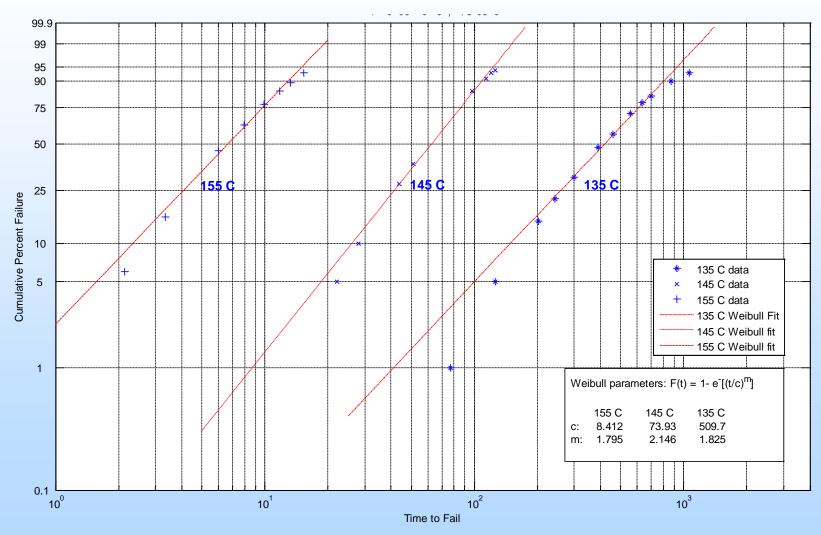

#### **Data Retention Bake**

Data is for Demonstration Only - Not Real Flash Data

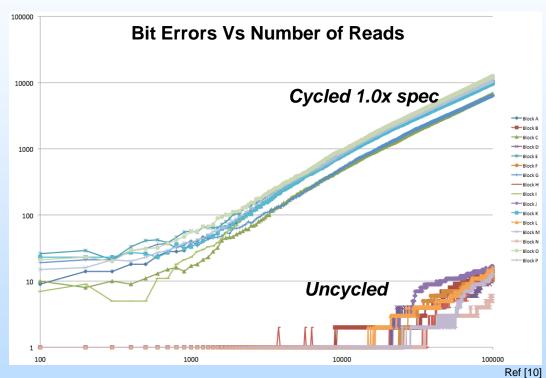

#### **Read Disturb**

#### • PURPOSE

Measure how BER worsens with multiple reads of block of data

#### DISTURB TEST

- 1. Erase

- 2. Program

- 3. Read many times

- Repeat test after cycling device. Perform at:

- 0x

- 0.5x

- 1.0x

- 1.5x

Read disturb error rate much worse in parts that have consumed erase/program/read cycles.

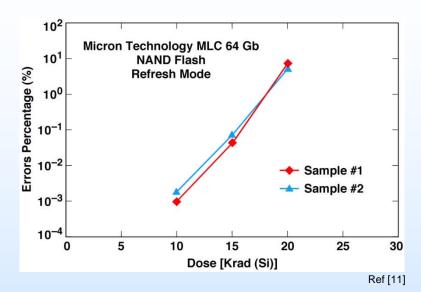

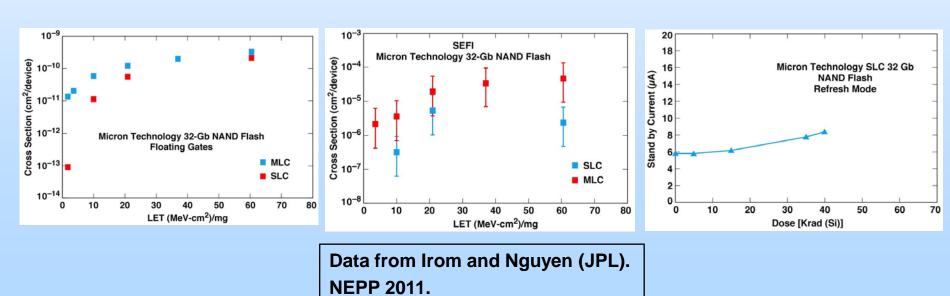

# **Radiation Effects**

- Every lot should be tested

- Total Ionizing Dose (TID)

- Single Event Upset (SEU)

- Single Event Fault Interrupt (SEFI)

- Flash can be tested for different applications:

- Refresh: Erase/Program Between Read

- No Refresh: Read Only

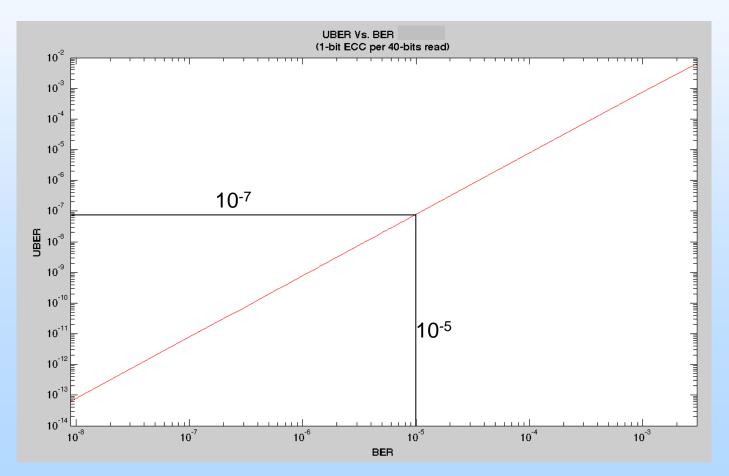

When calculating uncorrectable bit error rate (UBER) from raw NAND bit error rate (BER), the worst case BER should be used. Here's a general example, but users should tailor to their specific application or use case:

$BER_{worst case} = BER_{radiation} + BER_{cycling} + BER_{disturb}$

To be presented at the 3rd NASA Electronic Parts and Packaging (NEPP) Program Electronic Technology Workshop June 11-13, 2012, NASA GSFC, Greenbelt, MD.

# **System Level Considerations**

#### **Error Correction Codes (ECC)**

- Always required with NAND Flash.

| NAND<br>Type | Datasheet ECC Requirement         | Corresponding<br>Bit Error Rate | Recommended ECC                              |

|--------------|-----------------------------------|---------------------------------|----------------------------------------------|

| SLC          | 1-bit ECC per 528 bytes of data   | 0.02%                           | SEC/DEC Hamming Code<br>or Reed-Solomon Code |

| MLC          | 12-bit ECC per 539 bytes of data  | 0.28%                           | BCH Algorithms                               |

| TLC          | 60-bit ECC per 1146 bytes of data | 0.65%                           | Low Density Parity Check<br>(LDPC) Codes     |

# **Other Recommendations**

- Pure Tin Leads

- All NAND Flash are PEMS, which have pure tins leads. Leads must be retinned or solder-dipped before installation onto flight boards.

- Disturb Error Mitigation

- Limit the number of reads between programming, sequentially program pages in a block, and minimize partial-page programming [Ref: 12].

- Moisture Sensitivity (PEMS Storage)

- Plastic packaging is hygroscopic

- Need to be stored in humidity controlled environments

- Should be "baked out" prior to assembly to prevent popcorning or other damage

- Electrostatic Discharge (ESD) Sensitivity

- Most NAND Flash devices are classified has having ESD sensitivities of Class 1C (>1000 V HBM) or better.

- Most standard ESD practices (static dissipative wrist straps, workbenches, and storage bags) will prevent damaging the device.

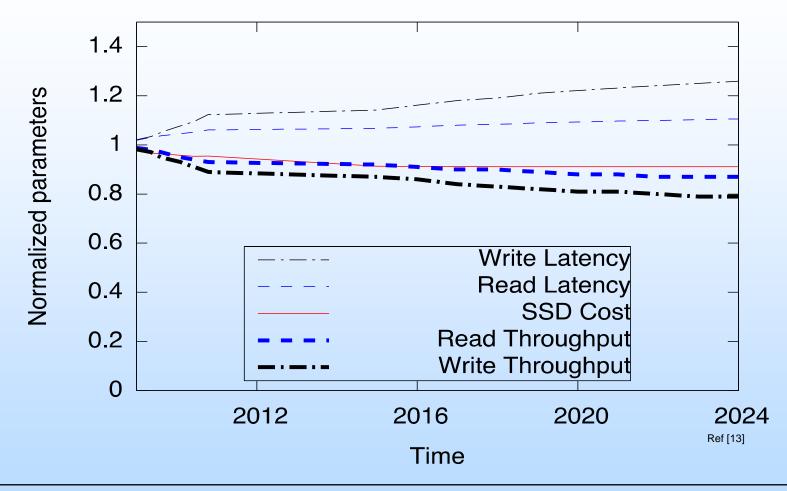

### **End of the Road for Flash?**

The Bleak Future of NAND Flash Memory

Laura M. Grupp†, John D. Davis‡, Steven Swanson†

*†Department of Computer Science and Engineering, University of California, San Diego ‡Microsoft Research, Mountain View*

#### What's Next?

# **Could it be MRAM?**

Stay Tuned...

#### **Sources/References**

- **1.** Bez, R. "Introduction to Flash Memory." Proceedings of the IEEE, Vol. 91, No. 4, April 2003.

- 2. 4 Gb NAND SLC Datasheet, "2\_4\_8gb\_nand\_m49a\_\_1.fm Rev. D 12/06 EN." Micron, Inc.

- **3.** TN-29-19, "NAND Flash 101: An Introduction to NAND Flash and How to Design It In to Your Next Product." Micron, Inc.

- 4. Jung, T.S. "Memory Technology and Solutions Roadmap," Samsung Analyst Day, 2005.

- 5. Yaakobi, L. "Characterization and Error-Correcting Codes for TLC Flash Memories." International Conference on Computing, Networking and Communications, Data Storage Technology and Applications Symposium, 2012.

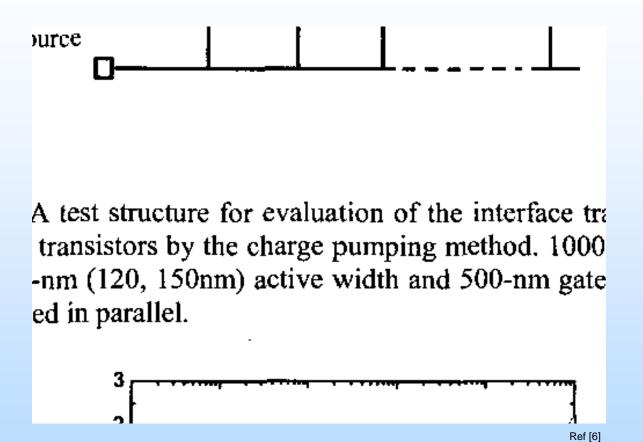

- 6. Lee, J. "Degradation of Tunnel Oxide by FN Current Stress and Its Effects On Data Retention Characteristics of 90-nm NAND Flash Memory Cells," IRPS, 2003.

- 7. Desnoyers, P. "Empirical Evaluation of NAND Flash Memory Performance," HotStorage, 2009.

- 8. Prouty, W. "NAND Flash Reliability and Performance, The Software Effect." Flash Memory Summit, 2007.

- 9. Heidecker, J. "NAND Flash Screening and Qualification Guideline for Space Application." NASA Electronics and Packaging Program (NEPP), 2011.

- **10.** Qualification data for 128 Gb MCM MLC NAND for SMAP Mission, JPL, 2010.

- **11.** Irom, F. "Radiation Tests of Highly Scaled, High-Density, Commercial, Nonvolatile NAND Flash Memories," NASA Electronic Parts and Packaging Program (NEPP), 2011.

- **12.** Sheldon, D. "Disturb Testing in Flash Memories." NASA Electronic Parts and Packaging Program (NEPP), 2009.

- **13.** Grupp, L. "The Bleak Future of NAND Flash Memory." University of San Diego, 2011.