The document and process conversion Measures necessary to comply with This revision shall be completed by 30 September 2001. INCH-POUND

MIL-P-50884D <u>28 December 2000</u> SUPERSEDING MIL-P-50884C 4 May 1984 (See 6.6)

## MILITARY SPECIFICATION

# PRINTED WIRING BOARD, FLEXIBLE OR RIGID-FLEX GENERAL SPECIFICATION FOR

Inactive for new design after 28 February 1999. For new design use MIL-PRF-31032.

This specification is approved for use by all Departments and Agencies of the Department of Defense.

#### 1. SCOPE

- 1.1 <u>Scope</u>. This specification establishes the performance and qualification requirements for flexible and rigid-flex printed wiring boards with or without plated through holes (see 6.1). Verification is accomplished through the use of one of two methods of product assurance (appendix A or appendix B). Detail requirements, specific characteristics, and other provisions which are sensitive to the particular intended use are specified in the applicable master drawing.

- 1.2 Classification. Printed wiring boards are classified by 1.2.1 and 1.2.2.

- 1.2.1 Type. Printed wiring boards are of the types shown, as specified (see 3.1).

- Type 1 Singled-sided flexible printed wiring board (see 6.4.2.1) with or without shields or stiffeners.

- Type 2 Double-sided flexible printed wiring board (see 6.4.2.2) with or without shields or stiffeners with or without plated-through holes.

- Type 3 Multilayer flexible printed wiring board with plated holes (see 6.4.2.3) and with or without shields or stiffeners.

- Type 4 Multilayer rigid and flexible printed wiring board with plated-through holes (see 6.4.2.4).

- Type 5 Bonded rigid and/or flexible printed wiring board combinations without plated-through holes (see 6.4.2.5).

- 1.2.2 Flexibility class. The flexibility class is identified by a single letter, A or B, designating the printed wiring board class.

- Class A Capable of withstanding flexing during installation.

- Class B Capable of withstanding continuous flexing for the number of cycles specified (see 3.1.1).

Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Defense Supply Center, Columbus, ATTN: DSCC/VAC, P.O. Box 3990, Columbus, OH 43216-5000 by using the Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.

AMSC N/A FSC 5998

- 1.2.3 <u>Flexible base material</u>. The printed wiring board flexible base material type should be identified by the base material designators of the applicable flexible base material specification as required by the master drawing (see 3.1.1).

- 1.2.4 <u>Rigid base material type (designs with stiffeners)</u>. The printed wiring board rigid base material type should be identified by the base material designators of the applicable base material specification as required by the master drawing (see 3.1.1).

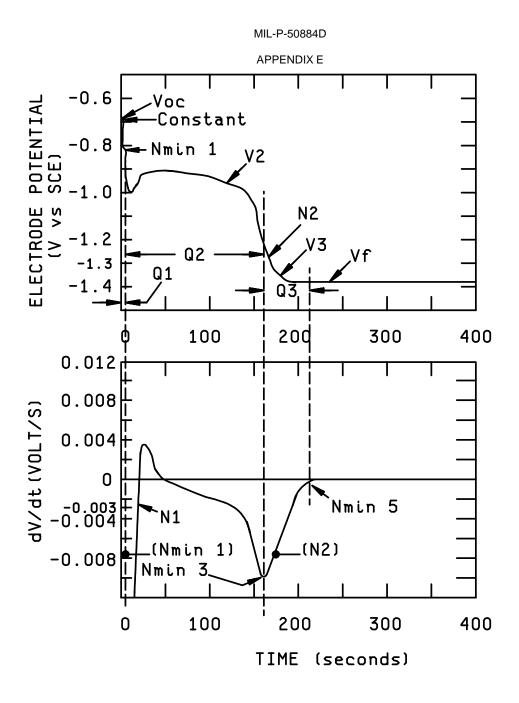

- 1.3 <u>Description of this specification</u>. The main body contains general provisions and is supplemented by detailed appendices. Appendices A and B describe the two product assurance programs that can be implemented by the manufacturer. Appendix A contains the traditional QPL product assurance program. Appendix B is an optional quality management approach using a technical review board concept addressed in MIL-PRF-31032, to modify the generic verification criteria provided in this specification. Appendix C provides statistical sampling, and basic test and inspection procedures. Appendix D is optional and can be used when producing printed wiring boards designed to superseded design standards (see 6.4.1 and A.6.7.2). Appendix D may also be used as a guide in developing a test plan for legacy or existing designs based on the tests and inspections of appendix A. Appendix E is optional and describes an alternative procedure used to evaluate oxidation levels on solderable surfaces. The procedure involves using electrochemical reduction techniques to determine the type and quantity of oxide on plated-through holes.

## 2. APPLICABLE DOCUMENTS

- 2.1 <u>General</u>. The documents listed in this section are specified in sections 3 and 4 of this specification. This section does not include documents cited in other sections of this specification or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirement documents cited in sections 3 and 4 of this specification, whether or not they are listed.

- 2.2 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DoD adopted are those listed in the issue of the DoDISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DoDISS are the issues of the documents cited in the solicitation (see 6.2).

# ASSOCIATION CONNECTING ELECTRONICS INDUSTRIES (IPC)

IPC-T-50

Terms and Definitions for Interconnecting and Packaging Electronic Circuits. (DoD adopted).

(Application for copies should be addressed to the Association Connecting Electronics Industry, 2215 Sanders Road, Suite 200 South, Northbrook, IL 60062-6135.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

- 3.1 <u>General requirements</u>. The manufacturer of printed wiring boards, in compliance with this specification, shall use or have access to production and verification facilities adequate to assure successful compliance with the provisions of this specification and the associated master drawing. Only printed wiring boards which are verified and meet all the applicable performance requirements and the design, construction, and material requirement of the associated master drawing shall be certified as compliant and delivered.

- 3.1.1 <u>Master drawing</u>. Printed wiring boards delivered under this specification shall be of the material, design, and construction specified on the applicable master drawing.

- 3.1.2 <u>Conflicting requirements</u>. In the event of conflict between the requirements of this specification and other requirements of the applicable master drawing, the precedence in which documents shall govern, in descending order, is as follows:

- a. The applicable master drawing (see 3.1.1). Additional acquisition requirements (see 6.2) may be provided in the order or contract. Any deletion of any of the performance requirements or performance verifications of this specification not approved by the qualifying activity, will result in the printed wiring board being deemed noncompliant with this specification.

- This specification.

- c. The applicable design standard (see 3.1.1, A.3.3.3 as applicable).

- d. Specifications, standards, and other documents referenced in section 2.

- 3.1.3 <u>Terms and definitions</u>. The definitions for all terms used herein shall be as specified in IPC-T-50 and those contained herein (see 6.4, and appendices A, B, C, D, and E).

- 3.2 <u>Qualification</u>. Printed wiring boards furnished under this specification shall be products that are authorized by the qualifying activity for listing on the applicable QPL at the time of award of contract (see A.4.5 and 6.3). In addition, the manufacturer shall certify (for Qualified Products List (QPL)) or receive certification from the qualifying activity (for QPL/Qualified Manufacturer's List (QML)) that the product assurance requirements of 3.3 have been met and are being maintained.

- 3.2.1 QPL. The qualification requirements for the QPL product assurance level shall be in accordance with appendix A.

- 3.2.2 QPL/QML. The qualification requirements for the QPL/QML product assurance level shall be in accordance with appendix B.

- 3.3 <u>Product assurance requirements.</u> This document contains two different methods of product assurance for printed wiring board compliance. The two levels of printed wiring product assurance are QPL (see 3.3.1) and QPL/QML (see 3.3.2) as defined below.

- 3.3.1 QPL product assurance. Product assurance procedures (see A.4.5.5.2) shall be made available to the qualifying activity no later than 6 months after the date of this specification in order for the manufacturer to be retained on QPL No. 50884. The product assurance procedures shall, as a minimum, consist of the items outlined in A.4.5.5.2.

- 3.3.2 QPL/QML product assurance. A product assurance program for QPL/QML printed wiring board furnished under this specification shall satisfy the requirements of appendix B.

- 3.4 <u>Letters of interpretation and policy</u>. Letters of interpretation and policy applicable to this document shall be approved in writing by the preparing activity. All letters of interpretation and policy applicable to MIL-P-50884 written prior to the current date of this document are not applicable to this revision. All subsequent letters of interpretation and policy letters are valid only until the next document change action (amendment or revision).

- 3.5 <u>Recycled, recovered, or environmentally preferable materials</u>. Recycled, recovered, or environmentally preferable materials should be used to the maximum extent possible provided that the material meets or exceeds the operational and maintenance requirements, and promotes economically advantageous life cycle costs.

- 3.6 <u>Workmanship</u>. Printed wiring boards shall be processed in such a manner as to be uniform in quality and shall be free from other defects that will affect life, serviceability, or appearance.

- 4. VERIFICATION

- 4.1 Classification of inspections. The inspection requirements specified herein are classified as follows:

- a. Qualification inspection (see A.4.5 or B.4.1).

- b. Inspection of product for delivery (see A.4.6 or B.4.3a).

- c. Periodic conformance inspection (see A.4.7 or B.4.3b).

- 4.2 Printed wiring board performance verification.

- 4.2.1 QPL. Printed wiring board performance verification inspection shall consist of inspections on the production printed wiring boards and the quality conformance test circuitry or test coupons referenced in appendix A.

- 4.2.2 QPL/QML. The minimum requirements for printed wiring board performance verification to the QPL/QML product assurance level shall satisfy the guidelines of appendix B.

- 4.3 <u>Qualification inspection</u>. Qualification is possible by two different methods based on the product assurance level used, QPL (see 4.3.1) or QPL/QML (see 4.3.2).

- 4.3.1 QPL. Qualification inspection for the QPL product assurance level shall be performed at a laboratory acceptable to the Government (hereafter referred to as a "certified suitable laboratory" see 6.3) on qualification test specimens produced with material, equipment, and procedures that will be used in subsequent production. The requirements concerning the qualification test specimens, number of specimens to be tested, and the test routines they shall be subjected to, and the extent of qualification shall be as specified in appendix A.

- 4.3.2 QPL/QML product assurance level shall be as specified in appendix B.

## 5. PACKAGING

5.1 <u>Packaging</u>. For acquisition purposes, the packaging requirements shall be as specified in the contract or order (see 6.2). When actual packaging of materiel is to be performed by DoD personnel, these personnel need to contact the responsible packaging activity to ascertain requisite packaging requirements. Packaging requirements are maintained by the Inventory Control Point's packaging activity within the Military Department or Defense Agency, or within the Military Department's System Command. Packaging data retrieval is available from the managing Military Department's or Defense Agency's automated packaging files, CD-ROM products, or by contacting the responsible packaging activity.

#### 6. NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

- 6.1 <u>Intended use</u>. Flexible and rigid-flex printed wiring boards are intended primarily for use in electronic and electrical equipment to eliminate high density hand wiring, where space is limited and where compact packaging is desirable.

- 6.2 Acquisition requirements. Acquisition documents must specify the following:

- a. Title, number, revision letter (with any amendment number when applicable), and date of this specification.

- b. Issue of DoDISS to be cited in the solicitation, and if required, the specific issue of individual documents referenced (see 2.2).

- c. Packaging requirements (see 5.1).

- d. Appropriate type (see 1.2.1) and flexibility class (see 1.2.2).

- e. Title, number, revision letter (with any engineering change proposal or notice of revision number when applicable), and date of the applicable master drawing (see 3.1.1).

- 6.3 Qualification. With respect to products requiring qualification, awards will be made only for products which are, at the time of award of contract, qualified for inclusion in Qualified Products List (QPL) No. 50884 whether or not such products have actually been so listed by that date. The attention of the contractors is called to these requirements, and manufacturers are urged to arrange to have the products that they propose to offer to the Federal Government tested for qualification in order that they may be eligible to be awarded contracts or orders for the products covered by this specification. Information pertaining to qualification of products may be obtained from Defense Supply Center, Columbus, ATTN: DSCC-VQE, P.O. Box 3990, Columbus, Ohio 43216-5000. Application procedures should conform to the guidelines of SD-6, "Provisions Governing Qualification" (see 6.3.3).

- 6.3.1 <u>Transference of qualification</u>. Manufacturers currently qualified to MIL-P-50884C will have their qualification transferred to this document. The expiration date of their current qualification will not be changed. Qualifications in process (before the date of this document) will be performed to the requirements MIL-P-50884C with Amendment 5. New applications for qualification (after the date of this document) must be performed to the requirements of this revision.

- 6.3.2 <u>Retention of qualification</u>. Printed wiring boards verified and certified to MIL-P-50884C (with any amendment) or to any product assurance level contained herein will retain qualification to this document.

- 6.3.2.1 <u>Discussion</u>. MIL-P-50884C (unamended) certification program was not governed by the policies and procedures of the Defense Standardization Program as defined by DoD 4120.3-M and therefore does not exist within the QPL program of MIL-P-50884C with Amendment 1 and beyond. For additional information concerning this issue, see MIL-P-50884C, paragraph 60.1.

- 6.3.3 <u>"Provisions Governing Qualification"</u>. Copies of SD-6, "Provisions Governing Qualification", may be obtained upon application to Document Automation and Production Services (DAPS), Building 4D (DPM-DODSSP), 700 Robbins Avenue, Philadelphia, PA 19111-5094.

## 6.4 Terms and definitions.

- 6.4.1 <u>Design standard</u>. A document that establishes the baseline parameters (default values), standard practices and guidelines for the design of printed wiring boards. Within this document, the term "design standard" is used to describe those documents that contains the design, construction, material, and test coupon requirements and guidelines used to produce panels of flexible printed wiring boards.

- 6.4.2 Printed wiring board types. The printed wiring board types should be as specified in IPC-2223 or MIL-STD-2118.

- 6.4.2.1 <u>Type 1</u>. Type 1 flexible printed wiring boards have only one conductive layer (single sided conductor pattern) with cover lay and no plating in the component holes. In addition, the design may contain shields or stiffeners. Type 1 flexible printed wiring boards are usually designed for class B (continuous flex) applications.

- 6.4.2.2 <u>Type 2</u>. Type 2 flexible printed wiring boards are printed wiring boards with conductor patterns on both sides of the printed board (double sided). In addition, the design of the printed wiring board may require the following: (1) that the holes through the base material be plated through to connect the conductor patterns on both sides together, (2) with or without shields, and (3) with or without stiffeners. Type 2 flexible printed wiring boards are usually designed for class B (continuous flex) applications.

- 6.4.2.3 <u>Type 3</u>. Type 3 flexible printed wiring boards are multilayered (with 3 or more conductor layers) with plated-through holes. Type 3 printed wiring boards are usually designed for class A (flex to install) applications.

- 6.4.2.4 <u>Type 4</u>. Type 4 flex-rigid printed wiring boards are multilayered boards containing plated-through holes with rigid sections connected by flexible sections. Type 4 printed wiring boards are usually only designed to be used in class A (flex to install) applications.

- 6.4.2.5 <u>Type 5</u>. Type 5 printed wiring boards are multilayer bonded rigid and/or flexible printed wiring board combinations without plated-through holes.

- 6.4.3 <u>Product assurance</u>. The method of complying with the two different levels of this document using either the QPL method (that has been internal to this document since MIL-P-50884C, amendment 1) or the new method QPL/QML (introduced by this revision).

- 6.4.3.1 QML. A list of manufacturers, by name and plant address, who have met the certification and qualification requirements stated in MIL-PRF-31032. A QML focuses on qualifying an envelope of materials and processes rather than individual products or designs. That envelope is qualified by carefully selecting representative worst case test vehicles or representative samples from production that contain all potential combinations of materials and processes that may be subsequently used during production. A QML is normally appropriate for items of supply that have very rapid technological advancement or a myriad of variations or custom designs that make individual product qualifications impractical or excessively expensive.

- 6.4.3.2 QPL. A QPL focuses on qualifying individual products or families of products. A QPL will normally be appropriate for items of supply that are stable and will be continually available for extended period of time.

- 6.4.3.3 QPL/QML. A transitional program that allows a manufacturer that is certified and qualified to the QML program of MIL-PRF-31032 to fabricate, test, and supply products to this revision of this document.

- 6.5 <u>Compliant printed wiring boards</u>. For a printed wiring board to be compliant with this document, it must be produced by a manufacturer qualified for listing on QPL No. 50884 or reciprocal listing as described in appendix B, and must be obtained from a lot which was subjected to and passed all inspection of product for delivery verifications using the applicable product assurance program.

- 6.6 Supersession.

- 6.6.1 Superseded types and classes. Superseded types and classes are listed below:

- a. Type A of MIL-P-50884B (the ability to withstand only one solder operation without degradation) was not superseded and therefore does not apply or exist in newer revisions.

- b. Type B of MIL-P-50884B (the ability to withstand five solder and unsoldering operation without degradation) was superseded by all printed wiring board types of MIL-P-50884C and beyond.

- Class 1 of MIL-P-50884B was superseded by types 1, 2 and 5 of MIL-P-50884C and beyond.

- Class 2 of MIL-P-50884B was superseded by types 3 and 4 of MIL-P-50884C and beyond.

- 6.6.2 <u>Design, construction and verification</u>. Design, construction, and verification supersession information is included in appendix D of this document.

- 6.6.3 <u>Reference to superseded specifications</u>. All the requirements of this document can be interchangeable with those documents identified as MIL-P-50884. Therefore, existing documents (master drawings or OEM documents) referencing MIL-P-50884 need not be revised, updated, or changed to make reference to MIL-P-50884 in order for this document to be used.

- 6.6.4 <u>Diagrams and figures</u>. Most diagrams and figures that were in previous revisions of MIL-P-50884 have been eliminated from this document. See appendix A for guidance concerning diagrams and figures.

- 6.7 <u>Design standards</u>. This document contains requirements and guidelines for the testing of printed wiring boards that were designed to and or make use of test coupons conforming to IPC-2221. See appendix D for additional guidance regarding the verification of panels using different design standards.

- 6.8 Subject term (key word) listing.

Design standard Master drawing Qualified Manufacturer List (QML) Qualified Product List (QPL) Test coupon Verification Conformance Inspection

6.9 <u>Changes from previous issue</u>. Marginal notations are not used in this revision to identify changes with respect to the previous issue due to the extensiveness of the changes.

# APPENDIX A

# PRODUCT ASSURANCE (QUALIFICATION AND VERIFICATION) REQUIREMENTS FOR QUALIFIED PRODUCTS LIST (QPL) PROGRAMS

#### A.1. SCOPE

A.1.1 <u>Scope</u>. This appendix contains the requirements and procedures for manufacturers using the traditional QPL method of product assurance (qualification and verification inspection) for printed wiring boards covered by this specification. The process for extending and retaining qualification is also herein. This appendix is a mandatory part of this specification for non-QML manufacturers and the information contained herein is intended for compliance only.

## A.2. APPLICABLE DOCUMENTS

- A.2.1 <u>General</u>. The documents listed in this section are specified in sections 3 and 4 of this specification. This section does not include documents cited in other sections of this specification or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirement documents cited in sections 3 and 4 of this specification, whether or not they are listed.

- A.2.1.1 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DoD adopted are those listed in the issue of the DoDISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DoDISS are the issues of the documents cited in the solicitation (see A.6.2).

## ASSOCIATION CONNECTING ELECTRONICS INDUSTRIES (IPC)

| J-STD-003  | - | Solderability Tests for Printed Boards.                                                          |

|------------|---|--------------------------------------------------------------------------------------------------|

| IPC-2221   | - | Printed Board Design, Generic Standard for.                                                      |

| IPC-2223   | - | Flexible Printed Boards, Sectional Design Standard for.                                          |

| IPC-A-600  | - | Acceptability of Printed Boards.                                                                 |

| IPC-TM-650 | - | Test Methods Manual.                                                                             |

| IPC-100041 | - | Master Drawing for Single Sided Printed Boards.                                                  |

| IPC-100042 | - | Master Drawing for Double Sided Printed Boards.                                                  |

| IPC-100043 | - | Master Drawing for 10 Layer Multilayer Printed Boards.                                           |

| IPC-100044 | - | Master Drawing for 4 Layer Multilayer Printed Boards.                                            |

| IPC-100101 | - | Capability Test Board (Single Sided), Master Drawing.                                            |

| IPC-100102 | - | Capability Test Board (Double Sided), Master Drawing.                                            |

| IPC-100103 | - | Capability Test Board (Ten Layer Multilayer Board without Blind or Buried Vias), Master Drawing. |

(Application for copies should be addressed to the Association Connecting Electronics Industries (IPC), 2215 Sanders Road, Suite 200 South, Northbrook, IL 60062-6135.)

# NATIONAL CONFERENCE OF STANDARDS LABORATORIES

NCSL Z540 - General Requirements for Calibration Laboratories and Measuring and Test Equipment.

(Application for copies should be addressed to the National Conference of Standards Laboratories, 1800 30th Street, Suite 305B, Boulder, CO 80301-1032.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

#### APPENDIX A

A.2.2 Order of precedence. In the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### A.3 REQUIREMENTS

- A.3.1 <u>General</u>. The performance requirements contained in this section, although sometimes determined by examination of sampled printed wiring boards or test coupons, apply to all deliverable printed wiring boards.

- A.3.1.1 <u>Master drawing (see A.6.2.1d)</u>. Printed wiring boards delivered under this specification shall be of the material, design, and construction specified on the applicable master drawing. For the purposes of this appendix, when the term "specified" is used without additional reference to a specific location or document, the intended reference shall be to the applicable master drawing. If individual design details are not specified on the applicable master drawing, then the baseline design parameters shall be as detailed in the design standard that was used to design the printed wiring board (see A.3.3).

- A.3.2 <u>Qualification</u>. Printed wiring boards furnished under this specification shall be products that are authorized by the qualifying activity for listing on the applicable QPL at the time of award of contract (see A.4.5 and A.6.3). In addition, the manufacturer shall certify that the product assurance requirements of A.4.5.5.2 have been met and are being maintained.

- A.3.3 <u>Design (see A.6.2.1e)</u>. Printed wiring boards shall be of the design as specified. Unless otherwise specified (see A.3.1.1), if individual design details are not specified on the applicable master drawing, then the baseline design parameters to be use for acceptability of finished product requirements shall be as detailed in the design standard that was used to design the printed wiring board. If no design standard is specified on the master drawing or the appropriate design standard cannot be determined, then the default design shall be performance class 3 of IPC-2221 and IPC-2223.

- A.3.3.2 <u>Test coupons</u>. Test coupon design, quantity, placement, and usage shall be in accordance with IPC-2221 and IPC-2223. NOTE: Test coupons shall be as specified in the applicable design standard and shall reflect worst case design conditions of the printed board(s) they represent.

- A.3.4 <u>Material</u>. The printed wiring boards shall be constructed of material as specified (see A.3.1.1). When a definite material is not specified (see A.3.1.1), a material shall be used that will enable the printed wiring board to meet the performance requirements of this specification. Acceptance or approval of any material shall not be construed as a guaranty of the acceptance of the finished printed wiring board.

- A.3.5 <u>Visual and dimensional requirements</u>. The finished printed wiring board shall meet the dimensional (such as cutouts, overall thickness, periphery, etc.) requirements specified (see A.3.1.1) and in A.3.5.1 through A.3.5.9. IPC-A-600 contains figures and illustrations that can be useful in visualizing the accept/reject requirements listed below.

- A.3.5.1 Base materials (flexible and rigid).

- A.3.5.1.1 <u>Edges of flexible sections</u>. Defects such as burrs, nicks, tears, or delamination, along the trimmed edges of flexible sections of printed wiring boards shall be acceptable provided the penetration does not reduce the edge spacing by more than 50 percent of the edge spacing specified (see A.3.1.1). Discoloration or resin recession along the trimmed edges of the flexible sections following the surface solderability test is acceptable providing the discoloration or resin recession dimension does not exceed the thickness of the adhesive material in the bonding area (when applicable) or reduce the edge spacing below the requirements of the master drawing.

- A.3.5.1.2 Edges of rigid sections (types 4 and 5). Defects such as burrs, nicks, and haloing along the edges of rigid sections of printed wiring boards shall be acceptable provided the penetration does not reduce the edge spacing by more than .10 inch (0.25 mm) or 50 percent of the edge spacing specified (see A.3.1.1), whichever is less.

- A.3.5.1.3 <u>Surface imperfections</u>. Surface imperfections (such as scratches, pits, dents, and weave texture) shall be acceptable providing the imperfection meets the following:

- a. The base material reinforcement material (woven or non-woven fiber) is not cut, disturbed, or exposed.

- b. The imperfection does not bridge between conductors (weave texture may bridge conductors).

- The dielectric spacing between the imperfection and conductors does not reduce conductor spacing below the specified minimum requirements (see A.3.1.1).

- A.3.5.1.4 <u>Subsurface imperfections</u>. Subsurface imperfections (such as blistering, haloing, and delamination) shall be acceptable providing the imperfection meets the following:

- a. The imperfection is translucent.

- b. The imperfection does not bridge more than 25 percent of the distance between conductors or plated-through holes. No more than two percent of the printed wiring board area on each side shall be affected.

- The imperfection does not reduce conductor spacing between adjacent conductors below the minimum requirements specified (see A.3.1.1).

- The imperfection does not propagate as a result of testing (such as rework simulation, thermal stress, or thermal shock).

- A.3.5.1.4.1 Foreign inclusions. Foreign inclusions shall be permitted when they meet the following:

- a. The inclusion is trapped within the flexible portion of the printed board.

- b. The inclusion is located at least .010 inch (0.25 mm) from the nearest conductor.

- c. The inclusion does not reduce the spacing between conductors below the minimum conductor spacing specified (see A.3.1.1).

- d. The inclusions longest dimension is no greater than .032 inch (0.81 mm) in circuitry areas. Inclusions in non-circuitry areas have no maximum dimension requirement.

#### APPENDIX A

- A.3.5.1.4.2 <u>Subsurface spots</u>. Subsurface spots shall be permitted when they meet any of the following:

- a. The spots are translucent.

- b. The spots are known to be weave texture other than delamination or disbonding.

- c. The spots are isolated white spots that are at least .010 inch (0.25 mm) from the nearest conductor or that do not propagate as a result of any soldering operation (gelation particles are acceptable regardless of location).

- A.3.5.1.4.3 <u>Adhesive voids (for metal clad flexible base materials only)</u>. Adhesive voids that are no greater than .020 inch (0.51 mm) or 25 percent of spacing shall be acceptable.

### A.3.5.2 Conductor pattern.

- A.3.5.2.1 <u>Annular ring, external</u>. The minimum external annular ring shall be as specified (see A.3.1.1). If not specified, the minimum external annular ring shall be .002 inch (0.051 mm) for plated through holes and .006 inch (0.152 mm) for unsupported holes. Unless otherwise specified, the external annular ring may have, in isolated areas, a 20 percent reduction of the minimum external annular ring specified (see A.3.1.1), due to defects such as pits, dents, nicks, pinholes and extruded adhesive onto the land. Unless otherwise specified, plated holes identified as vias can have a maximum of 90 degrees of hole breakout if the breakout does not occur at the conductor to land intersection.

- A.3.5.2.2 <u>Conductor spacing</u>. The conductor spacing shall be as specified (see A.3.1.1). The minimum edge spacing (the spacing between the edge of the printed wiring board and conductors) shall be as specified (see A.3.1.1).

- A.3.5.2.3 Conductor width. The conductor width(s) shall be as specified (see A.3.1.1).

- A.3.5.2.3.1 <u>Conductor pattern imperfections</u>. The conductor pattern shall contain no cracks, splits or tears. Unless otherwise specified (see A.3.1.1), any combination of edge roughness, nicks, pinholes, cuts or scratches exposing the base material shall not reduce each conductor width more than 20 percent of its minimum specified width. There shall be no occurrence of the 20 percent reductions greater than .50 inch (12.70 mm) or 10 percent of a conductor length, whichever is less.

- A.3.5.2.4 <u>Conductor finish coverage</u>. The conductor finish plating or coating shall completely cover the basis metal of the conductive pattern. Complete conductor coverage by solder does not apply to the vertical conductor edges. There shall be no evidence of any lifting or separation of conductor finish plating or coating from the surface of the conductive pattern. There shall be no whiskers of solder or plating on the surface of the conductive pattern. For designs using solder resist over bare conductors, it shall be acceptable to have up to .010 inch (0.25 mm) of exposed base metal at the interface between the solder resist and the basis metal conductor finish. For design requiring unfused tin-lead plating as a final conductor finish coverage, the thickness shall be as specified (see A.3.1.1 and A.3.3).

## A.3.5.3 Cover lay.

A.3.5.3.1 <u>Access hole registration</u>. The cover lay registration shall be such that the size or diameter of the access hole shall not reduce the component land area or minimum annular ring below the limits specified (see A.3.5.2.1). In addition, access hole misregistration shall not expose adjacent isolated lands or conductors.

- A.3.5.3.2 <u>Delamination</u>. There shall be no cover lay delamination along the outer edges of the cover lay (see A.3.5.1.1). Cover lay delamination shall be acceptable providing the following conditions are met:

- a. At random locations away from conductors if each delamination is no larger than .01 square inch (6.45 square mm) and is not within .040 inch (1.0 mm) of the printed wiring board edge or access hole edge. The total number of the above delaminations shall not exceed three in any 1 square inch (645 square mm) of cover lay surface area.

- b. Along conductor edges, the total delamination does not exceed either .02 inch (0.51 mm) in width or 20 percent of the spacing between adjacent conductors, whichever is smaller.

- A.3.5.3.3 <u>Wrinkles or creases</u>. Wrinkles or creases in the cover lay shall be acceptable provided the requirements of A.3.5.3.2 are met.

- A.3.5.3.3.1 <u>Class B only</u>. After exposure to the flexibility endurance test (see A.3.7.4.3 and A.4.8.4.3), there shall be no propagation of any cover lay separation or delamination in the continuous flex area for class B designs.

- A.3.5.4 <u>Hole pattern accuracy</u>. The accuracy of the hole pattern (size and location) on the printed wiring board shall be as specified (see A.3.1.1).

- A.3.5.5 <u>Lifted lands</u>. There shall be no lifted lands on the deliverable printed wiring board.

- A.3.5.6 <u>Registration, external (method I)</u>. Misregistration shall not reduce the minimum external annular ring below its specified limits (see A.3.1.1).

- A.3.5.7 Solder resist (when applicable). Unless otherwise specified, the solder resist conditions below shall apply.

- A.3.5.7.1 <u>Coverage</u>. Solder resist coverage imperfections (such as blisters, skips, and voids) shall be acceptable providing the imperfection meets all of the following:

- a. The solder resist imperfection shall not expose two adjacent conductors whose spacing is less than the electrical spacing required for the voltage range and environmental condition specified in the applicable design standard.

- b. In areas containing parallel conductors, the solder resist imperfection shall not expose two isolated conductors whose spacing is less than 0.5 mm (.020 inch) unless one of the conductors is a test point or other feature area which is purposely left uncoated for subsequent operations.

- c. The exposed conductor shall not be bare copper.

- d. The solder resist imperfection does not expose tented via holes.

- A.3.5.7.2 <u>Discoloration</u>. Discoloration of metallic surfaces under the cured solder resist is acceptable.

- A.3.5.7.3 <u>Registration</u>. The solder resist shall be registered to the land or terminal patterns in such a manner as to meet the requirements specified (see A.3.1.1). If no requirements are specified, the following apply:

- a. Unless otherwise specified, solder resist shall not encroach onto surface mount lands.

- b. Solder resist misregistration onto plated-through component hole lands (plated-through holes to which solder connections are to be made) shall not reduce the external annular ring below the specified minimum requirements.

- c. Solder resist shall not encroach into plated-through hole barrels or onto other surface features (such as connector fingers or lands of unplated holes) to which solder connections will be made.

- d. Solder resist is permitted in plated-through vias or holes in which no lead is to be soldered.

- Test points which are intended for assembly testing shall be free of solder resist unless a partial coverage allowance is specified.

- A.3.5.7.4 Thickness. The solder resist thickness shall be as specified (see A.3.1.1).

- A.3.5.8 <u>Stiffener</u>. Complete bonding of the stiffener to the flexible portion of the printed wiring board is not required (see A.6.9).

- A.3.5.8.1 <u>Stiffener access hole registration</u>. Stiffener access hole registration shall be such that the size or diameter of the access hole shall not reduce the component land area or minimum annular ring below the limits specified (see A.3.5.2.1).

- A.3.5.9 <u>Wicking</u>. Wicking of plating or solder extending .010 inch (0.25 mm) into the base material shall be acceptable provided it does not reduce the conductor spacing below the minimum clearance spacing requirements specified (see A.3.1.1).

- A.3.6 <u>Plated-through hole requirements</u>. When examined by microsection, the test specimen shall meet the requirements of A.3.6.1 through A.3.6.14. IPC-A-600 contains figures and illustrations that can aid in the visualization of the accept/reject conditions of microsectioned test specimens.

- A.3.6.1 <u>Annular ring, internal</u>. The minimum annular ring for functional internal lands on types 3 and 4 printed wiring boards shall be as specified (see A.3.1.1). If not specified on the master drawing, the minimum internal annular ring shall not be less than .002 inch (0.051 mm).

- A.3.6.2 <u>Conductor thickness</u>. The conductor thickness shall be as specified (see A.3.1.1). When a copper foil weight requirement is specified, a reduction in thickness up to 10 percent below the minimum allowable foil thickness specified by the applicable material specification shall be considered acceptable in order to accommodate a processing allowance for cleaning either by chemical or mechanical means.

- A.3.6.3 <u>Dielectric layer thickness</u>. The minimum dielectric thickness separating the conductor layers of the printed wiring boards shall be as specified (see A.3.1.1). If not specified on the master drawing, the minimum dielectric spacing for rigid base materials shall be .0035 inch (0.089 mm) and for flexible base materials .0015 inch (0.038 mm).

- A.3.6.3.1 <u>Thermal planes</u>. The minimum lateral spacing between adjacent conductive surfaces (nonfunctional pads) or plated-through hole and the thermal plane shall be as specified (see A.3.1.1). Radial cracks, wicking or voids in the hole-fill insulation material shall not reduce by 75 percent the specified lateral spacing between adjacent conductive surfaces.

- A.3.6.3.2 <u>Cover lay thickness</u>. Unless otherwise specified (see A.3.1.1), the thickness of the cover lay shall not be measured.

- A.3.6.4 Delamination. Printed wiring boards shall have no delaminations in excess of that allowed in A.3.5.1.4.

- A.3.6.5 Etchback or smear removal.

- A.3.6.5.1 <u>Etchback (when specified, see A.3.1.1)</u>. When specified (see A.3.1.1), printed wiring boards shall be etched back for the lateral removal of resin and reinforcement material (woven glass or other media) from the internal conductors prior to plating. The etchback shall be effective on at least the top or bottom (horizontal) surface of each internal conductor. Negative etchback is not acceptable when etchback is specified (see A.3.1.1).

- A.3.6.5.1.1 <u>Etchback limits</u>. Unless otherwise specified (see A.3.1.1), etchback shall not exceed .003 inch (0.08 mm) or be less than .0001 inch (0.0025 mm) with .0005 inch (.013 mm) being a preferred depth when measured at the internal copper contact area protrusion.

- A.3.6.5.2 <u>Smear removal (hole cleaning)</u>. When etchback is not specified (see A.3.1.1), the vertical faces of the internal conductors of the plated-through hole shall be cleaned to be free of resin smear. Lateral removal of base material from the hole wall shall not exceed .001 inch (0.03 mm). When etchback is not specified (see A.3.1.1), a negative etchback of .0005 inch (0.013 mm) maximum shall be acceptable.

- A.3.6.6 Base material voids.

- A.3.6.6.1 <u>As received condition of rigid base materials</u>. Laminate voids with the longest dimension of .003 inch (0.08 mm) or less shall be acceptable.

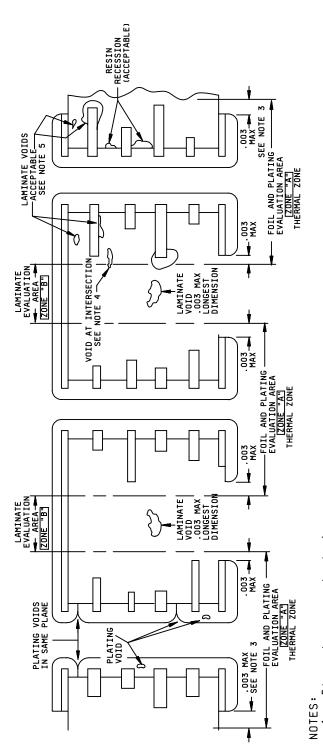

- A.3.6.6.2 <u>After rework simulation, thermal shock or thermal stress testing (see figure 1)</u>. Laminate voids are not evaluated in zone A. Laminate voids in zone B with the longest dimension of .003 inch (0.08 mm) or less shall be acceptable provided the conductor spacing is not reduced below the minimum dielectric spacing requirements, laterally or vertically, as specified (see A.3.1.1).

- A.3.6.6.3 <u>Adhesive voids (for metal clad flexible base materials only)</u>. Adhesive voids that are no greater than .020 inch (0.51 mm) shall be acceptable. Multiple adhesive voids in the same plane between adjacent plated holes shall not have a combined length which exceeds .003 inch (0.08 mm).

# APPENDIX A

Dimensions are in inches.

4 2 2 4 . . . .

Laminate voids greater than .003 (0.08 mm)

Laminate voids greater than .003 (0.08 mm) Metric equivalents are given for general information only. Typically beyond land edge most radially extended. Void at intersection of zone A and zone B. Laminate voids that extend into zone B are rejectable. Laminate voids are not evaluated in zone A. Laminate voids that extend into zone B are rejectable.

Typical plated-through hole cross section after thermal stress or rework simulation. FIGURE 1.

## APPENDIX A

## A.3.6.7 Lifted lands.

- A.3.6.7.1 <u>As received condition</u>. There shall be no lifted lands on the as received specimen. When inspected in accordance with A.4.8.2 and lifted lands are present, the lot shall be 100 percent visually inspected in accordance with A.4.8.1 for separation of the lands from the base material.

- A.3.6.7.2 <u>After rework simulation, thermal stress or thermal shock testing</u>. After undergoing rework simulation, thermal stress or thermal shock testing (see A.3.7.4.6, A.3.7.4.10, and A.3.7.6.2), the maximum allowed distance from the base material surface to the bottom of the edge of the land or pad shall be no greater than the total land thickness. The total land thickness is equal to the combined thickness of the metal foil and copper plating on that land.

## A.3.6.8 Plating and coating properties.

A.3.6.8.1 <u>Conductor finish thickness (when applicable)</u>. Unless otherwise specified on the master drawing (see A.3.1.1), the conductor finish plating or coating thickness shall be as specified in Table I. (Also see A.3.5.2.4).

Table I. Conductor plating and finish thickness.

| Material                                                                | Thickness                                 |

|-------------------------------------------------------------------------|-------------------------------------------|

| Copper (in holes, blind vias, surface)                                  | .001 (0.025 mm)                           |

| Copper (buried vias)                                                    | .0006 (0.015 mm)                          |

|                                                                         |                                           |

| Gold (for edge board connectors and areas not to be soldered) (Minimum) | .00003 (0.0008 mm)                        |

| Gold (on areas to be soldered) (Maximum)                                | .000006 (0.00015 mm)                      |

| Gold (on areas to be wire bonded, ultrasonic) (Minimum)                 | .00006 (0.0015 mm)                        |

| Gold (on areas to be wire bonded, thermosonic) (Minimum)                | .00003 (0.0008 mm)                        |

| Immersion gold                                                          | .000003 to .000009 (0.0008 to 0.00023 mm) |

|                                                                         |                                           |

| Nickel (for edgeboard connectors) (Minimum)                             | .0001 (0.0025 mm)                         |

| Nickel (barrier to prevent formation of copper-tin compounds) (Minimum) | .0002 (0.005 mm)                          |

| Nickel, electroless                                                     | .0001 to .0002 (0.0025 to 0.005 mm)       |

| Organic Solderabilty Preservative                                       | Solderable                                |

| Tin-lead, fused or solder coat                                          | Coverage and solderable                   |

| Tin-lead, unfused                                                       | .0003 (0.008 mm)                          |

| Solder coat over base copper                                            | Coverage and solderable                   |

A.3.6.8.2 <u>Copper plating thickness (when applicable)</u>. Copper plating thickness (on the surface, in plated-through holes or blind/buried vias) shall be as specified (see A.3.1.1). Unless otherwise specified (see A.3.1.1), a 20 percent reduction of the specified copper plating thickness shall be acceptable. Any 20 percent thickness reduction shall be non-continuous (isolated; not more than 10 percent of the composite board thickness). Any copper plating less than 80 percent of the specified thickness shall be treated as a void.

- A.3.6.8.2.1 <u>Copper plating voids</u>. The copper plating in the plated-through holes shall not exhibit any void in excess of the following:

- a. There shall be no more than one plating void per panel, regardless of length or size.

- b. There shall be no plating void in excess of 5 percent of the total printed wiring board thickness.

- c. There shall be no plating voids evident at the interface of an internal conductive layer and plated hole wall.

- A.3.6.8.2.2 <u>Plating separations (see A.6.4.3)</u>. Except for along the vertical edge of the external copper foil, there shall be no separations or contamination between the hole wall conductive interfaces. Conductive interface separations along the vertical edge of the external copper foil shall be acceptable.

- A.3.6.9 <u>Hole wall deficiencies</u>. Nodules, plating folds, or plated glass fibers that project into the copper plating shall be acceptable provided that the hole diameter and the hole wall copper thickness are not reduced below their specified limits (see A.3.1.1).

- A.3.6.10 <u>Metallic cracks</u>. There shall be no cracks in the internal layer conductive foils, platings, or coatings. Cracks in outer layer metal foil shall be acceptable if they do not propagate into the plated copper. Cracks shall not be acceptable in the copper plating.

- A.3.6.11 Nail-heading. Nail-heading of conductors shall not exceed 1.5 times the copper foil thickness.

- A.3.6.12 Resin recession.

- A.3.6.12.1 <u>As received condition</u>. Resin recession at the outer surface of the plated-through hole barrel wall shall be permitted provided the maximum depth as measured from the barrel wall does not exceed .003 inch (0.08 mm) and the resin recession on any side of the plated-through hole does not exceed 40 percent of the cumulative base material thickness (sum of the dielectric layer thickness being evaluated) on the side of the plated-through hole being evaluated.

- A.3.6.12.2 After rework simulation, thermal shock or thermal stress testing. Resin recession at the outer surface of the plated-through hole barrel shall be permitted and is not cause for rejection.

- A.3.6.13 <u>Wicking</u>. Wicking of copper plating extending .003 inch (0.08 mm) into the base material shall be acceptable provided it does not reduce the conductor spacing below the minimum clearance spacing requirements specified (see A.3.1.1).

- A.3.6.14 <u>Undercutting</u>. Undercutting at each edge of the conductors shall not exceed the total thickness of the copper foil and plated copper.

#### APPENDIX A

- A.3.7 <u>Inspection requirements</u>. The detailed requirements contained in this section, although determined by examination of sample printed wiring boards or test coupons, apply to all deliverable printed wiring boards.

- A.3.7.1 <u>Acceptability (of printed wiring boards)</u>. When examined as specified in A.4.8.1, the printed wiring boards shall be in accordance with the acceptance requirements specified in A.3.1.1 (master drawing), A.3.4 (material), A.3.5 (visual and dimensional), A.3.8 (marking), A.3.10 (repair) and A.3.11 (workmanship), as applicable.

- A.3.7.2 <u>Acceptability (of microsectioned test specimens)</u>. When printed wiring board test specimens (finished printed wiring boards, supporting test coupons, or qualification test specimens) are microsectioned and examined as specified in A.4.8.2, the requirements specified in A.3.6 shall be met.

- A.3.7.2.1 <u>As received</u>. After meeting the requirements of A.3.8 and A.3.11 when inspected in accordance with A.4.8.1, the as received printed wiring board test specimen shall be microsectioned and inspected in accordance with A.4.8.2 and shall meet the requirements of A.3.6.

## A.3.7.2.2 Registration, internal.

- A.3.7.2.2.1 <u>By microsection (method II)</u>. Unless otherwise specified (see A.3.1.1), when inspected as specified in A.4.8.2.2, the layer-to-layer pattern misregistration shall not reduce the minimum annular ring below its specified (see A.3.1.1) limits.

- A.3.7.2.2.2 Optional internal registration by registration test coupons. Registration test coupons may have been designed into the printed wiring board by the design activity, or may be added to the panel by the manufacturer to enhance testability (see A.4.8.2.2.2 and appendix D). To be usable for acceptance purposes, registration test coupons must relate the actual grid location of each circuitry layer to all other circuitry layers and to the hole pattern accuracy required (see A.3.5.4) in each printed wiring board.

## A.3.7.3 Chemical requirements.

- A.3.7.3.1 <u>Cleanliness</u>. When printed wiring boards are tested in accordance with A.4.8.3.1, the levels of cleanliness shall be in accordance with the requirements of A.3.7.3.1.1 or A.3.7.3.1.2, as applicable.

- A.3.7.3.1.1 Prior to the application of solder resist (see A.6.5). Unless otherwise specified, prior to the application of solder resist, the level of ionic contamination shall not exceed 10.06 micrograms/square inch (1.56 micrograms/square centimeter). The sodium chloride salt equivalent ionic contamination test equipment specified in A.6.5.2 may be used in lieu of the method specified in A.4.8.3.1. When printed wiring boards are tested using the sodium chloride salt equivalent ionic contamination test equipment specified in A.6.5.2, the final value shall be less than equivalents of sodium chloride specified in table VI for the printed wiring board surface area tested.

- A.3.7.3.1.2 <u>Completed printed wiring boards (when specified, see A.3.1.1 and A.6.2.2.g)</u>. The levels of cleanliness for completed printed wiring boards shall be as specified.

- A.3.7.3.2 <u>Resistance to solvents (marking inks or paints)</u>. After marking is tested in accordance with A.4.8.3.2, any specified markings which are missing in whole or in part, faded, smeared, of shifted (dislodged) to the extent that they cannot be readily identified shall constitute failure.

#### APPENDIX A

#### A.3.7.4 Physical requirements.

- A.3.7.4.1 <u>Bow and twist (stiffener sections)</u>. When tested as specified in A.4.8.4.1, the maximum allowable bow and twist for rigid or stiffener sections of the printed wiring board shall be 0.75 percent for designs that use surface mount components and 1.5 percent for all other designs, unless otherwise specified (see A.3.1.1).

- A.3.7.4.2 Conductor edge outgrowth.

- A.3.7.4.2.1 <u>Solder covered conductors</u>. When the printed wiring board test specimen is examined as specified in A.4.8.1, there shall be no outgrowth of the solder coating on the conductor edges.

- A.3.7.4.2.2 <u>Conductors covered with metals other than solder</u>. After undergoing the test as specified in A.4.8.4.2, the printed wiring board test specimen shall be examined as specified in A.4.8.1 and the maximum permissible outgrowth on conductors shall be .001 inch (0.03 mm).

- A.3.7.4.3 <u>Flexibility endurance (class B only)</u>. When tested as specified in A.4.8.4.3, printed wiring board test specimen shall be capable of withstanding the specified conditions of A.3.7.4.3.1 or A.3.7.4.3.2, as applicable, without any evidence of damage, degradation or rejectable delamination. After the test, the requirements specified in A.3.5.3.2.1, A.3.7.5.1 and A.3.7.5.2 shall be met.

- A.3.7.4.3.1 Qualification and periodic testing. Printed wiring board test specimen shall be capable of withstanding 100,000 cycles without any evidence of damage, degradation or rejectable delamination. The following details and exceptions shall apply:

- a. The test specimens shall be in accordance with table I or V, as applicable.

- b. Number of test specimens to be tested: One.

- c. Number of flex cycles: 100,000 cycles.

- d. Mandrel size (when applicable): The mandrel size for types 1 and 2 shall be twelve times the sum of the total ply thickness reduced to the nearest .125 inch (3.18 mm). The mandrel size for types 3, 4, and 5 shall be twenty-four times the sum of the total ply thickness reduced to the nearest .125 inch (3.18 mm). The mandrel shall not be less than .125 inch (3.18 mm).

- A.3.7.4.3.2 <u>User specified (see A.3.1.1 and A.6.2.2)</u>. The number of flexing cycles, flexing rate, and points of application of the flexing, travel of loop (if other than one inch (25.4 mm) minimum), and diameter of mandrel (when applicable) shall be specified on the master drawing. If no parameters are specified on the master drawing, use the qualification and lot acceptance test default values of A.3.7.4.3.1.

- A.3.7.4.4 Folding flexibility (class A only). When tested as specified in A.4.8.4.4, printed wiring board test specimen shall be capable of withstanding the specified conditions of A.3.7.4.4.1 or A.3.7.4.4.2, as applicable, without any evidence of damage, degradation or rejectable delamination. After the test, the electrical requirements specified in A.3.7.5.1 and A.3.7.5.2 shall be met.

- A.3.7.4.4.1 Qualification and periodic testing. The number of fold cycles shall be 25 cycles in both directions; center of the test specimen orthogonal to the longest length.

- A.3.7.4.4.2 <u>User specified (see 3.1.1 and 6.2)</u>. The folding flexibility test parameters shall be as specified on the master drawing. The minimum parameters specified on the master drawing shall be as follows:

- a. Direction of bend.

- b. Degree of bend.

- c. Number of fold cycles.

- d. Diameter of mandrel.

- e. Points of application.

- A.3.7.4.5 <u>Plating adhesion</u>. When tested as specified in A.4.8.4.5, there shall be no plating particles or conductor patterns removed from the printed wiring board test specimen except for outgrowth.

- A.3.7.4.6 <u>Rework simulation</u>. Rework simulation is not applicable for printed wiring board designs that do not use any plated through-holes for component attachment.

- A.3.7.4.6.1 <u>Types 1 and 5 with unsupported holes (bond strength)</u>. After undergoing the test specified in 4.8.4.6.1, the unsupported land shall withstand 5 pounds (2.27 Kg) pull or 500 lb/in (3.4 MPa), whichever is less.

- A.3.7.4.6.2 <u>Types 2, 3 and 4 with plated-through holes</u>. After undergoing the test specified in A.4.8.4.6.2, the type 2, 3 or 4 printed wiring board test specimens shall meet the following requirements:

- a. External visual and dimensional inspection: When inspected as specified in A.4.8.1, there shall be no evidence of blistering or delamination in excess of that allowed in A.3.5.

- b. Internal visual and dimensional inspection: The printed wiring board test specimen is microsectioned and inspected in accordance with A.4.8.2, the requirements specified in A.3.6 through A.3.6.14 shall be met.

#### APPENDIX A

- A.3.7.4.7 <u>Solderability</u>. Solderability testing is applicable only on printed wiring board designs that require soldering during circuit card assembly processes. Printed wiring board designs that use compliant pin technology only for component attachment do not require solderability testing. Printed wiring board designs that use surface mount components only shall be tested for surface solderability as specified in A.3.7.4.7.2.

- A.3.7.4.7.1 <u>Hole (plated through hole) solderability</u>. After undergoing the test specified in A.4.8.4.7.1, the printed wiring board test specimen shall conform to the accept/reject criterion (good wetting, pinholes, dewetting, non-wetting, etc.) specified in J-STD-003 class 3 or appendix E, as applicable.

- A.3.7.4.7.2 <u>Surface (or surface mount land)solderability</u>. After undergoing the test specified in A.4.8.4.7.2, the printed wiring board test specimen shall conform to the accept/reject criterion (good wetting, pinholes, dewetting, non-wetting, etc.) specified in J-STD-003 class 3 or appendix E, as applicable.

- A.3.7.4.8 <u>Solder resist cure and adhesion</u>. When tested as specified in A.4.8.4.8, the cured solder resist coating shall not exhibit tackiness, blistering, or delamination and the maximum percentage of cured solder resist lifted from the surface of the base material, conductors, and lands of the coated printed wiring board test specimen shall be in accordance with the following:

- a. Bare copper or base material: Maximum percentage of lifting 0 percent.

- b. Gold or nickel plating: Maximum percentage of lifting 5 percent.

- c. Tin-lead plating or solder coating: Maximum percentage of lifting 10 percent.

- A.3.7.4.9 <u>Surface peel strength (types 3 and 4 foil laminated printed wiring boards)</u>. After undergoing the test specified in A.4.8.4.9, the surface conductor shall withstand a minimum peel strength greater than or equal to the "after thermal stress" values for the corresponding copper foil type, profile and weight specified by the base material specification. This requirement is only applicable to foil laminated types 3 an 4 printed wiring boards that have surface conductors or surface mount lands. Printed wiring boards with no external circuitry (external terminal land or pads only) do not require peel strength testing.

# A.3.7.4.10 Thermal stress.

- A.3.7.4.10.1 <u>Types 1 and 5</u>. After undergoing the test specified in A.4.8.4.10, the printed wiring board test specimen shall be inspected in accordance with A.4.8.1 and shall not exhibit any cracking or separation of plating and conductors, blistering or delamination shall not exceed the limits allowed in A.3.5.1.3 and lands shall not lift in excess of that allowed in A.3.5.5.

- A.3.7.4.10.2 <u>Types 2, 3 and 4</u>. After undergoing the test specified in A.4.8.4.10, the printed wiring board test specimen shall be examined in accordance with A.4.8.1 and shall exhibit no blistering or delamination in excess of that allowed in A.3.5.1.3. After meeting the visual and dimensional requirements of A.3.5, the printed wiring board test specimen shall be microsectioned and inspected in accordance with A.4.8.2 and shall meet the requirements of A.3.6 through A.3.6.14.

#### APPENDIX A

#### A.3.7.5 Electrical requirements.

- A.3.7.5.1 <u>Continuity</u>. The circuit continuity test shall be in accordance with A.4.8.5.1. For qualification inspection there shall be no open circuits whose resistance exceeds 5 ohms. For production testing, there shall be no open circuit whose resistance exceeds 10 ohms. For referee purposes, 0.5 ohm maximum per inch of circuit length shall apply.

- A.3.7.5.2 <u>Circuit shorts</u>. When tested as specified in A.4.8.5.2, the resistance between mutually isolated conductors shall be greater than 2 megohms.

- A.3.7.5.3 <u>Dielectric withstanding voltage</u>. When inspected as specified in A.4.8.5.3, there shall be no flashover, sparkover, or breakdown.

- A.3.7.5.4 <u>Heat sinking planes</u>. When metal core printed wiring boards are inspected as specified in A.4.8.5.2, the dielectric material used to insulate the heat-sinking plane from circuitry and plated through holes shall provide an insulation resistance greater than 2 megohm. There shall be no flashover, sparkover, or dielectric breakdown.

## A.3.7.6 Environmental requirements.

- A.3.7.6.1 <u>Moisture and insulation resistance</u>. When tested as specified in A.4.8.6.1, the printed wiring board test specimen shall have a minimum of 500 megohms of resistance between conductors. After the test, the specimen shall be inspected in accordance with A.4.8.1 and the specimen shall not exhibit blistering, measling, or delamination in excess of that allowed in A.3.5.1.3.

- A.3.7.6.2 <u>Thermal shock</u>. While undergoing the test specified in A.4.8.6.2, a resistance change of 10 percent or more between the first and last high temperature measurements shall be considered a reject. After the test, the printed wiring board test specimens shall meet the following requirements:

- a. External visual and dimensional inspection (all types): When inspected as specified in A.4.8.1, there shall be no evidence of plating cracks, blistering, or delamination in excess of that allowed in A.3.5.1.3.

- b. Internal visual and dimensional inspection (types 3 and 4): When the printed wiring board test specimen is microsectioned and inspected in accordance with 4.8.2, the requirements specified in A.3.6 shall be met.

- A.3.8 Marking. Unless otherwise specified (see A.6.2), each production printed wiring board, each qualification test specimen, and each set of quality conformance test circuit strips (as opposed to each individual test coupon) shall be marked as specified (see A.3.1.1) and herein. As a minimum, each production printed wiring board, qualification test specimen, or quality conformance test circuit strip shall reference the printed wiring board manufacturers' CAGE (Commercial and Government Entity), lot date, and printed wiring board traceability code. The marking shall be produced by the same process used in producing the conductive pattern; or by the use of a nonconductive, fungistatic ink or paint applied to the printed wiring board or to a label which is applied to the printed wiring board; or by mechanical pencil marking on a metallic area provided for marking purposes may also be used. All marking shall be able to withstand solder fluxes, cleaning solutions, and molten solder encountered in the manufacture of printed wiring boards, shall remain legible after all tests, and in no manner affect printed wiring board performance.

#### APPENDIX A

- A.3.9 <u>Traceability</u>. Unless otherwise specified, traceability shall be available for review by the qualifying or contracting activity for a minimum of 3 years after delivery of the printed wiring boards.

- A.3.9.1 Quality conformance test circuitry and test coupons. Each quality conformance test circuitry (QCTC) shall be identifiable with those corresponding production printed wiring boards produced on the same panel that also produced the QCTC. All individual test coupons separated from its QCTC or qualification test specimen shall have its traceability maintained back to the QCTC or qualification test specimen from which the test coupons were separated.

- A.3.9.2 <u>Printed board materials</u>. Traceability shall be such that for each printed wiring board, all printed board materials specified or used shall be traceable to a material production lot, inspection lot, or other specified grouping.

- A.3.10 Repair. When inspected in accordance with A.4.8.1, printed wiring boards shall not reveal any evidence of repair.

- A.3.11 <u>Workmanship</u>. Printed wiring boards shall be processed in such a manner as to be uniform in quality and shall be free of defects in excess of those allowed in this appendix that could affect life or serviceability.

#### A.4 VERIFICATION

- A.4.1 Classification of inspections. The inspections requirements specified herein are classified as follows:

- a. Qualification inspection (see A.4.5).

- b. Inspection of product for delivery (see A.4.6).

- c. Periodic conformance inspection (see A.4.7).

- A.4.2 <u>Test and measuring equipment</u>. Measuring and test equipment of sufficient accuracy, quality, and quantity to permit performance of the required inspection shall be established and maintained by the manufacturer. The establishment and maintenance of a calibration system to control the accuracy of the measuring and test equipment shall be in accordance with NCSL Z540, or equivalent.

- A.4.3 <u>Inspection conditions</u>. Unless otherwise specified in the applicable test method or procedure, inspections and tests may be performed at ambient conditions.

- A.4.4 <u>Printed wiring board performance verification</u>. Printed wiring board performance verification shall consist of inspections on the production printed wiring boards and the QCTC or test coupons referenced in tables herein for in-process, groups A, B, and C inspections. Selection of test coupons for testing shall be in accordance with the applicable inspection table. Each production printed wiring board or panel of printed wiring boards shall include sufficient test coupons to complete the applicable verification requirements specified. The design of test coupons shall be as specified on the applicable master drawing (see A.3.1.1). The minimum number of test coupons on the production panel and the requirements for positioning the test coupons on the panel shall be in accordance with the requirements of the applicable design standard (see A.3.1.1 and appendix D).

#### APPENDIX A

#### A.4.5 Qualification inspection (see A.6.3).

A.4.5.1 Qualification eligibility. The fabrication of the qualification test vehicles may begin before authorization to test is granted, however before the start of qualification testing, the manufacturer must receive authorization from the qualifying activity.

## A.4.5.2 Samples.

- A.4.5.2.1 <u>Qualification test specimens</u>. Qualification test specimens shall conform to the following for the type of printed wiring boards for which qualification is sought:

- Type 1: The qualification test specimens for type 1 shall meet the requirements specified in master drawing IPC-100041 or IPC-100101.

- Type 2: The qualification test specimens for type 2 shall meet the requirements specified in master drawing IPC-100042 or IPC-100102.

- c. Types 3 and 4: The qualification test specimens for types 3 and 4 shall meet the requirements specified in master drawing IPC-100043 or IPC-100103.

- Type 5: The qualification test specimens for type 5 shall meet the requirements specified in master drawing IPC-100044.

- e. Class B: When qualifying for types 3 or 4 (normally class A), one type 1 or type 2 qualification test specimen shall also be submitted at the same time.

If design defaults are not listed on the qualification master drawing, then use the values contained in IPC-2221.

- A.4.5.2.1.1 <u>Modifications to qualification test specimens</u>. All portions of zones A, B, C (except for test coupon E-5), and D of the test pattern are now required for qualification testing. Requests for the modification of the qualification test specimens shall be made prior to, or at the time of, the request for qualification testing.

- A.4.5.2.2 <u>Sample size</u>. A sample of at least four qualification test specimens shall be produced by the manufacturer. Unless otherwise specified on the qualifying activity approved authorization, the qualification test specimens shall be serialized.

- A.4.5.3 <u>Inspection routines</u>. Qualification inspection shall consist of the tests and inspections specified below. The following details shall apply:

- a. Two qualification test specimens shall be tested by the manufacturer in accordance with A.4.5.3.1. These two qualification test specimens that passed the tests specified in A.4.5.3.1 shall then be destructively tested at a certified suitable laboratory in accordance with A.4.5.3.2.

- b. The two qualification test specimens not subjected to destructive testing shall be retained as reference samples by the manufacturer for a period of 12 months.

- A.4.5.3.1 <u>Manufacturer test routine</u>. The manufacturer shall perform the inspections specified in tables II and III (in-process and group A inspection) on zones A, B, and C of all of the completed printed wiring board in the lot. Test coupons needed for destructive testing and microsection inspection shall be taken from zone D. Further details concerning test coupons selection can be found in the application for qualification available form the qualifying activity.

#### APPENDIX A

- A.4.5.3.2 <u>Certified suitable laboratory test routine</u>. The certified suitable qualification laboratory shall subject two of the qualification test specimens to the inspections specified in table I. The order of the inspections and tests is optional; however, the cleanliness test shall be performed first.

- A.4.5.3.3 <u>Contract services</u>. Manufacturers wanting to use an external subcontracted service for production of printed wiring board shall first qualify using their own equipment/processes internal to their facility. Once qualified internally, a manufacturer may qualify using the subcontracted service. This additional subcontracted qualification will not be listed separately on the QPL. The subcontract service shall not be extended to another external subcontracted service or manufacturer.

NOTE: For the purposes of this appendix, the internal equipment/process condition applies only to those processes used to manufacture the qualification test specimen. When applying for qualification of sub-contracted services, the process and the company performing the sub-contracted service shall be identified. If the manufacturer has no internal capability to perform a certain production step (either used during qualification or only used during production) this shall be identified on the application for authorization to test. If the sub-contracted service is changed, the manufacturer shall requalify.

A.4.5.3.4 <u>Qualification rejection</u>. Qualification approval will not be granted if any of the qualification test specimens tested in accordance with table I fail to meet the specified requirements.

## A.4.5.4 Extent of qualification.

- A.4.5.4.1 <u>Printed wiring board type</u>. Qualification of a particular printed wiring board type shall be extended to cover all conductor patterns of that same printed wiring board type produced.

- a. Qualification of type 4 printed wiring boards shall be extended to cover all other types (5, 3, 2, and 1).

- b. Qualification of type 3 printed wiring boards shall be extended to cover types 1 and 2 printed wiring boards.

- c. Qualification of type 2 printed wiring boards shall be extended to cover type 1 printed wiring boards.

- d. Qualification of type 5 printed wiring boards shall be extended to cover type 1 printed wiring boards.

- e. Qualification of any type shall be extended to cover the approved type or types with a stiffener or solder resist.

- A.4.5.4.2 Classes. Qualification to flexibility class B shall be extended to cover flexibility class A.

#### APPENDIX A

#### A.4.5.4.3 Base material types.

- A.4.5.4.3.1 <u>Flexible base material types</u>. Qualification of any type of flexible base material type shall be extended to cover all flexible base material types. Qualification with a metal cladding adhesion method (adhesive/adhesiveless) shall be as follows:

- a. Adhesive family include all base materials that rely/use an adhesive to hold the metal to both sides of the dielectric. Note "cast" materials are considered to be in the adhesiveless family.

- b. Adhesiveless family includes all base materials that use other techniques (such as chemically deposited or vapor deposition) to adhere the basis metal to both sides of the dielectric.

- A.4.5.4.3.2 Rigid base material types. Qualification with a rigid base laminate material shall be as follows:

- a. Qualification with thermosetting resin (see IPC-T-50 and A.6.4.6.1) base material types shall be extended to cover all other types of thermosetting resin base materials.

- b. Qualification with thermoplastic resin (see IPC-T-50 and A.6.4.6.2) base material types shall be extended to cover all other types of thermoplastic resin base materials.

- A.4.5.4.4 <u>Stiffeners and solder resist</u>. Qualification of any printed wiring board type shall be extended to cover the approved type with a stiffener or solder resist.

- A.4.5.4.5 <u>Mass lamination (see A.6.4.4.1)</u>. Qualification of a contract lamination (four conductor layers) shall be extended to cover a contract lamination of three conductor layers. Qualification of a contract lamination (ten conductor layers) shall be extended to cover a contract lamination of three or more conductor layers. NOTE: Test specimens for four layer contract lamination shall meet the requirements specified in master drawing IPC-100044. Test specimens for ten layer contract lamination shall meet the requirements specified in master drawing IPC-100043.

## A.4.5.4.6 Processes.

- A.4.5.4.6.1 Etchback. Qualification using etchback shall be extended to cover non-etchback.

- A.4.5.4.6.2 <u>Process changes</u>. Any changes to a manufacturers qualified base material type, equipment, or processes must be reviewed by the qualifying activity for determination if partial or full regualification is necessary.

TABLE I. Qualification inspection.

|                                                                                            | Requirement                                                   | Method<br>Paragraph                                           |                   | Notes             |                   |                   |                   |                         |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|

| Inspection                                                                                 | Paragraph                                                     |                                                               | T1                | T2                | Т3                | T4                | T5                |                         |

| Visual and dimensional:                                                                    |                                                               |                                                               |                   |                   |                   |                   |                   |                         |

| Acceptability 3/                                                                           | A.3.7.1                                                       | A.4.8.1                                                       | PWB               | PWB               | PWB               | PWB               | PWB               | <u>3</u> /              |