National Aeronautics and Space Administration

# Microelectronics Reliability: Physics-of-Failure Based Modeling and Lifetime Evaluation

Mark White Jet Propulsion Laboratory Pasadena, California

Joseph B. Bernstein University of Maryland College Park, Maryland

Jet Propulsion Laboratory California Institute of Technology Pasadena, California

JPL Publication 08-5 2/08

National Aeronautics and Space Administration

# Microelectronics Reliability: Physics-of-Failure Based Modeling and Lifetime Evaluation

NASA Electronic Parts and Packaging (NEPP) Program Office of Safety and Mission Assurance

> Mark White Jet Propulsion Laboratory Pasadena, California

Joseph B. Bernstein University of Maryland College Park, Maryland

NASA WBS: 939904.01.11.10 JPL Project Number: 102197 Task Number: 1.18.5

Jet Propulsion Laboratory 4800 Oak Grove Drive Pasadena, CA 91109

http://nepp.nasa.gov

This research was primarily carried out at the University of Maryland under the direction of Professor Joseph B. Bernstein and was sponsored in part by the National Aeronautics and Space Administration Electronic Parts and Packaging (NEPP) Program, the Aerospace Vehicle Systems Institute (AVSI) Consortium—specifically, AVSI Project #17: Methods to Account for Accelerated Semiconductor Wearout—and the Office of Naval Research.

Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States Government or the Jet Propulsion Laboratory, California Institute of Technology.

Copyright 2008. All rights reserved.

# PREFACE

The solid-state electronics industry faces relentless pressure to improve performance, increase functionality, decrease costs, and reduce design and development time. As a result, device feature sizes are now in the nanometer scale range and design life cycles have decreased to fewer than five years.

Until recently, semiconductor device lifetimes could be measured in decades, which was essentially infinite with respect to their required service lives. It was, therefore, not critical to quantify the device lifetimes exactly, or even to understand them completely. For avionics, medical, military, and even telecommunications applications, it was reasonable to assume that all devices would have constant and relatively low failure rates throughout the life of the system; this assumption was built into the design, as well as reliability and safety analysis processes.

Technological pressures on the electronics industry to reduce transitor size and decrease cost while increasing transitor count per chip, however, runs counter to the needs of most high-reliability applications where long life with exceptional reliability is critical. As design rules have become tighter, power consumption has increased and voltage margins have become almost non-existent for the designed performance level. In achieving the desired performance levels, the lifetime of most commercial parts is the ultimate casualty. Most large systems are built with the assumption that electronic components will last for decades without failure. However, counter to this assumption, device reliability physics is becoming so well understood that manufacturing foundries are designing microcircuits for a three- to seven-year useful life, as that is what most of the industry seeks. The military, aerospace, medical, and especially the telecommunications industries cannot afford to depend on custom parts for their most sophisticated circuit designs.

Hence, we have developed this guideline document as an approach for system designers and device reliability engineers to develop a better understanding of device failures as a result of wearout, and to provide a better understanding of how current reliability models are applied in practice. We describe the best possible approaches to modeling reliability concerns in some of the

Preface

more advanced microelectronic technologies, and provide in-depth descriptions on how to implement into reliability equivalent circuits for spacecraft, planets, instrument, C-matrix, events (SPICE) simulation. Within the inherent limitations of high-power, high-speed, commercial Complementary Metal Oxide Semiconductor (CMOS) devices, suggestions are developed on how to model the incipient failure rate, how to trade circuit performance with reliability, and how to obtain a predictable end-of-life or component-level system repair rate through realistic time-dependent reliability prediction.

The development of this handbook for evaluating and simulating microelectronic systems reliability has been an ongoing project of the Microelectronics Reliability Engineering program at the University of Maryland, College Park, for more than six years. The program has been funded by the Aerospace Vehicle Systems Institute (AVSI) Consortium and the NASA Electronic Parts and Packaging (NEPP) Program Scaled CMOS Reliability Task, as well as the Office of Naval Research. Several doctoral dissertations have resulted from this work and major contributions were carried out by a number of individuals, including Jöerg Walters, Xiaohu Zhang, Xiaojun Li, Bing Huang, Jin Qin, Mark White, Moshe Gurfinkel, Shahrzad Salami, Qinguo Fan, Zvi Gur, Michael Talmor, and Yoram Shapira.

# ACRONYMS

| ADC     | Analog-to-Digital Converter                       |  |

|---------|---------------------------------------------------|--|

| AHI     | Anode Hole Injection                              |  |

| AHR     | Anode Hydrogen Release                            |  |

| ALT     | Accelerated Life Testing                          |  |

| AST     | Accelerated Stress Tests                          |  |

| ATPG    | Automatic Test Pattern Generation                 |  |

| AVSI    | Aerospace Vehicle Systems Institute               |  |

| BERT    | Berkeley Reliability Tools                        |  |

| BIR     | Built-In-Reliability                              |  |

| BTI     | Biased Temperature Instability                    |  |

| CAD     | Computer Aided Design                             |  |

| CADMP-2 | Computer-Aided Design of Microelectronic Packages |  |

| CALCE   | Computer-Aided Life-Cycle Engineering             |  |

| CDF     | Cumulative Distribution Function                  |  |

| CFR     | Constant Failure Rate                             |  |

| CHC     | Channel Hot Carrier                               |  |

| CHE     | Channel Hot Electron                              |  |

| CMOS    | Complementary Metal Oxide Semiconductor           |  |

| COTS    | Commercial-off-the-Shelf                          |  |

| DAC     | Digital-to-Analog Converter                       |  |

| DAHC    | Drain Avalanche Hot Carrier                       |  |

| DFR     | Design-For-Reliability                            |  |

| DNL     | Differential Nonlinearity                         |  |

| EM      | Electromigration                                  |  |

| EOS     | Electrical Overstress                             |  |

| ETM     | Effective Temperature Models                      |  |

## Acronyms

| FaRBS    | Failure Rate Based SPICE                                |

|----------|---------------------------------------------------------|

| FPGA     | Field Programmable Gate Array                           |

| FIT      | Failure in Time                                         |

| FN       | Fowler-Nordheim                                         |

| GCA      | Gradual Channel Approximation                           |

| GIDL     | Gate-Induced Drain Leakage                              |

| GOS      | Gate Oxide Short                                        |

| HCD      | Hot Carrier Degradation                                 |

| HCI      | Hot Carrier Injection                                   |

| HISREM   | Hot Carrier Induced Series Resistance Enhancement Model |

| HTOL     | High Temperature Operating Life                         |

| ICs      | Integrated Circuits                                     |

| INL      | Integral Nonlinearity                                   |

| ITRS     | International Technology Roadmap for Semiconductor      |

| KCL      | Kirchhoff's Current Law                                 |

| LDD      | Lightly Doped Drain                                     |

| LEM      | Lucky Electron Model                                    |

| LNA      | Low Noise Amplifier                                     |

| LSB      | Least Significant Bit                                   |

| MACRO    | Maryland Circuit-Reliability Oriented                   |

| MIL-HDBK | Military Handbook                                       |

| MOS      | Metal Oxide Semiconductor                               |

| MOSFET   | Metal Oxide Semiconductor Field Effect Transistor       |

| MSM      | Matrix Stressing Method                                 |

| MTBF     | Mean Time between Failures                              |

| MTTF     | Mean-Time-To-Failure                                    |

| NBTI     | Negative Bias Temperature Instability                   |

| NEPP     | NASA Electronic Parts and Packaging Program             |

|          |                                                         |

| NMOS    | N-Channel Metal Oxide Semiconductor                         |

|---------|-------------------------------------------------------------|

| NMOSFET | N-Channel Metal Oxide Semiconductor Field Effect Transistor |

| PBTI    | Positive Bias Temperature Instability                       |

| PMOS    | P-Channel Metal Oxide Semiconductor                         |

| PMOSFET | P-Channel Metal Oxide Semiconductor Field Effect Transistor |

| PoF     | Physics-of-Failure                                          |

| RAC     | Reliability Analysis Center                                 |

| RAMP    | Reliability Aware Micro-Processor                           |

| RF      | Radio Frequency                                             |

| RT      | Room Temperature                                            |

| SFDR    | Spurious-Free-Dynamic-Range                                 |

| SGHE    | Secondary Generated Hot Electron                            |

| SHA     | Sample-and-Hold Amplifier                                   |

| SHE     | Substrate-Hotelectron                                       |

| S/H     | Sample-and-Hold                                             |

| SNDR    | Signal-to-Noise-Plus-Distortion                             |

| SNM     | Static Noise Margin                                         |

| SPICE   | Spacecraft, Planets, Instrument, C-matrix, Events           |

| SRAM    | Static Random Access Memory                                 |

| SoC     | System-on-Chip                                              |

| SOFR    | Sum-of-Failure-Rates                                        |

| TBD     | Time-to-Breakdown                                           |

| TCAD    | Technology Computer Aided Design                            |

| TDDB    | Time-Dependent Dielectric Breakdown                         |

| UIUC    | University of Illinois at Urbana-Champaign                  |

| VHDL    | Very High Density Logic                                     |

| VTC     | Voltage Transfer Characteristics                            |

| VLSI    | Very Large Scale Integration                                |

|         |                                                             |

# CONTENTS

| Exe | ecutiv                             | e Summ                  | ary                                             | 1  |

|-----|------------------------------------|-------------------------|-------------------------------------------------|----|

| 1   | Intr                               | oduction                | n                                               | 3  |

|     | 1.1                                | Organ                   | ization                                         | 3  |

|     | 1.2                                | Reliab                  | vility Prediction from a Historical Perspective | 4  |

|     |                                    | 1.2.1                   | Traditional Approach                            | 5  |

|     |                                    | 1.2.2                   | Physics-of-Failure Approach                     | 16 |

|     |                                    | 1.2.3                   | Recent Approach: RAMP                           |    |

|     | 1.3                                | Reliab                  | vility Modeling and Prediction Today            | 20 |

|     |                                    | 1.3.1                   | Competing Mechanisms Theory                     |    |

|     |                                    | 1.3.2                   | FaRBS                                           |    |

|     |                                    | 1.3.3                   | MaCRO                                           |    |

|     | 1.4                                | Summ                    | nary                                            |    |

| 2   | Electron Device Physics of Failure |                         |                                                 | 27 |

|     | 2.1                                | Electro                 | omigration                                      |    |

|     |                                    | 2.1.1                   | Introduction                                    |    |

|     |                                    | 2.1.2                   | Basic Physics Process of EM                     |    |

|     |                                    | 2.1.3                   | Statistical Models of EM                        |    |

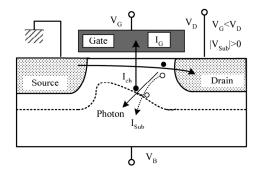

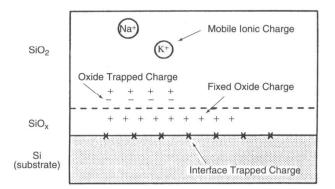

|     | 2.2                                | Hot Carrier Degradation |                                                 | 40 |

|     |                                    | 2.2.1                   | Introduction                                    | 40 |

|     |                                    | 2.2.2                   | Hot Carriers                                    | 40 |

|     |                                    | 2.2.3                   | Hot Carrier Injection Mechanisms                |    |

|     |                                    | 2.2.4                   | HCD Models                                      | 45 |

|     |                                    | 2.2.5                   | Acceleration Factors                            |    |

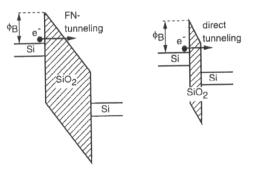

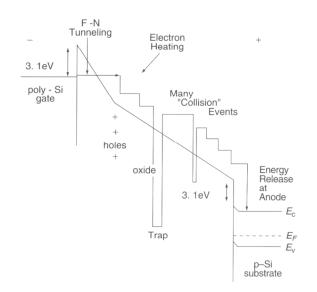

|     | 2.3                                | Time-                   | Dependent Dielectric Breakdown                  |    |

|     |                                    | 2.3.1                   | Introduction                                    |    |

|     |                                    | 2.3.2                   | Physics of Breakdown                            |    |

|     |                                    | 2.3.3                   | Oxide Breakdown Models                          |    |

|     |                                    | 2.3.4                   | Acceleration Factors                            |    |

|     | 2.4                                | Negati                  | ive Bias Temperature Instability                |    |

|     |                                    | 2.4.1                   | Introduction                                    | 65 |

|     |                                    | 2.4.2                   | NBTI Failure Mechanisms                         |    |

|     |                                    | 2.4.3                   | NBTI Models                                     | 70 |

| 3   | Fail                               | ure Rate                | e Based SPICE (FaRBS) Reliability Simulation    | 73 |

|     | 3.1                                |                         | uction                                          |    |

|     | 3.2                                | Modul                   | les and the Process of FaRBS                    | 73 |

|     |        | 3.2.1                                                         | Sensitivity Analysis                                               | 74  |

|-----|--------|---------------------------------------------------------------|--------------------------------------------------------------------|-----|

|     |        | 3.2.2                                                         | SPICE Simulation                                                   | 75  |

|     |        | 3.2.3                                                         | Wearout Models                                                     | 76  |

|     |        | 3.2.4                                                         | System Reliability Model                                           | 77  |

|     | 3.3    | Parame                                                        | eter Extraction Model                                              | 77  |

|     | 3.4    | Deratin                                                       | g Voltage and Temperature for Reliability                          | 78  |

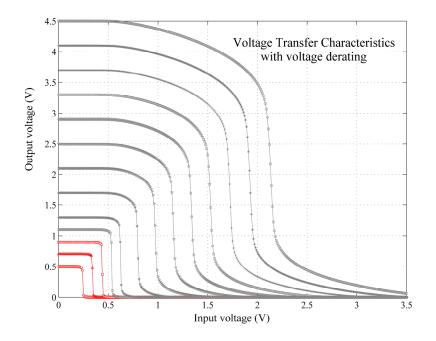

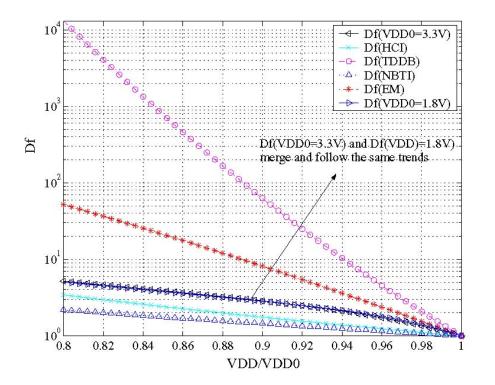

|     |        | 3.4.1                                                         | Circuit Design and Simulation                                      | 79  |

|     |        | 3.4.2                                                         | Simulation Results and Analysis                                    | 80  |

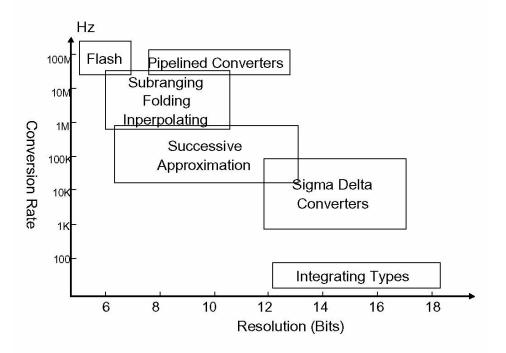

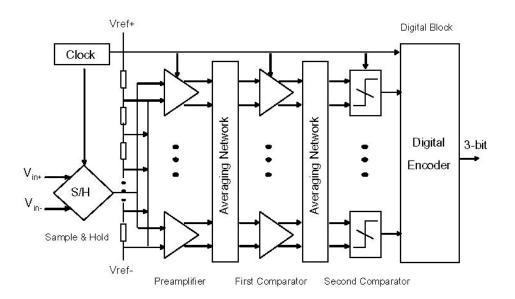

|     | 3.5    | FaRBS                                                         | Application: An Analog-to-Digital Converter Reliability Simulation | 94  |

|     |        | 3.5.1                                                         | Introduction                                                       | 94  |

|     |        | 3.5.2                                                         | ADC Circuits                                                       | 95  |

|     |        | 3.5.3                                                         | FaRBS Analysis of ADC Reliability                                  | 104 |

| 4   | Micr   | oelectro                                                      | nic Circuit Reliability Analysis and MACRO                         | 111 |

|     | 4.1    | Introdu                                                       | ction                                                              | 111 |

|     | 4.2    | Hot Ca                                                        | rrier Injection                                                    | 111 |

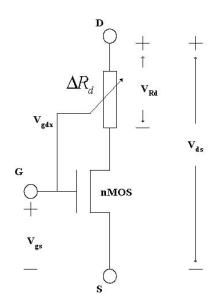

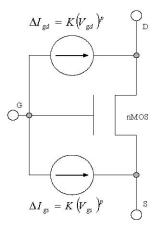

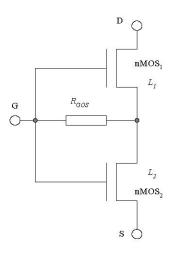

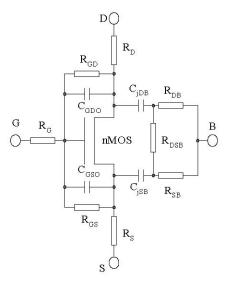

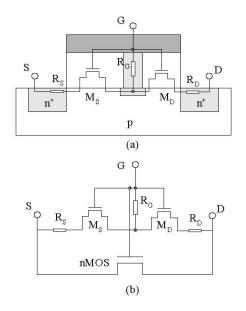

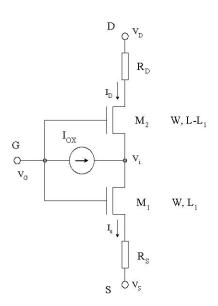

|     |        | 4.2.1                                                         | Failure-Equivalent Circuit Model                                   | 116 |

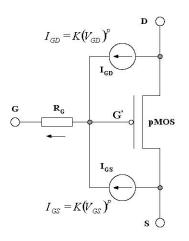

|     | 4.3    | Time-I                                                        | Dependent Dielectric Breakdown                                     | 124 |

|     |        | 4.3.1                                                         | Failure Equivalent Circuit Model                                   | 130 |

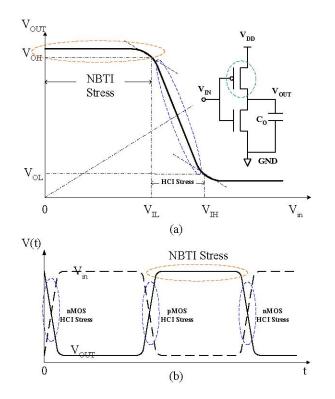

|     | 4.4    | Negativ                                                       | ve Bias Temperature Instability                                    | 141 |

|     |        | 4.4.1                                                         | Failure Equivalent Circuit Model                                   |     |

|     | 4.5    | MaCRO                                                         | O Application: An SRAM Reliability Simulation and Analysis         | 154 |

|     |        | 4.5.1                                                         | Introduction                                                       | 154 |

|     |        | 4.5.2                                                         | SRAM Circuit Design and Simulation                                 | 154 |

|     |        | 4.5.3                                                         | Preview of SRAM Failure Behaviors                                  | 161 |

|     |        | 4.5.4                                                         | Device Lifetime Calculation                                        | 162 |

|     |        | 4.5.5                                                         | SPICE Reliability Simulation with Circuit Models                   | 166 |

|     |        | 4.5.6                                                         | Reliability Design Techniques                                      | 176 |

|     |        | 4.5.7                                                         | Summary                                                            | 177 |

| 5   | Micr   | Microelectronic System Reliability                            |                                                                    |     |

|     | 5.1    | Introdu                                                       | ction                                                              | 179 |

|     | 5.2    | Individual Failure Mechanism Lifetime Models                  |                                                                    | 180 |

|     | 5.3    | 3 Microelectronic System Voltage and Temperature Acceleration |                                                                    | 183 |

|     |        | 5.3.1                                                         | Non-Arrhenius Temperature Acceleration                             | 185 |

|     |        | 5.3.2                                                         | Stress-Dependent Voltage Acceleration Factor                       | 186 |

|     |        | 5.3.3                                                         | Combined Voltage and Temperature Acceleration Factor               | 188 |

|     | 5.4    | Qualifi                                                       | cation Based on Failure Mechanism                                  | 188 |

|     | 5.5    | Summa                                                         | ary                                                                | 189 |

| Ref | erence | es                                                            |                                                                    | 199 |

# **EXECUTIVE SUMMARY**

This handbook presents a physics-of-failure approach to microelectronics reliability modeling and assessment. Knowledge of the root cause and physical behavior of key failure mechanisms in microelectronic devices has improved dramatically over recent years and has led to the development of more sophisticated reliability modeling tools and techniques. Some of these tools are summarized here.

Chapter 1 provides an overview of traditional reliability prediction approaches, i.e., MIL-HDBK-217 compared with some of the more recent reliability modeling and prediction approaches, including Reliability Aware Micro-Processor (RAMP) Model, Failure Rate Based SPICE (FaRBS) reliability simulation, and Maryland Circuit-Reliability Oriented (MaCRO) simulation. Chapter 2 describes the intrinsic wearout mechanisms of the electron device, including physics processes, mechanisms and models of electromigration (EM), hot carrier degradation (HCD), time-dependent dielectric breakdown (TDDB), and negative bias temperature instability (NBTI). In Chapter 3, the modules and processes of FaRBS reliability simulation, model parameter extraction, and derating of voltage and temperature for reliability are described. Sensitivity analysis and spacecraft, planets, instrument, C-matrix, events (SPICE) simulation of the wearout models are also discussed. To account for the effect of wearout mechanisms on circuit functionality and reliability, the device-level accelerated lifetime models are extended to microelectronic circuitlevel applications and an analog-to-digital converter reliability simulation using the FaRBS application is provided. Lifetime and failure equivalent circuit models for HCI, TDDB, and NBTI are presented in Chapter 4, Microelectronic Circuit Reliability Analysis and MaCRO. This chapter includes an illustrative case study for the purpose of demonstrating how to apply MaCRO models and algorithms to circuit reliability simulation, analysis, and improvement. The most common circuit structures used in reliability simulations are the ring oscillator, the differential amplifier, and the Static Random Access Memory (SRAM). The SRAM is selected as a case study vehicle to show the applicability of MaCRO models and algorithms in circuit reliability simulation and analysis. Chapter 5, in conclusion, describes the microelectronic system aspect of reliability, including impact to the system of individual failure mechanism lifetime models, voltage and temperature acceleration, and qualification based on failure mechanism and application. A failuremechanism-based qualification methodology using specifically designed stress conditions over traditional approaches (i.e., one voltage and one temperature) can lead to improved reliability predictions for targeted applications and optimized burn-in, screening, and qualification test plans.

# **1 INTRODUCTION**

#### 1.1 Organization

Microelectronics integration density is limited by the reliability of the manufactured product at a desired circuit density. Design rules, operating voltage, and maximum switching speeds are chosen to ensure functional operation over the intended lifetime of the product. To determine the ultimate performance for a given set of design constraints, reliability must be modeled for its specific operating condition.

Reliability modeling for the purpose of lifetime prediction is, therefore, the ultimate task of a failure physics evaluation. Unfortunately, existing industrial approaches to reliability evaluation fall short of predicting failure rates or wearout lifetime of semiconductor products. This is mainly attributed to the lack of a unified approach for predicting device failure rates, and the fact that all commercial reliability evaluation methods rely on the acceleration of a single, dominant failure mechanism.

Over the last several decades, knowledge of the root cause and physical behavior of the critical failure mechanisms in microelectronic devices has grown significantly. Confidence in historical reliability models has led to more aggressive design rules that have been successfully applied to the latest Very Large Scale Integration (VLSI) technology. One result of improved reliability modeling has been accelerated performance; that is, performance beyond the expectation of Moore's Law. A consequence of more aggressive design rules has been a reduction in the significance of a single-failure mechanism. Hence, in modern devices, there is no single-failure mode that is more likely to occur than any other within a range of specified operating conditions. This is practically guaranteed by the integration of modern simulation tools in the design process. The consequence of more advanced reliability modeling tools is a new awareness that device failures result from a combination of several competing failure mechanisms.

1 Introduction

#### 1.2 Reliability Prediction from a Historical Perspective

Reliability modeling and prediction is a relatively new discipline. Only since World War II has reliability become a subject of study due to the relatively complex electronic equipment used during the war and the high failure rates observed.

Since then, there have been two different approaches for reliability modeling corresponding to different time periods. Until the 1980s, the exponential, or constant failure rate (CFR), model [1] had been the only model used for describing the useful life of electronic components. It was common to the six reliability prediction procedures that were reviewed by Bowles [2] and was the foundation of the military handbook for reliability prediction of electronic equipments (known as the Military-Handbook-217 [MIL-HDBK-217] [3] series) that became the de facto industry standard for reliability prediction. Although the CFR model was used without physical justification, it is not difficult to reconstruct the rationale for the use of the CFR model, which mathematically describes the failure distribution of systems wherein the failures are due to completely random or chance events. Throughout that period, electronic equipment complexity began to increase significantly. Similarly, the earlier devices were fragile and had several intrinsic failure mechanisms that combined to result in a constant failure rate.

During the 1980s and early 1990s, with the introduction of integrated circuits (ICs), more and more evidence was gathered suggesting that the CFR model was no longer applicable. Phenomena such as infant mortality and device wearout dominated failures; these failures could not be described using the CFR model. In 1991, two research groups, IIT Research Institute/Honeywell SSED and the Westinghouse/University of Maryland teams, both recommended that, on the basis of their research and findings, the CFR model should not be categorically applied [4] to further updates of MIL-HDBK-217. They further recommended that the exponential distribution should not be applied to every type of component and system without due awareness.

The end of the CFR as a sole model for reliability modeling was officially set with the publication of the "Perry Memo." Responding to increasing criticism of CFR, Secretary of Defense William Perry issued a memorandum in 1994 that effectively eliminated the use of most defense

standards, including the MIL-HDBK-217 series. Many defense standards were cancelled at that time and, in their place, the Department of Defense (DoD) encouraged the use of industry standards, such as the ISO 9000 series for quality assurance.

Since then, the physics-of-failure approach has dominated reliability modeling. In this approach, the root cause of an individual failure mechanism is studied and corrected to achieve some determined lifetime. Since wearout mechanisms are better understood, the goal of reliability engineers has been to design dominant mechanisms out of the useful life of the components by applying strict rules for every design feature. The theoretical result of this approach is, of course, that the expected wearout failures are unlikely to occur during the normal service life of microelectronic devices. Nonetheless, failures do occur in the field and reliability prediction has had to accommodate this new theoretical approach to the virtual elimination of any one failure mechanism limiting the useful life of an electronic device.

# 1.2.1 Traditional Approach

### MIL-HDBK-217

The first brick of all traditional (empirical) reliability improvement methodologies was laid with MIL-HDBK-217. It was published in 1965 to achieve the following goals:

- To organize the reliability-data collected from the field.

- To find the basis for better designs.

- To give the "quantitative reliability requirements."

- To estimate the reliability before full-scale production [5].

MIL-HDBK-217 soon became a standard; it was subsequently updated several times to keep pace with technology advancement as well as the changes in prediction procedures. Meanwhile, other organizations started to develop their own prediction models suitable for their own industries.

#### 1 Introduction

In the 1990s, attempts were focused on finding an electronic system reliability assessment methodology, including causes of failures, that could be used in the design and manufacturing of electronic systems. To cover the vast range of electronic devices, the notion of a "similar-system" was invented. The term "similar-system" refers to a system that uses similar technology and is built for similar application, or performs a similar function. The next step was to find whether the "similar-system" was used for existing field data. The data from a predecessor system could be used to generate the prediction of a new "similar-system" to the extent that the new generation was evolutionary (not revolutionary). The key process was the translation of the almost-old data to the new similar-system by considering the differences reflected in complexity and temperature, as well as the environmental and learning factors [5].

The last version of MIL-HDBK-217 (MIL-HDBK-217F) covers a wide range of major electronic component categories used in modern military systems, from microcircuits and discrete semiconductors to passive components such as resistors and capacitors [6]; for each of these areas, the handbook presents a straightforward equation for calculating the failure rate in failures per million hours. According to its claim, the goal of the handbook is to "establish and maintain consistent and uniform methods for estimating the inherent reliability of the mature designs of military equipment and systems" [3].

It is possible to classify the concepts behind the traditional MIL-HDBK-217F prediction procedures as:

- The constant-failure-rate: The constant-failure-rate reliability model is used by most of the empirical-electronic reliability prediction approaches. The failure rate of the system containing different components is the summation of its components, which means that all system components are in series.

- 2.  $\pi$  factors: Almost all of the traditional prediction methods have a base failure rate modified by several  $\pi$  factors. Microcircuits, gate/logic arrays, and microprocessors incorporate stress models as a combination of package and parts. Examples of  $\pi$  factors include  $\pi_{CF}$  (Configuration Factor),  $\pi_E$  (Environmental Factor), and  $\pi_Q$  (Quality Factor). These

multiplication factors are included in the total failure rate calculation, Equation (1.1); are defined in MIL-HDBK-217F; and are based on different configuration levels, environmental stress levels, and quality levels for the part.

3. Two basic methods for performing reliability prediction based on the data observation include the parts count and the parts stress analysis. The parts count reliability prediction method is used for the early design phases, when not enough data is available but the numbers of component parts are known. The information for parts count method includes generic part types, part quantity, part quality levels (when known or can be assumed), and environmental factors. The general expression for item failure rate with this method is:

$$\lambda_S = \sum_{i=1}^n N_i (\lambda_g \pi_Q)_i \tag{1.1}$$

where  $\lambda_s$  is the total failure rate,  $\lambda_g$  is the failure rate of the *i*<sup>th</sup> generic part,  $\pi_Q$  is the quality factor of the *i*<sup>th</sup> part,  $N_i$  is the quantity of the *i*<sup>th</sup> generic part, and *n* is the number of the generic part categories. If the parts operating in the equipment are operating in more than one environment, the above equation is applied to each portion of the equipment in a distinct environment. The overall equipment failure rate is obtained by summing the failure rates for each environment.

The part stress model is based on the effect of mechanical, electrical, and environmental stress and duty cycles, such as temperature, humidity, vibration, etc., on the part failure rate. The part failure rate varies with applied stress and the strength-stress interaction determines the part failure rate [7]. This method is used when most of the design is complete and the detailed part stress information is available. It is applicable during later design phases as well. Since more information is available at this stage, the result is more accurate than the part count method. An example of the microelectronic circuit part stress is:

$$\lambda_p = (C_1 \pi_T + C_2 \pi_E) \pi_Q \pi_L \tag{1.2}$$

where  $\lambda_p$  is the part failure rate and  $C_I$ ,  $C_2$  are the complexity of the die base failure rate (such as the number of gates) and the complexity of the package type (such as pin count), respectively;  $\pi_T$  is the temperature acceleration factor for the related failure mechanism;  $\pi_E$  is the environmental factor; and  $\pi_L$  is the learning factor, which considers the maturity of the device manufacturing line [6].

Component quality affects the part failure rate and is based on the component quality level, which is determined by the tests and screening in the manufacturing process. Since there are different technologies in this regard, there are several types of quality levels.

The environmental  $\pi$  factor defines the sensitivity of environmental stress on the device. Different prediction methods have their own list of environmental factors suitable for their device conditions. For instance, the environmental  $\pi$  factors defined in MIL-HDBK-217F cover almost all of the environmental stresses suitable for military electronic devices (the exception is ionizing radiation).

The learning factor shows the maturity of the device and suggests that the first versions are less reliable than subsequent generations. For instance, the learning  $\pi$  factor in the military handbook tries to take into consideration the effect of the number of years that the product has been in production. Therefore, the appropriate acceleration models are applied to the failure rates.

Table 1.1 gives the temperature acceleration factor used in some of the traditional prediction procedures [2].

8

| Procedural<br>Method | emperature Acceleration Factor                                                                                                                                     |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MIL-HDBK-217F        | $= 0.1 \exp[-A(1/T_j - 1/298)]$                                                                                                                                    |  |

| HRD4                 | $T_{j} = 1$ , for $T_{j} \le 70^{\circ}$ C; 2.6 • 10 <sup>4</sup> exp[- 3500/ $T_{j}$ ] + 1.8 • 10 <sup>13</sup> exp[-11600/ $T_{j}$ ], for $T_{j} > 70^{\circ}$ C |  |

| NTT                  | $\pi_T = \exp[3480(1/339 - 1/T_j)] + \exp[8120(1/356 - 1/T_j)]$                                                                                                    |  |

| CNET                 | $\pi_T = A_1 \exp[-3500/T_j] + A2 \exp[11600/T_j]$                                                                                                                 |  |

| Siemens              | $\pi_T = A \exp[E_{a1} \bullet 11605(1/T_{j1} - 1/T_{j2})] + (1 - A) \exp[E_{a2} \bullet 11605(1/T_{j1} - 1/T_{j2})]$                                              |  |

**Table 1.1**. Different procedural temperature acceleration factors.

The common acceleration models are:

### **Arrhenius Law of Temperature**

$$AF_T = \exp[\frac{E_a}{k}(\frac{1}{T_1} - \frac{1}{T_2})]$$

(1.3)

where  $E_a$  is the activation energy, k is the Boltzmann's constant, and  $T_1$  and  $T_2$  are temperatures in Kelvin.

#### Kemeny Model for Voltage Acceleration

$$\lambda = \exp[C_0 - \frac{E_a}{kT_j}] \exp[C_1(\frac{V_{cb}}{V_{cbmax}})]$$

(1.4)

where  $V_{cb}$  is the collector-base voltage,  $V_{cbmax}$  is the maximum collector-base voltage before breakdown, and  $C_0$  and  $C_1$  are material-related constants.

# Peck's Law for Temperature Humidity

$$AF = (\frac{M_{use}}{M_{test}})^{-n} \exp[\frac{E_a}{k}(\frac{1}{T_{use}} - \frac{1}{T_{test}})]$$

(1.5)

where  $M_{use}$  is the moisture level in service,  $M_{test}$  is the moisture level in test, and *n* is a material constant.

## **Coffin-Mason Based Law for Fatigue**

$$AF = \frac{N_{use}}{N_{test}} = \left[\frac{\Delta T_{test}}{\Delta T_{use}}\right]^n \tag{1.6}$$

Examples of traditional reliability prediction approaches include the Telcordia, CNET, RDF, SAE, BT-HRD-5, Siemens, NTT, PRISM, and FIDES procedures. Table 1.2 provides common applications and procedural methods for those traditional approaches [8]:

Table 1.2. Procedural methods and applications.

| Procedural Method          | Application               |  |

|----------------------------|---------------------------|--|

| MIL-HDBK-217               | Military                  |  |

| Telcordia SR-332           | Telecom                   |  |

| CNET                       | Ground Military           |  |

| RDF-93 and 2000            | Civil Equipment           |  |

| SAE Reliability Prediction | Automotive                |  |

| Method                     | Telecom                   |  |

| BT-HRD-5                   | Siemens products          |  |

| Siemens SN29500            | Telecom                   |  |

| NTT Procedure              | Commercial and Military   |  |

| PRISM                      | Aeronautical and Military |  |

| FIDES                      | Aeronautical and Military |  |

#### Telcordia

The Telcordia (also called Bellcore) methodology from May 2001 was developed by Bell Communication Research (Telcordia Technologies Inc.) and focuses on equipment for the telecommunications industry. The main concepts in MIL-HDBK-217 and Telcordia SR-332 are similar, but Telcordia's SR-332 includes the ability to incorporate burn-in, field, and laboratory test data using a Bayesian analysis.

The basis of the Telcordia model for devices is referred to as the black box technique. This parts count method defines a black box steady-state failure rate,  $\lambda_{BB}$ , for different device types as:

$$\lambda_{BB} = \lambda_G \cdot \pi_Q \cdot \pi_S \cdot \pi_T \tag{1.7}$$

where  $\lambda_G$  is the generic steady-state failure rate for the particular device,  $\pi_Q$  is the quality factor,  $\pi_S$  is the electrical stress factor, and  $\pi_T$  is the temperature factor.

Parts count steady-state failure rate for units,  $\lambda_{PC}$ , is defined by:

$$\lambda_{PC} = \pi_E \sum_{i=1}^n N_i \lambda_{SSi} \tag{1.8}$$

where  $\lambda_{SSi}$  is the steady-state device failure rate of device *i*,  $\pi_E$  is the unit's environment factor,  $N_i$  is the quantity of device type *i*, and *n* is the number of device types in the unit.

The system failure rate,  $\lambda_{SYS}$ , is the sum of all failure rates of the units contained in a system:

$$\lambda_{SYS} = \sum_{j=1}^{M} \lambda_{PCj} \tag{1.9}$$

where  $\lambda_{PCi}$  is the failure rate of unit *j* and *M* is the number of units in system.

## PRISM

PRISM was developed by the Reliability Analysis Center (RAC) under contract with the U.S. Air Force in the 1990s. The latest version of the method, which is available in a software version, was released in July 2001. RAC Rates is the name of the PRISM mathematical model for component failure rates; the component models are based on data derived from several sources. PRISM applies Bayesian methods with empirical data to obtain a system-level prediction. This methodology considers the failures of components as well as those related to the system. However, the component models are the heart of the analysis. The methodology provides different models for capacitors, diodes, integrated circuits, resistors, thyristors, transistors, and software. The total component failure rate is composed of:

- 1. Operating conditions.

- 2. Non-operating conditions.

- 3. Temperature cycling.

- 4. Solder joint.

- 5. Electrical overstress (EOS).

For components without a defined RAC Rates model, PRISM provides "Non-electronic Parts Reliability and Electronic Parts Reliability Data" books for reference. A multitude of part types can be found in these references with failure rates for various environments.

The general PRISM failure rate of a system,  $\lambda_{SYS}$ , is:

$$\lambda_{SYS} = (PG) \sum_{i=1}^{N} (\lambda_P)_i + \lambda_{SW}$$

(1.10)

where *PG* is the process grade,  $\lambda_P$  is the RAC Rate failure rate of the *i*<sup>th</sup> component, and  $\lambda_{SW}$  is the RAC Rate failure rate of software.

Unlike other handbook constant failure rate models, RAC Rates models do not have a separate factor for part quality level. Quality level is implicitly accounted for by a method known as process grading. Process grading addresses factors such as design, manufacturing, part procurement, and system management, which are intended to capture the extent to which measures have been taken to minimize the occurrence of system failures.

#### FIDES

The FIDES [9, 10] prediction method attempts to predict the constant failure rate experienced in the useful life portion of the classic bathtub curve. This approach models intrinsic failures together with extrinsic failures resulting from equipment specification, design, production, and integration, as well as selection of the procurement route. The methodology takes into account failures resulting from development and manufacturing and the over-stresses linked to the application, such as electrical, mechanical, and thermal. At the highest level, the FIDES method is comprised of three basic factors:

$$\lambda = \lambda_{Phy} \cdot \pi_{Partmanufacturing} \cdot \pi_{Process} \quad (1.11)$$

where  $\lambda_{Phy}$  is the physical contribution,  $\pi_{Partmanufacturing}$  is a factor representing quality and manufacturing technical control, and  $\pi_{Process}$  covers all processes from specification to field operation and maintenance.  $\lambda_{Phy}$  is expressed as:

#### 1 Introduction

$$\lambda_{Phy} = \left[\sum_{physical contributions} (\lambda_0 \cdot \pi_{acceleration})\right] \cdot \pi_{induced} \quad (1.12)$$

where  $\lambda_0$  is the basic failure rate that depends on the technological characteristics,  $\pi_{acceleration}$  is an environmental acceleration factor vs. use conditions, and  $\pi_{induced}$  is the overstress factor.

#### Limitations

MIL-HDBK-217, as the origin for almost all traditional reliability approaches, has limitations. MIL-HDBK-217 has not been updated since 1995, and most ICs have not been updated since 1991. Therefore, more recent technologies are not included or defined. Table 1.3 shows a comparison and some of the limitations of MIL-HDBK-217, compared to the physics of failure approach [6].

Despite a variety of empirical prediction models, the majority of engineers still use MIL-HDBK-217. A Crane survey shows that almost 80 percent of the respondents use the Military handbook, while PRISM and Telcordia are second and third. Inconsistency among different traditional prediction methods is the main problem facing engineers.

| Issue                                 | Mil-Hdbk-217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Physics of Failure                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Model Development                     | Models can't provide accurate design or manufacturing<br>guidance since they were developed from assumed<br>constant failure-rate data, not root-cause, time-to-failure<br>data. A proponent representative's quote is germane:<br>"Therefore, because of the fragmented nature of the data<br>and the fact that it is often necessary to interpolate or<br>extrapolate from available data when developing new<br>models, no statistical confidence intervals should be<br>associated with the overall model results" [12]. | Models based on science/engineering first principles. Models can<br>support deterministic or probabilistic applications.                                                                                                                                                                                                                                                                          |

| Device Design<br>Modeling             | The Mil-Hdbk-217 assumption of perfect designs is not<br>substantiated due to lack of root-cause analysis of field<br>failures. Mil-Hdbk-217 models do not identify wearout<br>issues.                                                                                                                                                                                                                                                                                                                                       | Models for root-cause failure mechanisms allow explicit of the impact<br>that design, manufacturing, and operation have on reliability.                                                                                                                                                                                                                                                           |

| Device Defect<br>Modeling             | Models can't be used to 1) consider explicitly the impact of manufacturing variation on reliability, or 2) determine what constitutes a <i>defect</i> , or how to screen/inspect <i>defects</i> .                                                                                                                                                                                                                                                                                                                            | Failure mechanism models can be used to 1) relate manufacturing variation to reliability, and 2) determine what constitutes a <i>defect</i> and how to screen/inspect.                                                                                                                                                                                                                            |

| Device Screening                      | Mil-Hdbk-217 promotes and encourages screening without recognition of potential failure mechanisms.                                                                                                                                                                                                                                                                                                                                                                                                                          | Provides a scientific basis for determining the effectiveness of<br>particular screens or inspections.                                                                                                                                                                                                                                                                                            |

| Device Coverage                       | Doesn't cover new devices for approximately the first 5–8 years. Some devices, such as connectors, weren't updated for more than 20 years. Developing and maintaining current design reliability models for devices is an impossible task.                                                                                                                                                                                                                                                                                   | Generally applicable—applies to both existing and new devices—<br>since failure mechanisms are modeled, not devices. Thirty years of<br>reliability physics research has produced and continues to produce<br>peer-reviewed models for the key failure mechanisms applicable to<br>electronic equipment. Automated computer tools exist for printed<br>wiring boards and microelectronic devices. |

| Use of Arrhenius<br>Model             | Indicates to designers that steady-rate temperature is the<br>primary stress designers can reduce to improve reliability.<br>Mil-Hdbk-217 models will not accept explicit temperature<br>change inputs. Mil-Hdbk-217 lumps different acceleration<br>models from various failure mechanisms together, which is<br>unsound.                                                                                                                                                                                                   | The Arrhenius model is used to model the relationships between<br>steady-state temperature and mean time-to-failure for each failure<br>mechanism, as applicable. In addition, stresses due to temperature<br>change, temperature rate of change, and spatial temperature<br>gradients are considered, as applicable.                                                                             |

| Operating<br>Temperature              | Explicitly considers only steady-state temperature. Effect of<br>steady-state temperature is inaccurate because it is not<br>based on root-cause, time-to-failure data.                                                                                                                                                                                                                                                                                                                                                      | The appropriate temperature dependence of each failure mechanism is<br>explicitly considered. Reliability is frequently more sensitive to<br>temperature cycling, provided adequate margins are given against<br>temperature extremes [13].                                                                                                                                                       |

| Operational<br>Temperature<br>Cycling | Does not support explicit consideration of the impact of<br>temperature cycling on reliability. No way of superposing<br>the effects of temperature cycling and vibration.                                                                                                                                                                                                                                                                                                                                                   | Explicitly considers all stresses, including steady-state temperature,<br>temperature change, temperature rate of change, and spatial<br>temperature gradients, as applicable to each root-cause failure<br>mechanism.                                                                                                                                                                            |

| Input Data Required                   | Does not model critical failure contributors, such as<br>materials architectures, and realistic operating stresses.<br>Minimal data in, minimal data out.                                                                                                                                                                                                                                                                                                                                                                    | Information on materials, architectures, and operating stresses—the things that contribute to failures. This information is accessible from the design and manufacturing processes of leading electronic companies.                                                                                                                                                                               |

| Output Data                           | A proponent representative's quote offers some illumination:<br>"Mil-Hdbk-217 is not intended to predict field reliability<br>and, in general, does not do a very good job in an absolute<br>sense" [12].                                                                                                                                                                                                                                                                                                                    | Provides insight to designers on the impact of materials, architectures,<br>loading, and associated variation. Predicts the time-to-failure and<br>failure sites for key failure mechanisms in a device or assembly.<br>These failure times and sites can be ranked. This approach support<br>either deterministic or probabilistic treatment.                                                    |

| DoD/Industry<br>Acceptance            | Mandated by government, 30-year record of discontent. Not<br>part of the US Air Force Avionics Integrity Program<br>(AVIP). No longer supported by senior US Army leaders.                                                                                                                                                                                                                                                                                                                                                   | Represents the best practices of industry.                                                                                                                                                                                                                                                                                                                                                        |

| Coordination                          | Models have never been submitted to appropriate<br>engineering societies and technical journals for formal peer<br>review. Future tri-service coordination at issue.                                                                                                                                                                                                                                                                                                                                                         | Models for root-cause failure mechanisms undergo continuous peer<br>review by leading experts. New software and documentation<br>currently being coordinated with leading electronics companies<br>worldwide, US Army, and AVIP to start.                                                                                                                                                         |

| Relative Cost of<br>Analysis          | Cost is high compared with value added. Can misguide<br>efforts to design reliable electronic equipment.                                                                                                                                                                                                                                                                                                                                                                                                                     | Intent is to focus on root-cause failure mechanisms and sites, which is<br>central to good design and manufacturing. Acquisition flexible, so<br>costs are flexible. The approach can result in reduced life-cycle<br>costs due to higher initial and final reliabilities, reduced probability<br>of failing tests, reductions in <i>hidden factory</i> , and reduced support<br>costs.           |

# Table 1.3. A Comparison between MIL-HDBK-217 and Physics-of-Failure Approach.

## 1.2.2 Physics-of-Failure Approach

Attempts, which began during the 1970s, to include physics-of-failure into military handbooks were not very successful. Although the need for a physics-of-failure methodology was realized in the 1970s, a physics-of-failure-like model for small-scale CMOS technology was not introduced until 1989. Even so, this approach, as an independent methodology, only started to attract attention during the 1990s in the form of recommendations to update the military handbook. The recommendations addressed the weaknesses of traditional approaches: (1) the misleading use of constant physics-of-failure, (2) the use of the Arrhenius temperature model, (3) the modeling of wearout mechanisms, and (4) modeling mechanisms such as brittle die fracture.

The physics-of-failure methodology can be summarized as follows:

- Identify potential failure mechanisms, e.g., chemical, electrical, physical, mechanical, structural, or thermal processes leading to failure, and the failure sites on each device.

- Expose the product to highly accelerated stresses to find the dominant root-cause of failure.

- Identify the dominant failure mechanism as the weakest link.

- Model the dominant mechanism (what and why the failure takes place).

- Combine the data gathered from acceleration tests and statistical distributions, e.g., Weibull distribution, Lognormal distribution.

- Develop an equation for the dominant failure mechanism at the site and its mean time-to-failure (MTTF).

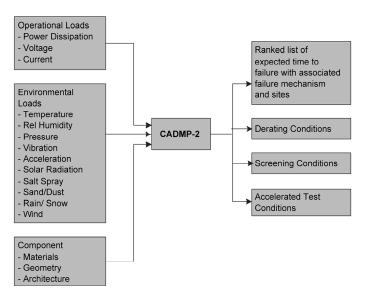

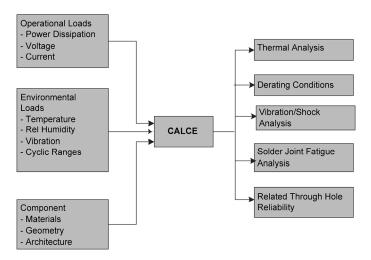

Physics-of-failure modeling and simulation tools are the key elements in this approach. There are two computer-based modeling and simulation tools: Computer-Aided Design of Microelectronic Packages (CADMP-2) and Computer-Aided Life-Cycle Engineering (CALCE). The CADMP-2 assesses the reliability of electronics at the package level; CALCE assesses the reliability of electronics at the package level. Together, these two models provide a framework to support a physics-of-failure approach for reliability in electronic systems design.

The CADMP-2 is a set of integrated software programs that can be used to design and assess the reliability of integrated circuit, hybrid and multi-chip module packages. Figure 1.1 shows the input and output of this software.

The CALCE software provides an environment for incorporating various tools associated with reliability, supportability, producibility, and costing tasks into the design of electronic systems in the earliest stages of the design process. Figure 1.2 shows the inputs and outputs of this software [24]. The main advantage of the physics-of-failure methodology is that contributing failure causes are based on scientific knowledge; that knowledge provides the scientific basis for reliability prediction, incorporating relevant information on materials, architectures, and operating stresses. Moreover, since accelerated stress tests are one of the main methods for finding the degradation model parameters, the test results could help provide the necessary test criteria for the product as well.

Fig. 1.1. CADMP-2 inputs and outputs.

Fig. 1.2. CALCE inputs and outputs.

The objectives of the physics-of-failure methodology are "to develop a physics-of-failure handbook for reliability assurance containing a methodology for assessing system reliability on the basis of environmental and operating stresses, the materials used, and the packaging selected," and "development of mixture models which consider both early and premature wearout failures caused by the displacement of the mean and variability due to manufacturing, assembly, handling, and misapplication" [4]. However, there are some serious challenges in implementing this approach, Ref. Table 1.3.

#### 1.2.3 Recent Approach: RAMP

In 2003, IBM published the Reliability Aware Micro-Processor (RAMP) model for processor reliability. RAMP models chip mean-time-to-failure as a "function of the failure rates of individual structures on the chip due to different failure mechanisms, and can be used to evaluate the reliability implications of different applications, architectural features and processor designs" [25]. In addition, it is claimed that the above-mentioned model is a self-standing module that could be attached to simulators to make power and temperature predictions [13].

In IBM's report, processor errors are classified into two main categories: soft and hard. Hard errors are subclassified into intrinsic and extrinsic failures. RAMP only models intrinsic processor failures because long-term processor reliability is dominated by wearout or intrinsic failures. However, IBM believes that RAMP can be extended to model soft errors.

Although main wearout intrinsic failure mechanisms affecting processors are those related to electromigration, stress migration, time-dependent dielectric breakdown, temperature cycling and hot carrier injection, negative-bias temperature inversion and corrosion, RAMP only considers the first four; however, it could cover the others as well. It should be noted that RAMP uses the Arrhenius model to show the dependence of processor failures on temperature; due to the direct processor reliability relation to the operating temperature, it is expected that many reliability problems are the result of elevated processor temperature.

RAMP uses MTTF to measure reliability. To calculate MTTF, RAMP assumes all failure mechanisms have constant failure rates. This assumption is clearly inaccurate; however, it allows RAMP to combine different failure mechanisms and provides a unified MTTF. Assuming a constant failure rate, the MTTF is calculated as the inverse of the failure rate. The system reliability model used in RAMP is the sum-of-failure-rates model. RAMP treats each structure on a chip as a separate component that can fail in different ways corresponding to various failure mechanisms. The "competing risk model" determines the dominant component failure mechanism, and the "series model" estimates the system failure rate (based on the failure rate of each component).

To calculate the failure rate of a component using the competing risk model, RAMP makes the following assumptions:

- Each failure mechanism proceeds independently of every other, at least until a failure occurs.

- The component fails when the first of all competing failure mechanisms reaches a failure state.

- Each of the failure mechanisms has a known life distribution model.

If there are *k* failure mechanisms and the failure rate of the component due to the *i*<sup>th</sup> failure mechanism is  $\lambda_i(t)$ , then the failure rate of the component due to all failure mechanisms,  $\lambda_C(t)$  is given by:

$$\lambda_C(t) = \sum_{i=1}^k \lambda_i(t) \tag{1.13}$$

In the case where a component has a constant failure rate  $\lambda_C$ , the MTTF for that component is given by:

$$MTTF_C = \frac{1}{\lambda_C} = \frac{1}{\sum_{i=1}^k \lambda_i}$$

(1.14)

where  $\lambda_i$  is the failure rate due to each failure mechanism.

The "series model" is also applied to estimate the systems reliability based on the components. By applying the same set of assumptions used for the "competing risk model," i.e., a system consisting of *j* components fails when the first component fails, the MTTF of the system is given by:

$$MTTF_{SYS} = \frac{1}{\sum_{i=1}^{j} MTTF_{i}} = \frac{1}{\sum_{i=1}^{j} \lambda_{i}} = \frac{1}{\sum_{i=1}^{j} \sum_{l=1}^{k} \lambda_{il}}$$

(1.15)

where  $\lambda_i$  is the failure rate of the *i*<sup>th</sup> component and  $\lambda_{il}$  is the failure rate of the *i*<sup>th</sup> component due to the *l*<sup>th</sup> failure mechanism.

#### **1.3 Reliability Modeling and Prediction Today**

Reliability device simulators have become an integral part of the design process. These simulators successfully model the most significant physical failure mechanisms in modern

electronic devices, such as time-dependent dielectric breakdown (TDDB), negative bias temperature instability (NBTI), electromigration (EM), and hot carrier injection (HCI). These mechanisms are modeled throughout the circuit design process so that the system will operate for a minimum expected useful life.

Modern chips are composed of tens or hundreds of millions of transistors. Hence, chip-level reliability prediction methods are mostly statistical. Today, chip-level reliability prediction tools model the failure probability of the chips at the end of life, when the known wearout mechanisms are expected to dominate. However, modern prediction tools do not predict the random, post burn-in failure rate that can be seen in the field.

Chip and packaged system reliability is measured as rate of failure in time (FIT). The FIT is defined as one failure per billion part hours. The semiconductor industry provides an expected FIT rate for every product that is sold based on operation within the specified conditions of voltage, frequency, heat dissipation, etc. Hence, a system reliability model is a prediction of the expected mean time between failures (MTBF) for an entire system as the reciprocal of the sum of the FIT rates for every component.

The failure rate of a component can be defined in terms of an acceleration factor, AF, as:

$$\lambda = \frac{Number \, of \, failures}{Number \, of \, tested \times hours \times AF} \times 10^9 FIT \tag{1.16}$$

where "Number of failures" and "Number of tested" are the number of actual failures that occurred as a fraction of the total number of units subjected to an accelerated test. The acceleration factor, AF, is generally established by the manufacturer for a given technology and product, as they know the impact of different failure mechanisms on their designs accelerated in the High Temperature Operating Life (HTOL); this information is generally based on a company proprietary variant of the MIL-HDBK-217 approach for accelerated life testing. The true task of reliability modeling, therefore, is to choose an appropriate value for AF based on the physics of the dominant failure mechanisms that would occur in the field for the device.

The HTOL qualification test is usually performed as the final qualification step of a semiconductor manufacturing process. The test consists of stressing some number of parts, usually about 100, for an extended time, usually 1000 hours, at an accelerated voltage and temperature. Two features shed doubt on the accuracy of this procedure. One feature is lack of sufficient statistical data due to too few parts; the second is that manufacturers stress their parts under relatively low stress levels to guarantee zero failures during qualification testing. Unfortunately, with zero failures, little statistical data is acquired.

The accepted approach for measuring FIT would, in theory, be reasonably correct if there is only a single dominant failure mechanism that is excited equally by either voltage or temperature. For example, EM is known to follow Black's equation (described later) and is accelerated by increased stress current in a wire or by increased temperature of the device. If, however, multiple failure mechanisms are responsible for device failures, each failure mechanism should be modeled as an individual "element" in the system and the component survival is modeled as the survival probability of all the "elements" as a function of time.

If multiple failure mechanisms, instead of a single mechanism, are assumed to be timeindependent and independent of each other, FIT (constant failure rate approximation) rates can be a reasonable measure of realistic field failures. Under the assumption of multiple failure mechanisms, each will be accelerated differently, depending on the physics that are responsible for each mechanism. If, however, an HTOL test is performed at an arbitrary voltage and temperature for accelerated only on a single failure mechanism, then only that mechanism will be accelerated. If multiple failure mechanisms with different sensitivity functions to acceleration conditions exist, a choice of only one HTOL test point is biasing the results.

1 Introduction

#### 1.3.1 Competing Mechanisms Theory

Whereas failure-rate qualification has not improved over the years, the semiconductor industry's understanding of the reliability physics of semiconductor devices has advanced enormously. Every known intrinsic wearout failure mechanism is well understood and the processes are so tightly controlled that electronic components are designed to perform with reasonable life and with no single dominant failure mechanism. Standard HTOL tests generally reveal multiple intrinsic failure mechanisms during testing, which would suggest also that no single failure mechanism would dominate the FIT rate in the field. Therefore, in order to derive a more accurate model for FIT, a preferable approximation would be that all failures are equally likely and that the resulting overall failure distribution will resemble a constant failure rate process that is consistent with the military handbook, FIT rate approach.

The acceleration of a single failure mechanism is a highly non-linear function of temperature and/or voltage. The temperature acceleration factor  $(AF_T)$  and voltage acceleration factor  $(AF_V)$  can be calculated separately; this is the subject of most studies concerning reliability physics. The total acceleration factor of the different stress combinations will be the product of the acceleration factors of temperature and voltage.

This acceleration factor model is widely used as the industry standard for device qualification; however, it only approximates a single dielectric breakdown type of failure mechanism and does not correctly predict the acceleration of other mechanisms.

To be even approximately accurate, however, electronic devices should be considered to have several failure modes degrading simultaneously. Each mechanism "competes" with the others to cause an eventual failure. When more than one mechanism exists in a system, the relative acceleration of each one must be defined and averaged at the applied condition. Every potential failure mechanism should be identified and its unique AF should be calculated for each mechanism at a given temperature and voltage so that the FIT rate can be approximated for each mechanism separately, where each mechanism leads to an expected failure unit per mechanism,  $FIT_i$ . Unfortunately, again, individual failure mechanisms are not uniformly accelerated by a standard

HTOL test, and the manufacturer is forced to model a single acceleration factor that cannot be combined with the known physics-of-failure models.

The history of reliability prediction of microelectronic devices can be categorized into two distinct phases:

- 1. The first phase relied on traditional methods, or empirical models. These traditional methods are based on the data gathered either from laboratory tests or fielded applications; the statistical curve fitting of the component failure data provides the required mathematical model. Depending on the specific sources and environment used to collect the data, the models provide predictions for the relevant area. Due to data diversities, the predictions are different as well. Almost all of the procedures are based on the data gathered from the field with extrapolation from devices that are similar to each other. These procedures model past experience and data to estimate the reliability of similar or modified products and to deal with the early defects and random events.

- 2. The second phase, physics-of-failure, is an approach that uses the "knowledge of the root-cause failure mechanism" [14]. This approach tries to bring the prediction to increased scientific accuracy. Physics-of-failure focuses on device end-of-life failure mechanisms. Unlike traditional methodologies, this approach studies the impact of different parameters on single-device wearout mode.

Combining these two methodologies can develop into a powerful framework for predicting microelectronic device reliability.

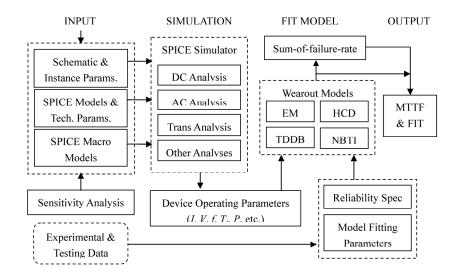

# 1.3.2 FaRBS

FaRBS (Failure-Rate-Based SPICE [spacecraft, planet, instrument, C-matrix, events]) [15] is a circuit-level simulation method that is based on the physics-of-failure and sum-of-failure-rates (SOFR) models. It combines the modules of SPICE (simulation program with integrated circuit emphasis), semiconductor wearout models, integrated circuit system reliability models, accelerated

factor models, and the SOFR reliability model. The FaRBS simulation methodology is presented in Chapter 3.

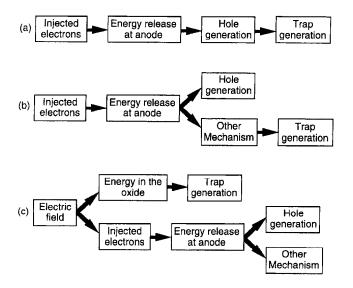

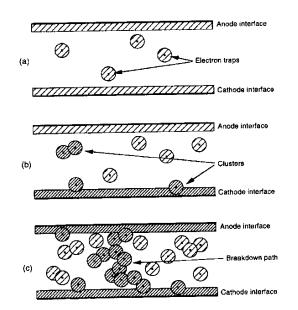

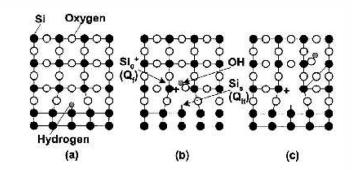

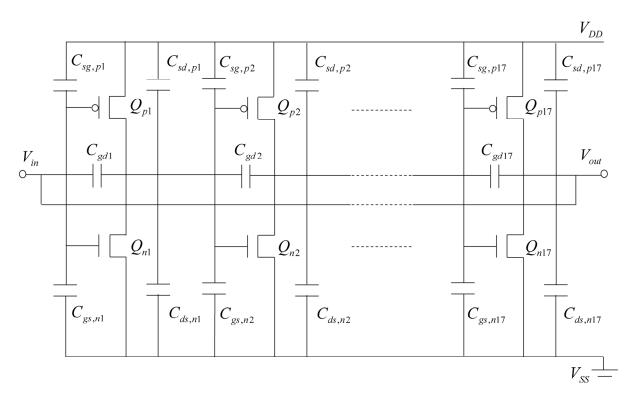

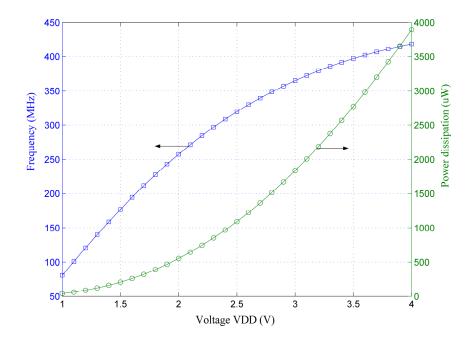

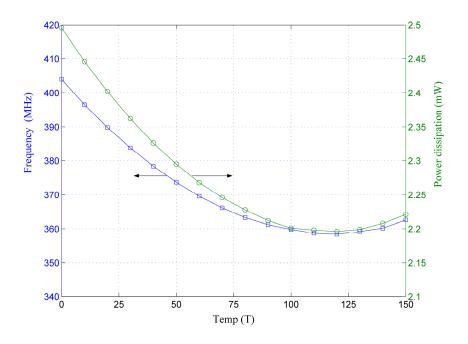

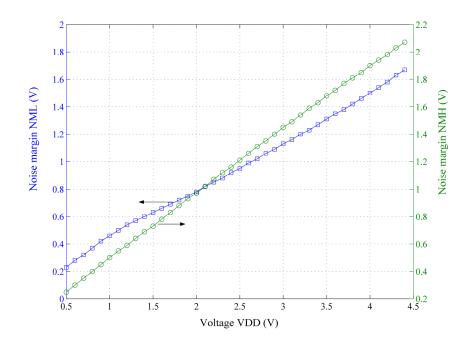

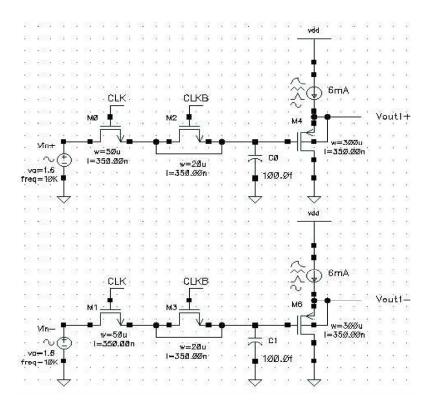

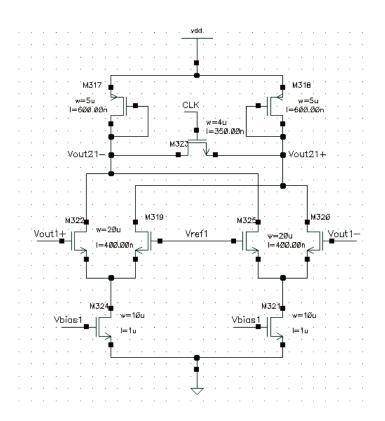

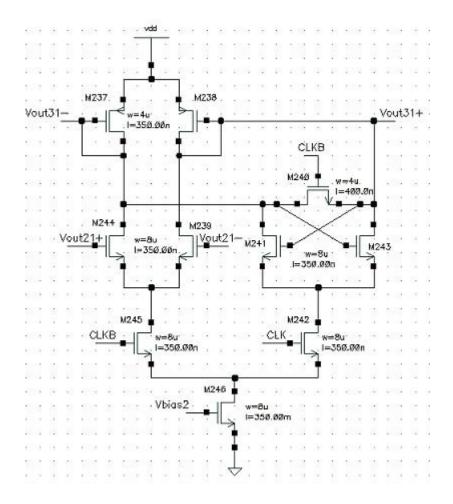

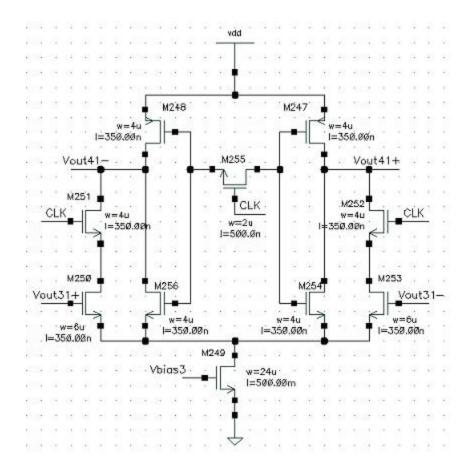

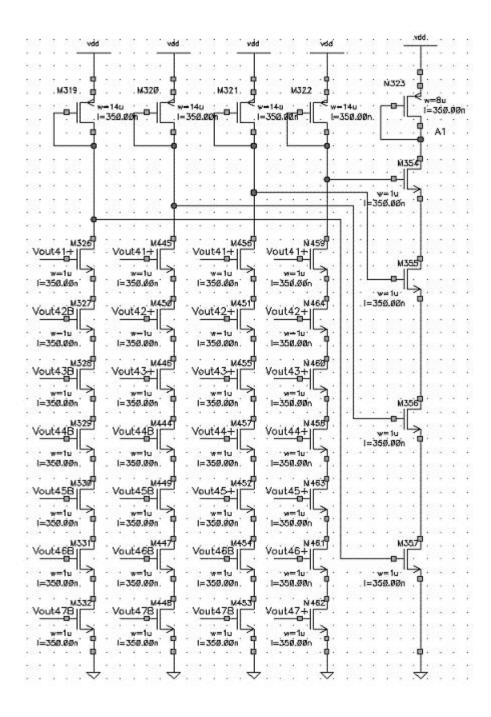

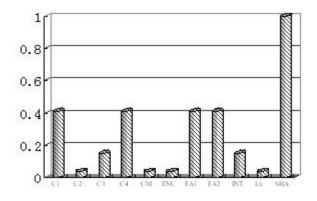

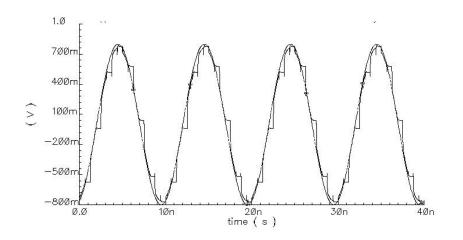

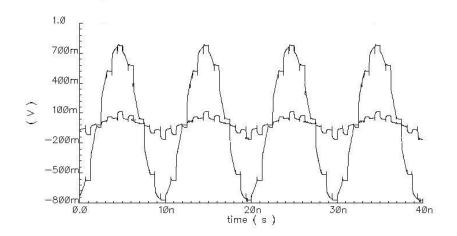

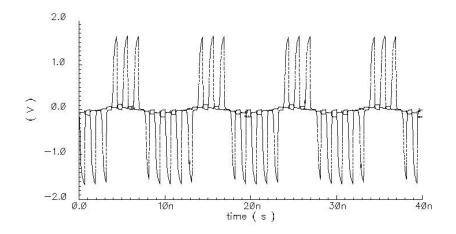

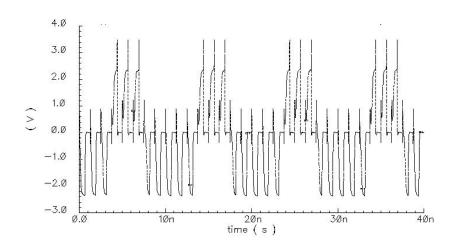

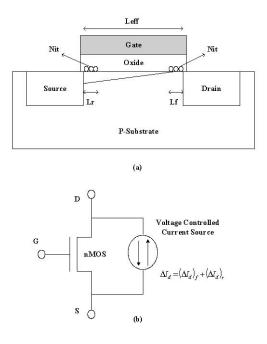

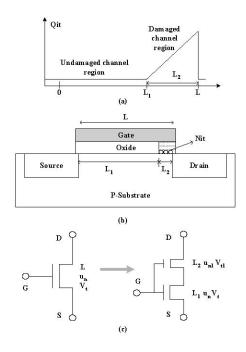

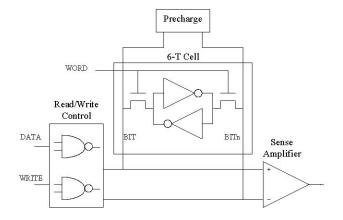

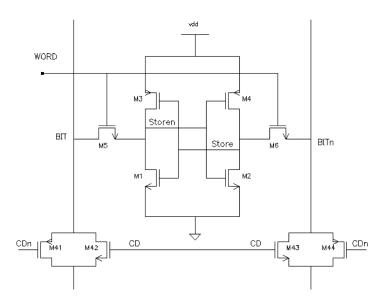

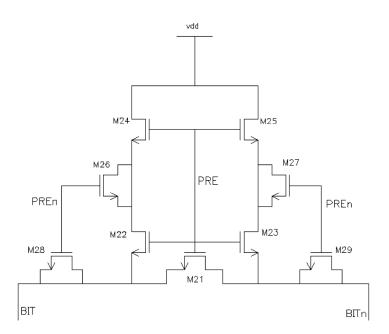

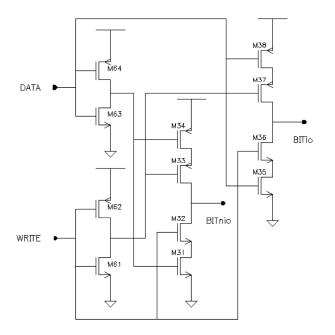

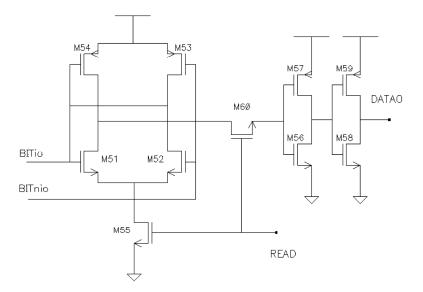

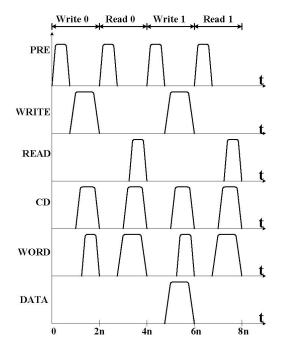

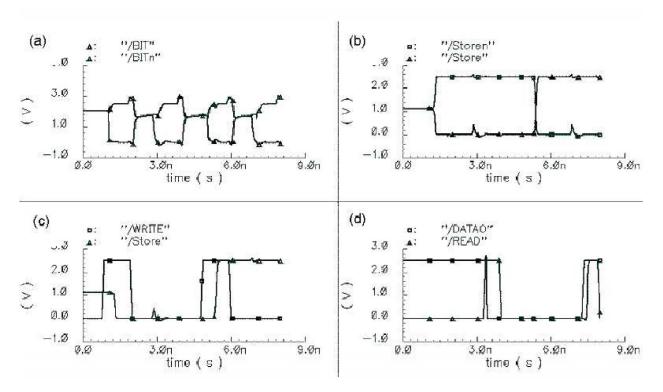

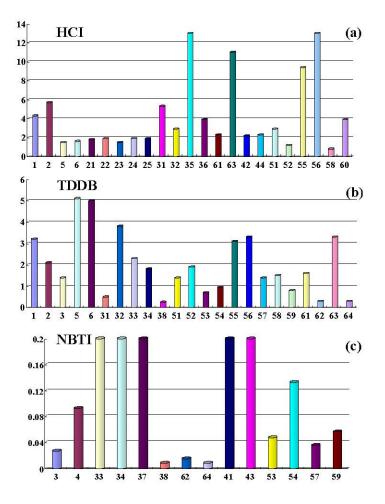

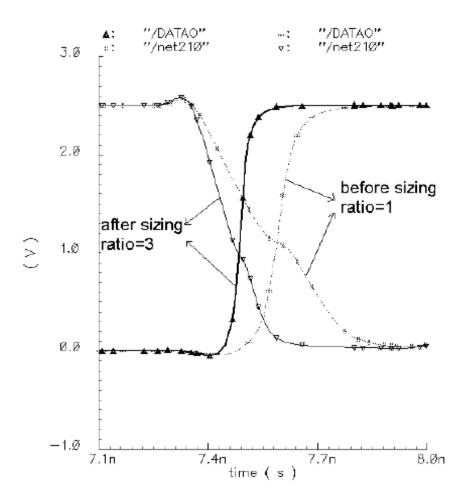

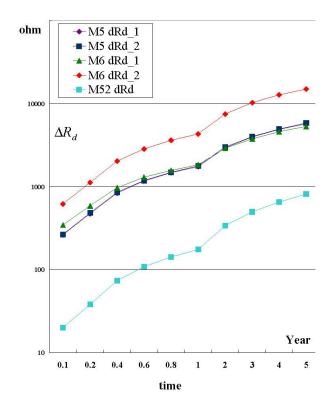

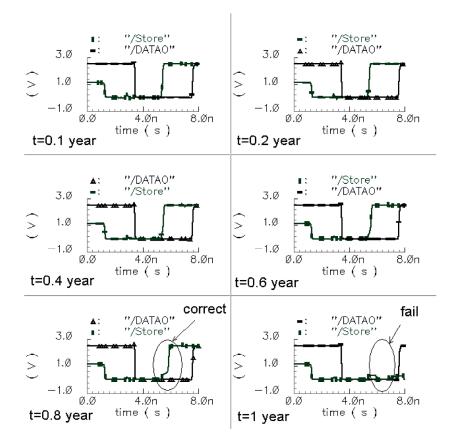

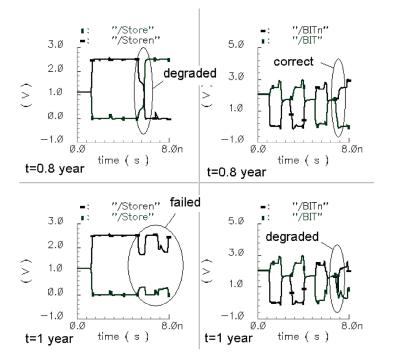

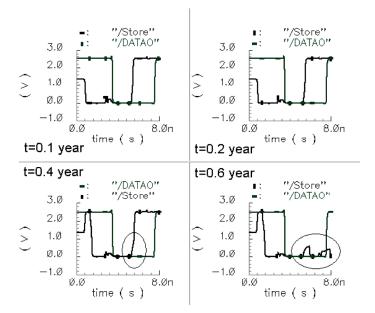

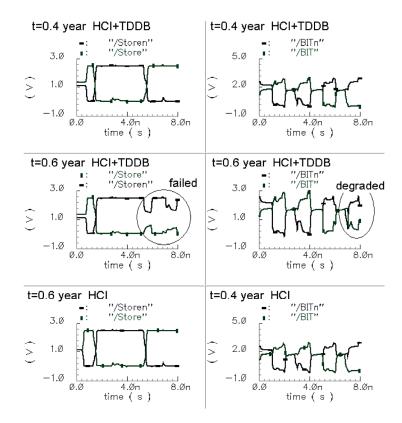

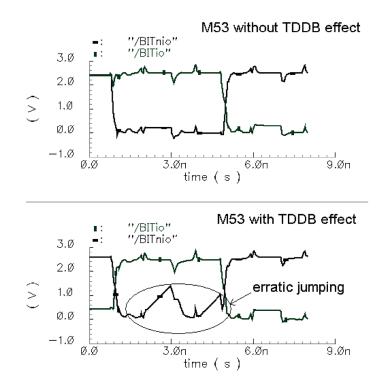

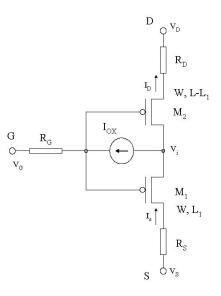

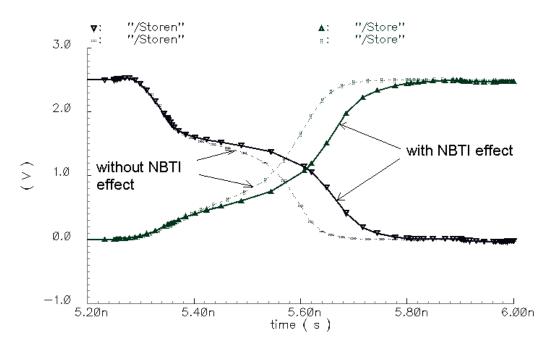

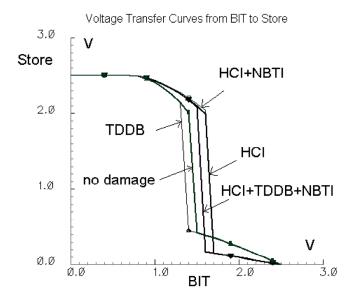

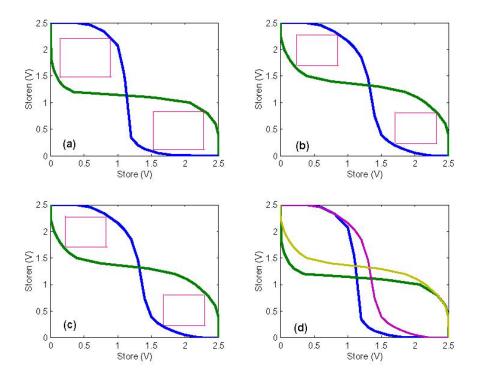

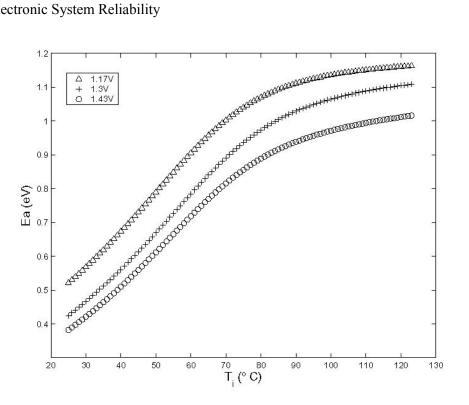

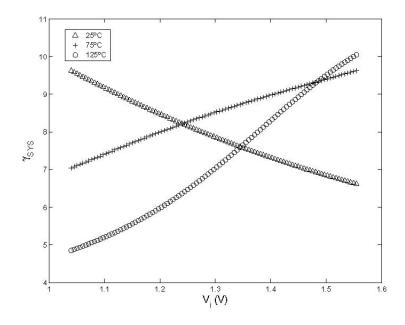

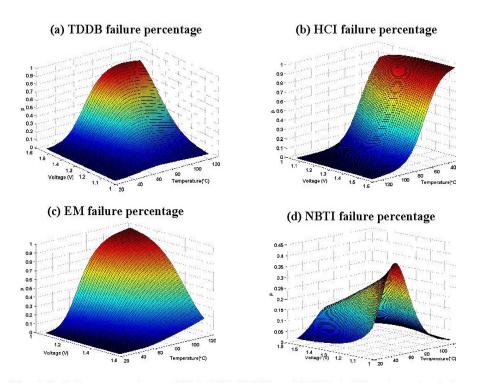

## 1.3.3 MaCRO