# Reliability of FPGA Assemblies Pb/Sn & Pb-free Solders Tested per IPC 9701A

## Reza Ghaffarian, Ph.D.

NASA-Jet Propulsion Laboratory, Caltech (818) 354-2059

Reza.Ghaffarian@JPL.NASA.Gov

Military and Aerospace FPGA Applications (MAFA) Meeting November 2007

## • Reliability

- Reliability definition

- IPC 9701A SMT Attachment Reliability

- Relative thermal cycle data Pb-free/SnPb

- Thermal Cycle Data for PBGA 676 I/O

- Celestica's test data using RIA3

- Solectron/industry- effect of dwell time

- o Xilinx

- Why different results using IPC 9701A?

- JPL preliminary data using RIA3 TVs & Future Joint Activities

- Other Current Activities

What is Reliability

"Reliability is the ability to function as expected under the expected operating conditions for an expected time period without exceeding expected failure levels"

- IPC 9701, Released Jan 2002

- IPC SM785- Guideline

- No answer to the question of data for product application

- Data comparison

- IPC 9701

- Details on thermal cycle test and acceptance

- Key Controls

- Surface finish (OSP, HASL), thickness, 93 mil, NSMD, continuous monitoring, etc.

- Five Cycle Conditions

- Preference 0/100°C

- Five number of thermal cycles

- Preference 6,000 cycles

IPC 9701- "Performance Test Methods and Qualification Requirements for Surface Mount Solder Attachments"

| Test Condition                                                                                                  |     | Mandated Condition                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature Cycle (TC) Condition:<br>TC2<br>TC3<br>TC4<br>TC 5                                                  | TC1 | $0^{\circ} \leftrightarrow +100^{\circ} (Preferred Reference)$<br>$-25^{\circ} \leftrightarrow +100^{\circ}$<br>$-40^{\circ} \leftrightarrow +125^{\circ}$<br>$-55^{\circ} \leftrightarrow +125^{\circ}$<br>$-55^{\circ} \sim ->100^{\circ}$                |

| Test Duration<br>Number of Thermal Cycle (NTC)<br>Requirement: NTC-A<br>NTC-B<br>NTC-C<br>NTC-D<br><i>NTC-E</i> |     | Whichever condition occurs FIRST: 50% (preferred 63.2%)<br>cumulative failure (Preferred Reference Test Duration) or<br>200 cycles<br>500 cycles<br>1,000 cycles (Preferred for TC2, TC3,and TC4)<br>3,000 cycles<br>6,000 cycles (Preferred Reference TC1) |

| Low Temperature Dwell<br>Temp. tolerance (preferred)<br>High Temperature Dwell<br>Temp. tolerance (preferred)   |     | 10 minutes<br>+0/−10℃ (+0/ −5℃) [+0 /−18뚜 (+0/ −9℉)]<br>10 minutes<br>+10/−0°C (+5/−0°C) [+18/−0뚜(+9/ −0℉)]                                                                                                                                                 |

### Table 1 Temperature cycling requirements specified in Table 4.1 of IPC 9701

# Pb-free Guideline- IPC 9701A-Appendix B

- IPC 9701A, Pb-free guideline- Released 2006

- Appendix B, "Guideline for Thermal Cycle Requirements for Leadfree Solder Joints"

- Moisture sensitivity, use J-STD-020

- Reference to several models

- Details to be covered in IPC 9706

- Release delayed due to lack of data on dwell- 2 dwells

- D10 (10 minute dwell)

- Most efficient

- Use as "stand-alone", only when modeling understood could be theoretically compared to tin-lead

- D30+ (30 minutes or higher)- To experimentally induce damage somewhat comparable to tin-lead

- Surface finish

- Only OSP, IAg

- Requalification is required when

- Solder paste change

- Lead terminal change

### Effect of Area Array Package Types on Assembly Reliability and Comments on IPC-9701A

Reza Ghaffarian, Ph.D. Jet Propulsion Laboratory, California Institute of Technology Pasadena, CA

Back-up information for IPC-9701A Discussion on Key Thermal Cycle Parameters and Projection for Lead-Free Vs Lead-Based Solder Joints

The appendix B of IPC-9701A establishes guidelines for modifications required to IPC-9701 for lead-free solder joints. Currently, there are only limited data and insight to determine acceleration factors and acceleration models for lead-free solders [1-13]. Data on the impact of various thermal cycle profiles on the results of accelerated testing in comparison to eutectic tin-lead solder are still being gathered by industry.

Acceleration thermal cycle test results especially when are compared to lead-free solder alloys are sometimes inaccurately assumed to be the same as product reliability. Correlations between acceleration test and product reliability for tin-lead are somewhat have been established during many years of investigation and product use whereas that is not true for less understood lead-free solder attachment. Reliability is the ability of a product, here surface mount solder attachments, to function under given conditions and for a specified period of time without exceeding acceptable failure levels. Therefore, comments such as a lead-free solder joint is more or less reliable than standard tin-lead solder joint based on only laboratory test results are unsubstantiated. Such general statements are incomplete when the lead-free alloy composition or/and when product information and use conditions are not specified. Product reliability needs to be estimated for solder joint under relevant use conditions.

### Ref: APEX 2006 MAFA 2007

Reza Ghaffarian

### QUALIFICATION OF A LEAD-FREE CARD ASSEMBLY AND TEST PROCESS FOR A SERVER COMPLEXITY PCBA

Matthew Kelly<sup>1</sup>, Marie Cole<sup>2</sup>, Jim Wilcox<sup>3</sup>, Jim Bielick<sup>4</sup>, Timothy Younger<sup>4</sup>, David Braun<sup>4</sup> IBM Corporation <sup>1</sup>Toronto, Canada; <sup>2</sup>Hopewell Junction, NY, USA; <sup>3</sup>Endicott, NY, USA; <sup>4</sup>Rochester, MN, USA

ATC: Accelerated Thermal Cycling. 0-100C. Visual inspection and functional test conducted every 250 cycles. Following IPC 9701 thermal profile protocol.

#### IMPACT OF AGING AND STORAGE CONDITIONS OF OSP PCBs ON BGA SOLDER JOINT RELIABILITY

Bala Nandagopal, Sue Teng and Mason Hu Manufacturing Technology Group Cisco Systems, Inc. San Jose, CA, USA

The boards were subjected to Accelerated Thermal Cycling (ATC) of  $-40/125^{\circ}$ C with 20 minute ramps and 10 minute dwells per IPC9701. The characteristic life ( $\eta$ ) results

#### EFFECT OF TEMPERATURE CYCLING PARAMETERS ON THE SOLDER JOINT RELIABILITY OF A Pb-FREE PBGA PACKAGE

John Manock<sup>1</sup>, Richard Coyle<sup>1</sup>, Brian Vaccaro<sup>2</sup>, Heather McCormick<sup>3</sup>, Richard Popowich<sup>1</sup>, Debra Fleming<sup>1</sup>, Peter Read<sup>1</sup>, John Osenbach<sup>2</sup>, and Dan Gerlach<sup>2</sup> <sup>1</sup>Alcatel-Lucent, Murray Hill, NJ, USA; <sup>2</sup>LSI Corp., Allentown, PA, USA; <sup>3</sup>Celestica Inc., Toronto, ON, Canada jmanock@alcatel-lucent.com and rcoyle1@alcatel-lucent.com

of SnAgCu (SAC) and SnPb solder assemblies using typical IPC-9701 est conditions for accelerated temperature cycling (ATC) [1]. In the previous study, a temperature range of 0°C to 100°C with 10 minute dwell times was used.

**MAFA 2007**

### COMPARISON OF THE LEVEL 2 CHARACTERISTICS OF HITCE™ SUBSTRATE ASSEMBLED WITH SAC AND HIGH LEAD BALLS

Nicole Butel Avago Technologies, Inc. ASIC Products Division Fort Collins, CO, USA nicole.butel@avagotech.com

For IPC9701, forty two assemblies for each leg were thermally cycled between 0°C and 100°C per IPC 9701.

#### SECOND LEVEL SOLDER JOINT RELIABILITY OF QUAD FLAT NO-LEAE (QFN) PACKAGES FOR USE IN IPC CLASS-2 ASSEMBLIES

Alex Chan Alcatel-Lucent Canada Inc. Kanata, ON, Canada Alex.l.Chan@alcatel-lucent.com

Aman Khan, Ph.D. Product Quality Engineer International Rectifier Temecula, CA, USA akhan1@irf.com

Robert Kinyanjui, Ph.D. Technology Development Center Sanmina-SCI Corporation Huntsville, AL, USA robert.kinyanjui@sanmina-sci.com

limited data is available that addresses the telecommunication application requirements per the IPC9701 specification under the TC1 test condition.

### BOARD LEVEL RELIABILITY OF LEAD-FREE SOLDERED INTERCONNECTS - TEST METHODS

H.-J. Albrecht, M. Heimann, Ch. Götze, and M. Löffler Siemens AG Berlin, Germany hans-juergen.albrecht@siemens.com

Temperature cycling test conditions should be consistent with the IPC 9701 specification. Here are different test conditions applied to study the performance of lead-free

- Celestica International Inc, Toronto, Canada

- Solectron/Sun Microsystems

- Xilinx, Inc

- NASA-JPL

**MAFA 2007**

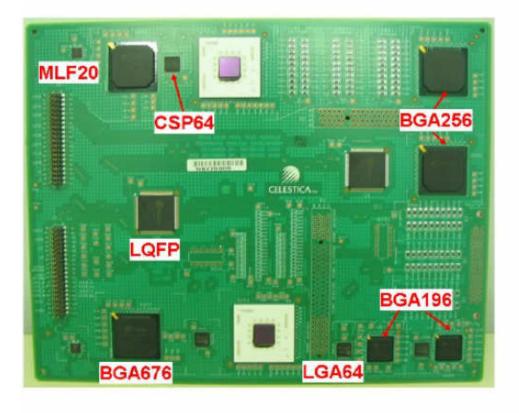

# Thermal Cycle Test- Celestica RIA3

'12 layer boards

'203 mm x 253 mm x 2.36 mm

'Lead-free compatible

laminate material

'Board finish – ENIG

(Electroless Ni / Immersion Au)

### Table 3. Solder composition

|    | SAC 305 pa | ste                   | SAC 405 paste |                       |        |  |  |  |  |  |  |

|----|------------|-----------------------|---------------|-----------------------|--------|--|--|--|--|--|--|

| Re | quirements | Compo<br>sition,<br>% | Req           | Compo<br>sition,<br>% |        |  |  |  |  |  |  |

| Ag | 3.0±0.2%   | 3.0                   | Ag            | 3.9±0.2%              | 4.0    |  |  |  |  |  |  |

| Cu | 0.5±0.1%   | 0.5                   | Cu            | $0.6 \pm 0.2$         | 0.6    |  |  |  |  |  |  |

| Zn | <0.002%    | 0.001                 | Zn            | <0.002%               | 0.001  |  |  |  |  |  |  |

| Al | <0.002%    | 0.000                 | Al            | <0.002%               | 0.000  |  |  |  |  |  |  |

| Sb | <0.12%     | 0.00                  | Sb            | <0.12%                | 0.00   |  |  |  |  |  |  |

| Fe | <0.02%     | 0.00                  | Fe            | <0.02%                | 0.00   |  |  |  |  |  |  |

| As | <0.03%     | 0.00                  | As            | <0.03%                | 0.00   |  |  |  |  |  |  |

| Cd | 0.002%     | 0.000                 | Cd            | 0.002%                | 0.000  |  |  |  |  |  |  |

| Pb | <0.050%    | 0.006                 | Pb            | <0.050%               | 0.004  |  |  |  |  |  |  |

| Bi | <0.10%     | 0.01                  | Bi            | <0.10%                | 0.01   |  |  |  |  |  |  |

| Sn | Remainder  | Remain                | Sn            | Remainder             | Remain |  |  |  |  |  |  |

- 405 balls/405 Paste, 305 balls/305 Paste

- Two thermal cycles

- 0-100C 60 min, 15 min dwells, 15 min ramp/cool

- -55 -100C, 60 min, 15 min dwells, 15 min ramp/cool

- Failure- 5 consecutive with ≥ 20% relative to its hot as-built resistance

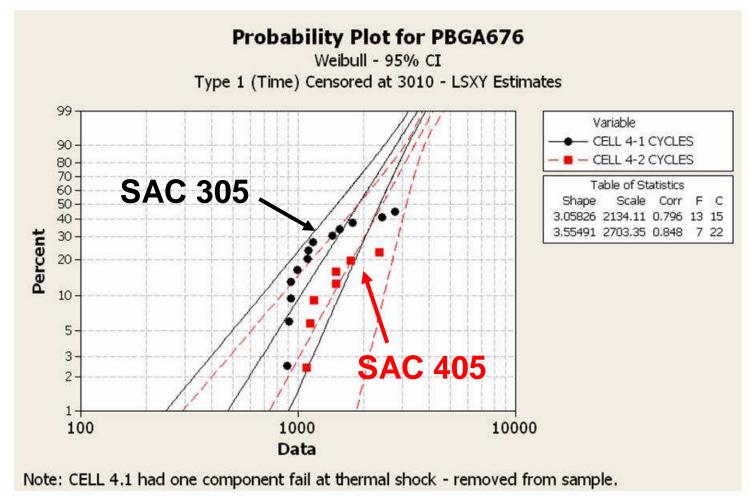

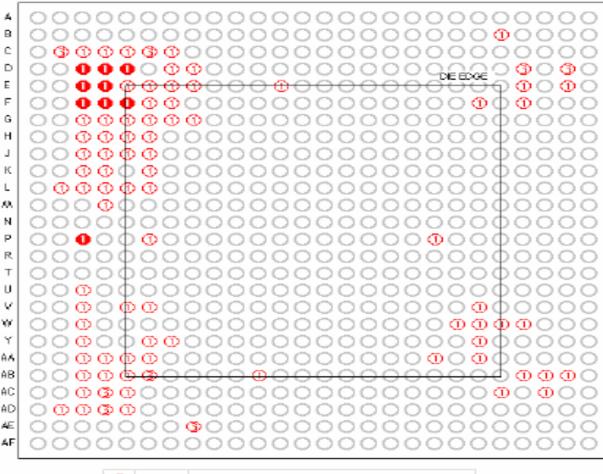

## 0-100C, SAC 305, 7 failures <2,500, 5400, 5800 cycles 0-100C, SAC 405, 7 failures <1,500, No failures to 6,000

**MAFA 2007**

Ref: Celestica SMTA 2006

Reza Ghaffarian

|    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | ]  |     |         |          |       |                          |

|----|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|---------|----------|-------|--------------------------|

| A  |   |   | 6 | 5 |   | 4 |   | 4 |   |    | 4  | 5  | 4  | 4  | 5  | 4  | 5  |    | 6  | 5  | 6  | 5  | 5  | 3  | 6  | 4  | A  |     |         |          |       |                          |

| в  |   |   | 5 | 5 | 5 | 4 | 5 |   |   |    |    | 4  |    | 5  | 5  | 4  |    | 5  | 6  | 4  | 4  | 5  | 5  | 4  | 5  | 5  | в  |     |         |          |       |                          |

| с  |   |   | 5 | 5 | 6 | 3 | 5 | 4 |   | 4  | 5  | 5  | 5  | 5  | 6  | 5  |    | 6  |    |    | 6  | 6  | 6  | 6  | 6  | 3  | с  |     |         |          |       |                          |

| D  | 6 | 5 |   |   |   | 4 | 5 | Γ | Γ | 5  | 5  | 4  | 4  | 5  |    | 5  | 5  |    |    |    |    |    | 6  | 6  | 6  | 4  | D  |     |         |          |       |                          |

| Ε  | 6 | 6 |   | 4 | 6 |   | 5 | 5 |   | 5  |    |    |    |    | 4  |    | 4  | 3  |    | 5  | 4  |    |    | 6  | 6  | 4  | Ε  |     |         |          |       |                          |

| F  | 6 |   | 6 | 4 | 4 |   |   | 4 |   |    | 5  | 5  | 5  |    | 5  | 4  | 5  |    |    |    |    |    | 5  |    |    | 5  | F  |     |         |          |       |                          |

| G  |   |   | 4 | 5 |   |   |   |   |   |    |    | 3  | 5  | 4  | 5  |    |    | 4  |    |    | 5  | 4  | 5  | 6  | 4  |    | G  |     | E/      |          | 400   |                          |

| н  |   |   |   |   |   |   |   |   | 3 |    | 4  | 5  |    | 4  |    |    |    | 6  |    |    |    |    |    |    | 6  | 4  | н  |     | EG      | 64 I/O = | 196   |                          |

| J  |   |   |   |   |   |   |   |   |   |    | 4  |    |    | 4  |    |    |    |    |    |    |    |    |    |    |    |    | J  |     |         |          | ~ .   |                          |

| к  |   |   |   |   |   |   |   |   |   |    |    | 5  |    |    | 4  |    |    |    |    |    |    |    |    |    | 6  |    | к  |     | Failure | # of     | % of  | % Fractured - Cye        |

| L  | 6 |   |   |   |   |   |   |   |   |    | 3  | 4  | 4  | 4  |    | 3  | 4  | 3  |    |    |    |    |    |    |    |    | L  |     | Mode    | Sites    | Sites | ·····                    |

| м  | 4 | 5 | 6 |   |   |   |   |   |   |    | 5  | 3  | 3  |    |    | 3  |    |    |    | 5  |    |    |    | 4  | 4  |    | Σ  |     | 1       | C        | 0%    | 1 = Open                 |

| н  | 4 |   | 4 | 3 | 5 |   | 6 |   |   | 4  | 4  |    |    |    |    |    |    |    |    |    |    |    |    | 3  |    |    | ы  |     | 2       | 5        | 1%    | 2 = 71-90%               |

| Ρ  | 4 |   | 5 | 4 |   |   |   | 6 | 4 |    | 5  | 5  | 5  | 6  | 5  | 5  |    | 4  |    | 4  | 6  | з  | 5  | 5  | 6  |    | Ρ  |     | 3       | ſ        | 0%    | 3 = 51-70%               |

| R  | 5 | 6 | 5 | 6 | 6 |   | 4 |   |   |    | 2  | 4  |    | 5  | 6  | 5  | 4  | 5  | 5  | 5  |    | 5  |    |    |    | 4  | R  |     | 1       | ſ        | 0%    | 4 = 31-50%               |

| т  | 6 | 5 | 4 | 5 |   | 6 | 6 |   |   | 5  | 3  | 4  |    | 5  | 3  | 4  |    | 4  |    | 6  | 4  |    |    |    | 5  | 4  | т  |     | 5       | c c      | 0%    | 4 = 51-30%<br>5 = 11-30% |

| υ  | 5 | 6 | 5 | 5 | 5 | 5 |   | 4 | 4 | 4  | 4  |    |    | 4  | 4  | 4  |    | 4  | 5  | 6  |    |    |    |    |    |    | υ  |     | -       | د<br>ج   | 1%    |                          |

| Ŷ  | 5 |   | 5 | 6 |   | 5 | 4 |   |   | 4  | 5  | 4  |    | 5  |    |    | 4  | 4  |    | з  | 4  | 4  | 6  | 5  |    | 4  | Ŷ  |     | 6       | 2        | 1.70  | 6 = 1-10%                |

| W  |   |   |   |   | 5 | 3 |   | 5 | 4 | 6  | 6  |    | 5  | 6  | 5  | 5  | 5  | 5  | 5  |    | 5  |    |    | 4  |    |    | 3  |     |         |          |       |                          |

| Y  | 5 | 6 |   |   | 4 | 4 | 6 |   | 5 | 5  | 5  | 4  | 4  |    | 5  |    | 5  | 5  | 5  | 5  | 4  |    | 6  | 5  | 5  | з  | Y  |     |         |          |       |                          |

| AA | 4 | 6 | 5 | 5 | 3 |   |   | 5 |   |    |    |    |    |    |    |    | 5  | 5  |    | 5  |    | 4  |    | 4  | 4  | з  | AA |     |         |          |       |                          |

| AB | 5 | 6 |   |   | 4 | 4 | 6 | 5 | 5 | 5  | 5  | 4  | 5  | 3  | 5  |    |    |    | 5  |    |    | 5  | 5  | 4  | 5  | 5  | AB |     |         |          |       |                          |

| AC |   | 6 |   | 5 | 4 |   | 6 |   | 5 |    |    | 5  | 5  | 5  | 5  |    |    | 6  |    | 4  |    | 6  | 4  | 4  | 5  | з  | AC |     |         |          |       |                          |

| AD |   | 6 |   | 5 |   | 6 |   | 6 |   | 5  | 6  | 4  |    |    |    |    |    |    | 6  |    |    | 5  |    |    | 5  | 4  | AD |     |         |          |       |                          |

| AE | 4 | 6 | 6 | 5 | 6 | 4 |   |   |   | 5  | 4  | 6  | 5  | 6  |    |    | 6  | 4  |    |    |    |    |    |    |    | 5  | AE |     |         |          |       |                          |

| AF | 5 | 6 | 6 | 6 |   | 6 |   | 5 |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 3  | 4  | AF |     |         |          |       |                          |

|    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 |    |     |         |          |       |                          |

|    |   |   |   |   | Ň |   |   | ŀ |   |    |    |    |    | ß  |    |    | ł  |    |    |    |    | j  |    | 22 |    |    |    | BUT | D       | P        |       |                          |

Present

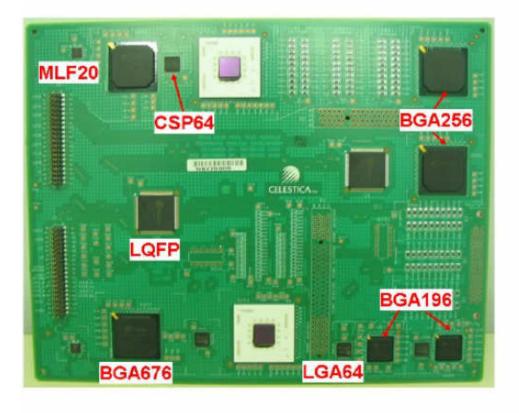

# Thermal Cycle Test- Celestica RIA3

'12 layer boards

'203 mm x 253 mm x 2.36 mm

'Lead-free compatible

laminate material

'Board finish – ENIG

(Electroless Ni / Immersion Au)

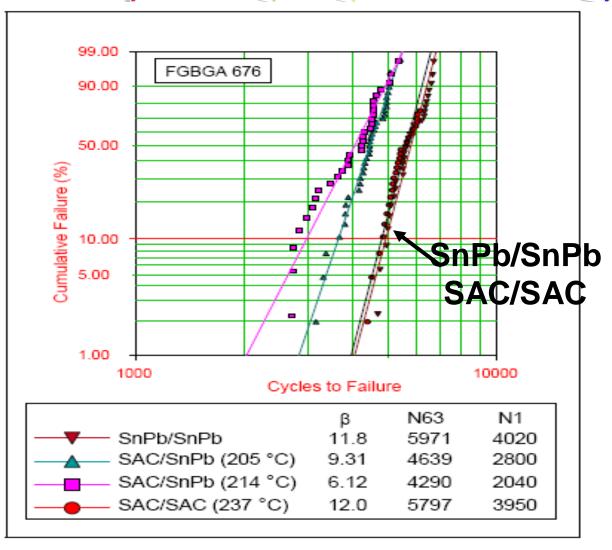

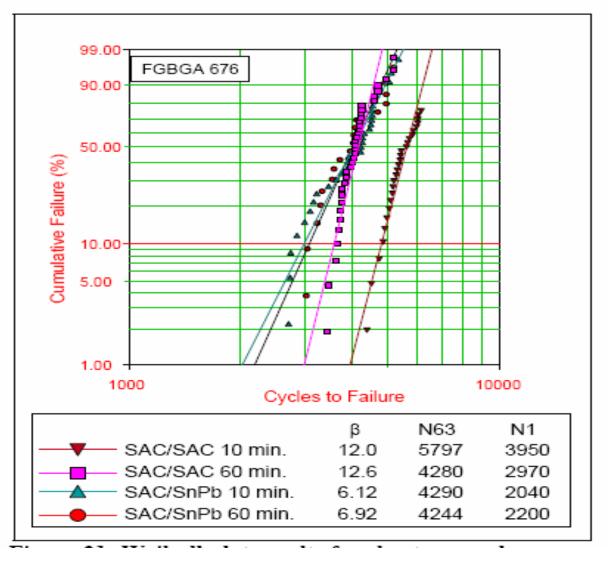

# Thermal Cycle Results (0-100C)- Solectron/Sun Microsystems

0-100C, 40 min (10 min dwells, 10 min ramp/cool)

**MAFA 2007**

**MAFA 2007**

| Electrical (High and Low Temperatures) | Continuous intermittent event monitoring (preferred reference)                                                                       |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                                        | OR                                                                                                                                   |

|                                        | Continuous electrical resistance monitoring (maximum scan interval of all chains =<br>one minute). Manual monitoring is not allowed. |

| Failure Definition                     | Event detector: 1000 $\Omega$ , 10 events (maximum), 1 micro-second duration (maximum), report first verified as time-to-failure     |

|                                        | AND/OR                                                                                                                               |

|                                        | Data logger/Voltmeter: 20% nominal resistance increase (maximum), five readings/<br>scans (maximum)                                  |

## **Failure Definition:**

**Celestica**: 20% increase and event detector **Solectron/Sun**: Event detector, not specified failure **Xilinx**: Event detector, >500 ohms

# New Data for RIA3 In Harsh Environment JPL

- JPL's Preliminary TC results using Celestica's RIA3 405/405. No failures to:

- ~ 200 cycle (-130/85°C), 4 parts

- ~ 200 cycles (-55°/125°C), 6 parts

- ~ 200 cycles (-55°/100°C), 8 parts

## • Pb-free vs SnPb

- Mild  $(0^{\circ}/100^{\circ}C)$  probably the same Solectron, Xilinx/Celestica?

- Harsh (-55°/125°C) SnPb>Pb-free? Xilinx & Celestica?

- Remember- Electrical failure earlier than Dye & pry failure

## • Future Activities

- Rework PBGA 676 I/Os in 305/305

- Include 305/305 assemblies into test matrix

- Test more RIA3 in harsh environment

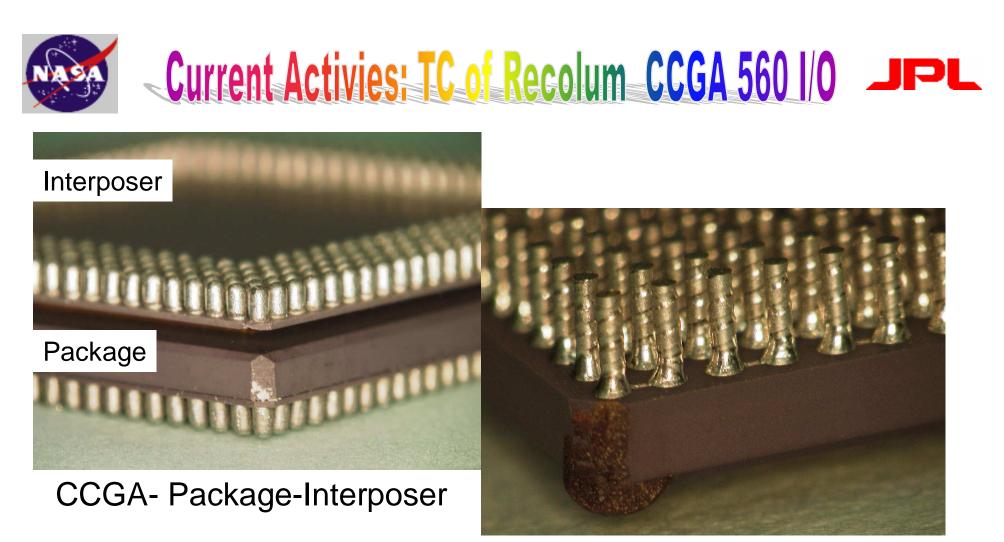

## **Recolumn Six Sigma Column**

SEE: Microelectronics Quality and Reliability Workshop MRQW – Dec 4-5, 2007

**MAFA 2007**

Reza Ghaffarian

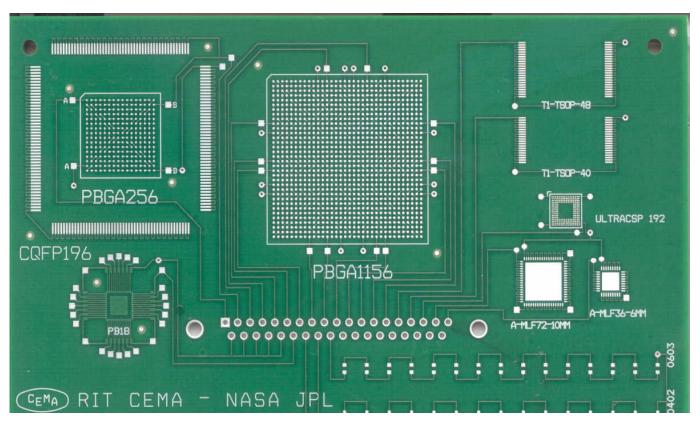

# Current Activitie: Rel of High I/O & Low Pitch

### EFFECT OF FORWARD & BACKWARD COMPATIBILITY OF SOLDER PASTE & COMPONENT FINISH ON FINE-PITCH COMPONENT ASSEMBLIES USING ENIG AND IMAG PWB FINISHES

Anand Kannabiran, Sreekanth Varma Penmatsa and S. Manian Ramkumar Center for Electronics Manufacturing and Assembly **Reza Ghaffarian** Jet Propulsion Laboratory California Institute of Technology

## **ASME-InterPACK 2007**

**MAFA 2007**

Rıza Yhaffarian

The research described in this publication is being conducted at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration.

The author would like to acknowledge Celestica's team especially I. Sterian and S. Bagheri for providing RIA3 test vehicles. The author extends his appreciation to program managers at NASA Electronic Parts and Packaging Program (NEPP) including M. Sampson & K. LaBel, Dr. C. Barnes, and P. Zulueta for their continuous support and encouragement.