# Computational Modeling Using FDTD Methods on Reconfigurable Co-Processor Platform

Robert Weir and Xinming Huang Embedded Computing Lab Email: rweir@wpi.edu

#### Introduction

As modern microprocessors reach their physical limits, engineers have begun investigating other approaches to improving performance since there continues to be a demand for faster computing systems, particularly in applications involving complex simulations and equations. In early computing systems, math coprocessors were added to improve the mathematical performance of microprocessors.

This project aims to revisit that idea by using a re-configurable hardware device known as a Field Programmable Gate Arrays (FPGA) as a coprocessor in conjunction with a modern microprocessor. Although FPGAs operate at a significantly lower frequency than modern microprocessors, they offer the ability to perform several operations in parallel that would ordinarily execute sequentially on a microprocessor. This allows FPGAs to overcome their slower clock rate by instantiating several "pieces" of hardware in parallel that are specifically tailored for the designer's application.

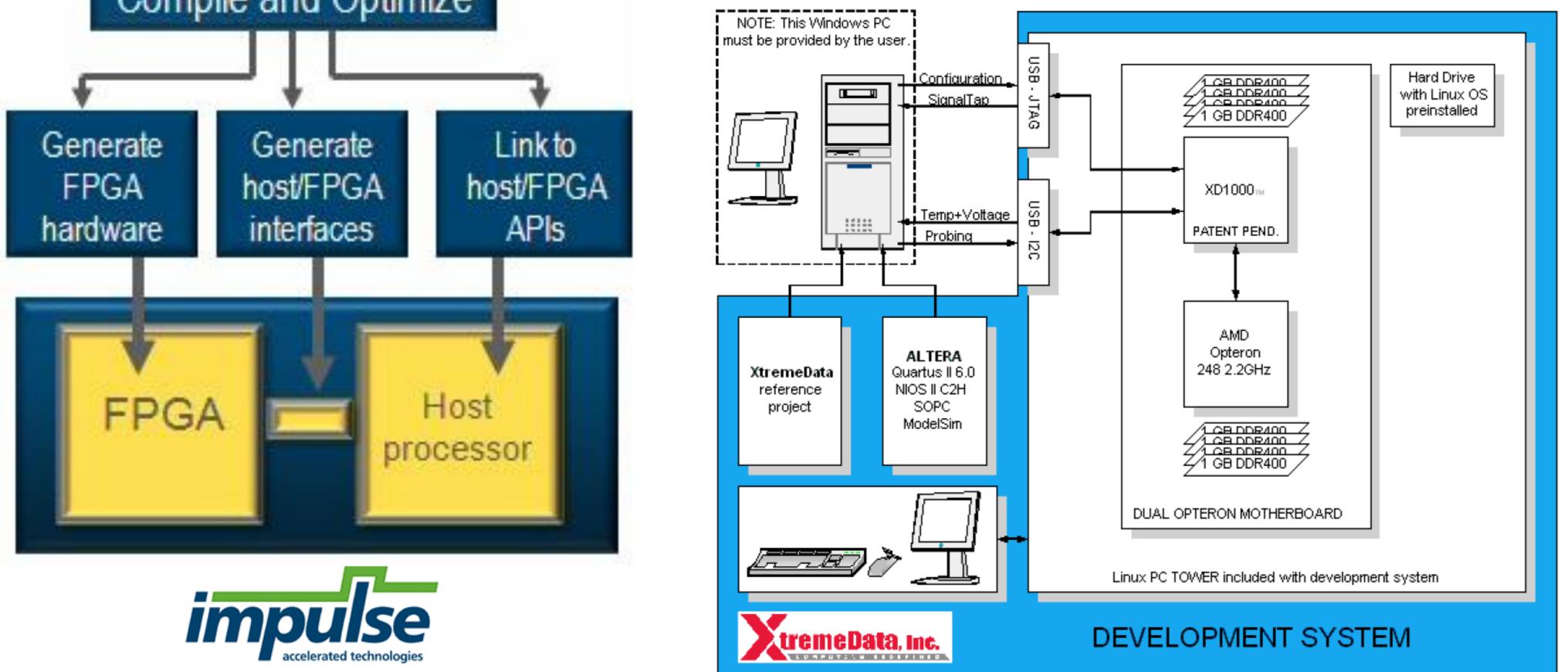

With hardware provided by XtremeData (<u>www.xtremedatainc.com</u>) and software provided by Impulse Accelerated Technologies (<u>www.impulsec.com</u>), this project aims to discover the feasibility and practicality of using a reconfigurable coprocessor to significantly improve the performance of computationally complex applications while significantly reducing the physical infrastructure that is typically required for modern high-performance computing systems.

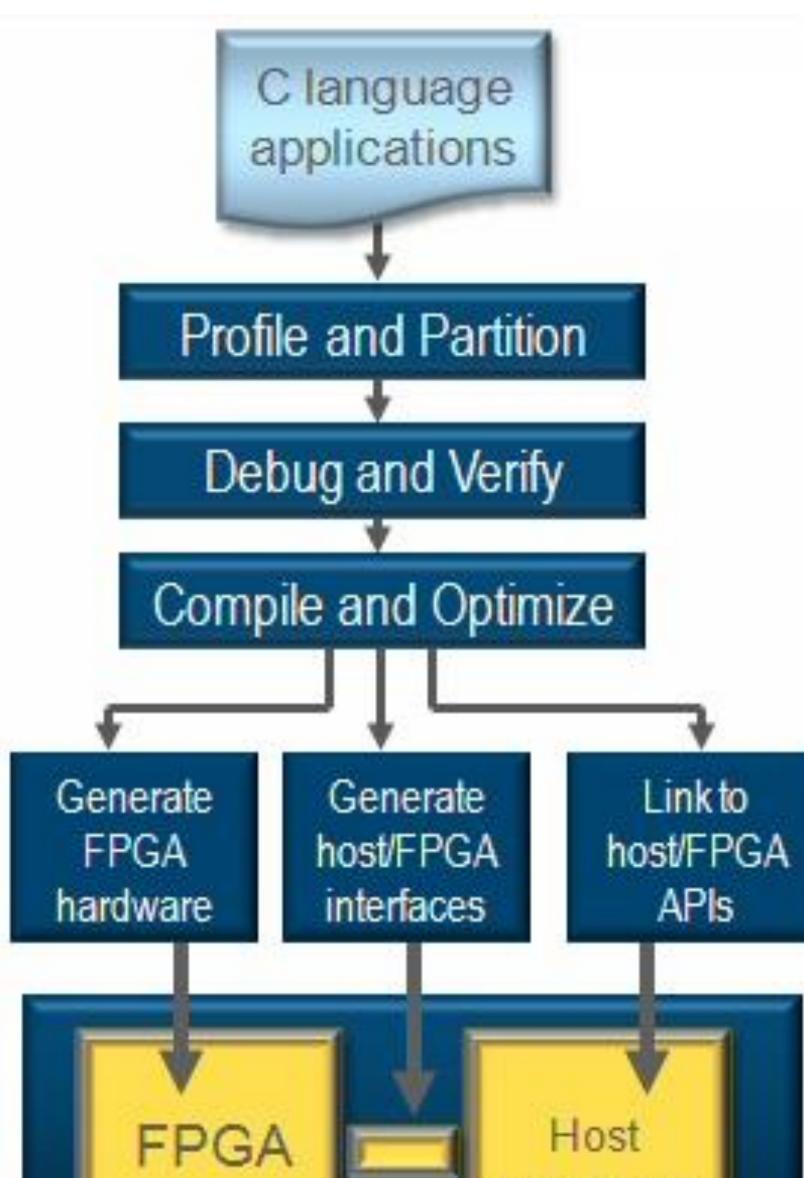

#### **Impulse C Design Paradigm**<sup>[1]</sup>

# **Research Objectives and Aims**

- Evaluate the performance and capability of XtremeData's XD1000 Computing Platform

- Floating-Point Performance

- Fixed-Point Performance

- Solve 1-D Wave Equation using FDTD (Finite Difference Time Domain Method) using the XD1000 platform

- Port an existing 802.11 Signal Modeling Application to the XD1000 Platform and evaluate its performance

# XD1000 Co-Processor<sup>[2]</sup>

## XD1000 Architecture<sup>[3]</sup>

# **Sources Cited**

[1] Impulse Accelerated Technologies (<u>http://www.impulsec.com/products.htm</u>)

[2] XtremeData Inc. (http://www.xtremedatainc.com/index.php?option=com\_docman&task=doc\_download&gid=17&Itemid=129)

[3] XtremeData Inc. (http://www.xtremedatainc.com/index.php?option=com\_docman&task=doc\_download&gid=17&Itemid=129)

## Acknowledgements

This research is supported by the following sponsors:

All Logos Copyrighted by their respective Copyright Holders.