# Effective Verification for DO-254 Projects

#### **David Landoll**

Applications Architect

G

R

# Agenda

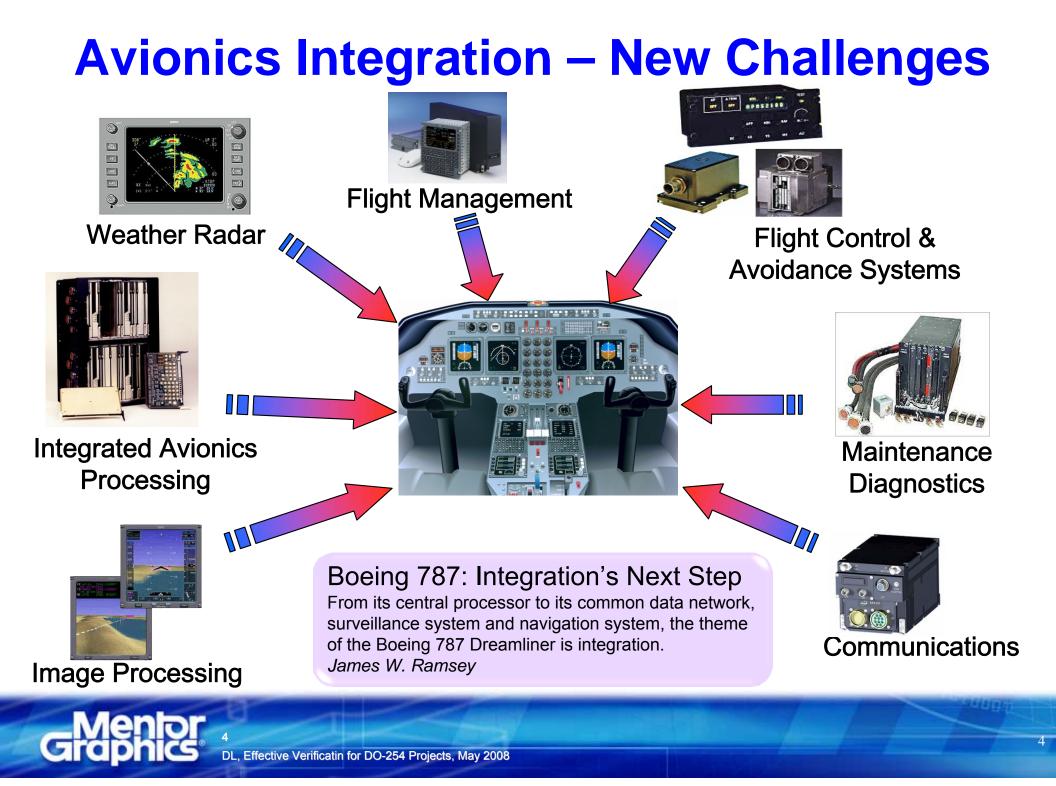

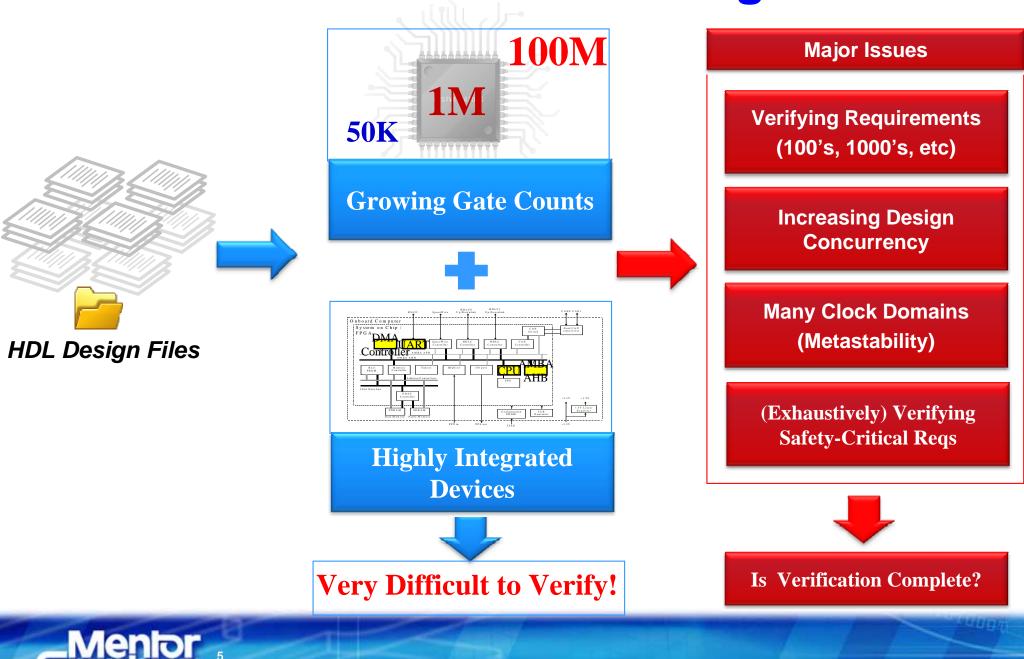

- Verification Challenges and Safety-Critical Design

- DO-254 Requirements for Verification

- Safety-Critical Verification: Recommendations

- Conclusion

# **Verifying for Safety Critical**

- Know that end product is customer safe

- Track that requirements are thoroughly verified

- Ensure verification processes to meet compliance to pertinent standards

- Keep project on schedule

## **Verification Challenges**

DL, Effective Verificatin for DO-254 Projects, May 2008

# **Questions for the Verification Manager**

- How do you know your tests really do *comprehensively* verify the requirements?

- Design performs its intended function

- How do you ensure you're testing the interactions between requirements (i.e., concurrency)?

- Design has no unintended functionality

- How do you ensure you catch anomalous behaviors that might not be tied to requirements?

- How do you manage your verification effort, measure your progress, and prove that you're done?

# Agenda

- Verification Challenges and Safety-Critical Design

- DO-254 Requirements for Verification

- Safety-Critical Verification: Recommendations

- Conclusion

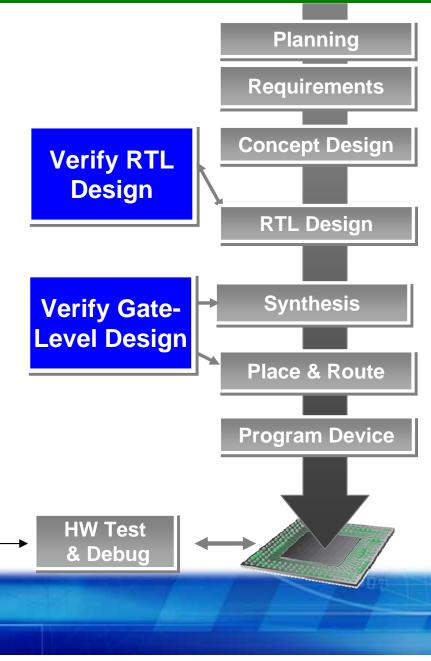

# Verification

#### Why it is Important

- The purpose of DO-254 is design assurance

- Designs must work as intended

- Quality verification is essential

- Verifying complex designs is very challenging

Note: In this presentation we will not be talking about testing the physical HW item, even though this is a requirement of "verification" for DO-254

Effective Verificatin for DO-254 Projects, May 2008

# Verification

*Verification Independence* so designer doesn't test own code

**Requirements-based test** on both RTL and Gate-Level design representations (as well as end hardware item)

**Traceability from Requirements to tests and results**

*Coverage* to ensure verification is complete

**Advanced Methods** for level A/B projects

*Reporting data* for audits and management

#### What Does Your Business Require?

*Cost effective methods* to ensure profitability

**Resources** used wisely

*Metrics* for monitoring progress and completion

**Assurance** of high quality results

*Compliance* to DO-254 requirements

# Agenda

- Verification Challenges and Safety-Critical Design

- DO-254 Requirements for Verification

- Safety-Critical Verification: Recommendations

- Conclusion

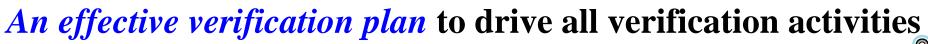

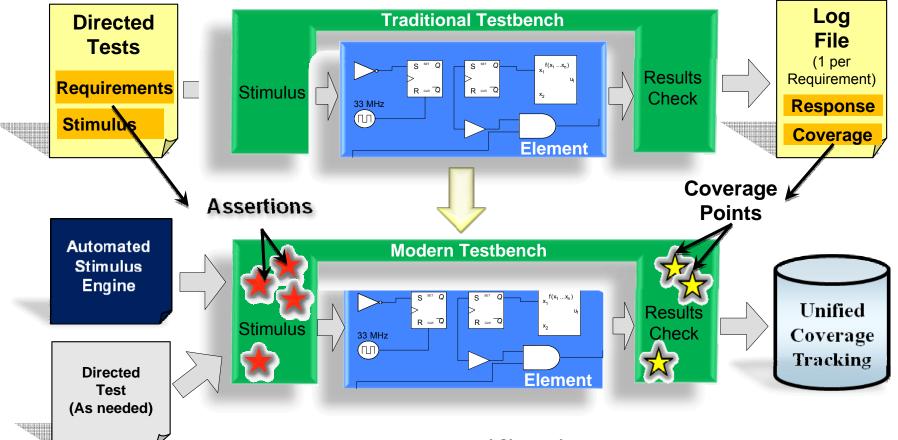

#### **Directed Test** A Traditional Approach

Model Sim

- A good approach for traditional design styles

- Manually-written tests exercise requirements via specified stimulus

- Testbench applies stimulus/checks results

- Log file includes results of test

- **Code coverage metrics determine if tests exercise RTL code**

Note: This method begins to fail with increased device complexity, integration and a large number of requirements

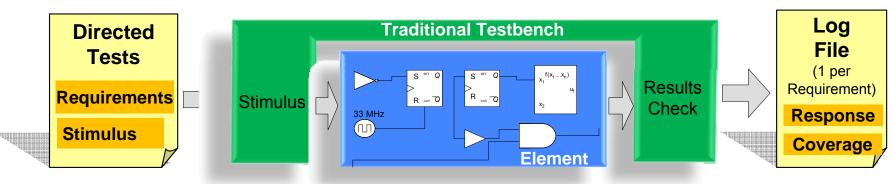

# **Traditional Coverage Limitation**

#### **Test Bench**

- These bugs exist, but are undetected

- Failures only appear if test propagates it to the output

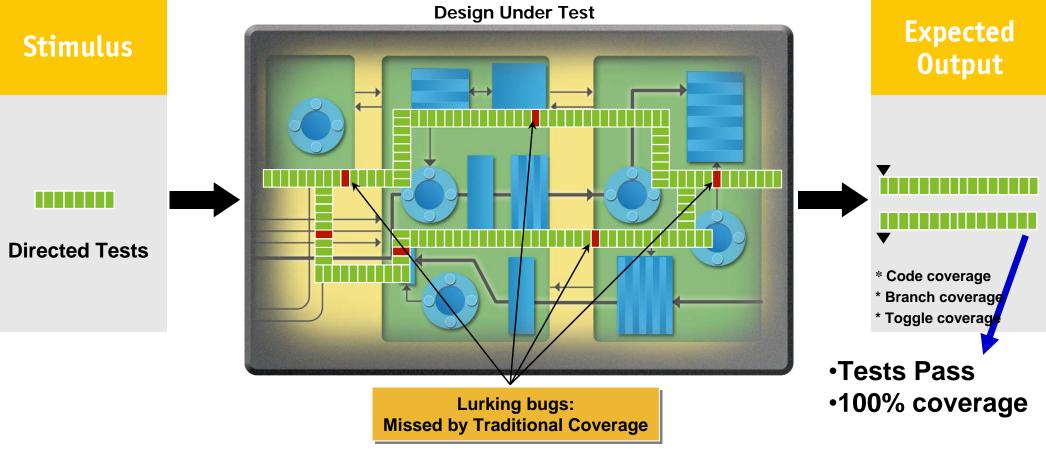

# **Evolution of Verification Methods**

- Most aerospace companies use this traditional approach (directed test/code coverage)

- More complex designs can benefit from newer techniques

#### **Automating Test Stimulus vs. Directed Test**

- Directed tests:

- Test writer must code each specific scenario to specify intent explicitly

- Prone to overestimating completeness of testing

- Doesn't scale with design complexity

- Automated test stimulus:

- Engine uses constraints and randomness to exercise a wide variety of possible scenarios

- Completeness driven by progress towards functional coverage goals

- Scales very efficiently with design complexity

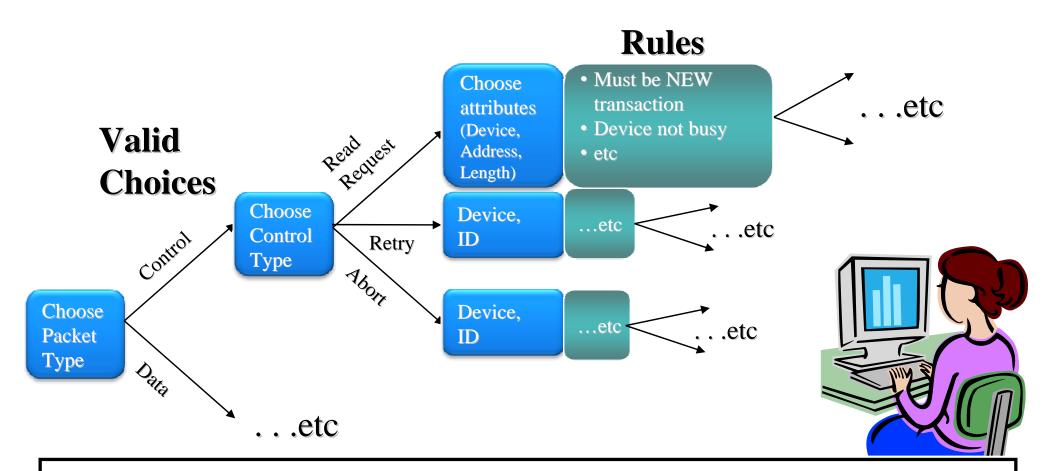

#### How do you build an Automated Testbench?

- 1. <u>Engineer</u> encodes traffic structure and rules per requirements (Testbench)

- 2. SystemVerilog Simulator then chooses paths (Stimulus), per rules (if any)

- **3.** Coverage measurements assures all paths taken per requirements

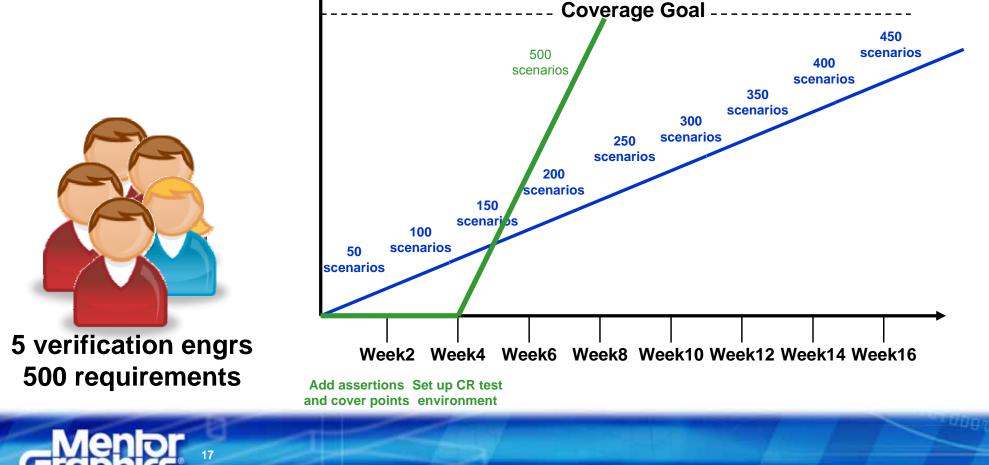

#### **Directed Test vs. Automated Test Stimulus**

#### **Directed Test**

- 1 test/scenario (1 day each)

- Immediate progress!

#### Automated Test Stimulus

- Up front infrastructure

- **5X productivity increase!**

#### Monitoring and Covering Requirements Assertion Based Verification

- Assertions are like comments that describe how the design is supposed to work (requirements)

- They actively monitor the design to ensure it does!

- Assertions provide traceability to requirements

#### **Requirement**

"The flight crew shall be aurally warned if the gear is down but not locked"

#### **Assertion**

property RQ62\_LANDING\_GEAR\_LOCK; @(posedge clk) GEAR\_down\_notification |-> ##[1:\$] Gear\_down\_lock\_notification; endproperty cover property RQ62\_LANDING\_GEAR\_LOCK;

18

#### Assertion Failure

DL, Effective Verificatin for DO-254 Projects, May 2008

#### Automated Test Generation Applied to DO-254 Modern Testbench Approach

- More complete verification

- **Requires fewer directed tests/resources**

- Direct link back to requirements

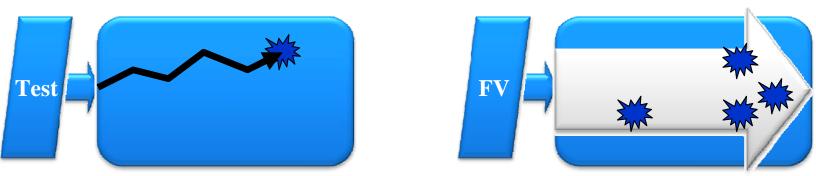

# **Formal Methods vs. Directed Test**

- Directed tests

- Simulation-based method that requires input stimulus

- Test writer must code a scenario that hits a bug

- If stimulus doesn't exercise a bug, the bug is missed

- Formal Methods

- Mathematical analysis done on RTL

--no stimulus needed

- Assertion provides description of requirement to be checked

- Formal engine analyzes assertion against every possible scenario (state)

- Exhaustive!

\*Note: Formal methods should be used in conjunction with (not as a replacement for) directed test and/or automated testing.

#### Example: Formal Model Checking for DO-254 Exhaustively Verify Safety-Specific Requirements

# Formal Model Checking finds all possible scenarios

- Example: enabling reverse thrusters

- Unexpected paths to this situation are called "sneak paths"

- Is there any way for some event to happen other than the correct way?

#### How to apply:

- Add an assertion stating that the event cannot happen in implementation

- Apply formal model checking

- Investigate/fix all unwanted situations

- Repeat process until no unwanted paths exist

#### **Requirement**

Reverse thrusters shall never fire in mid-air.

#### **Assertion**

assert always fire\_reverse\_thrusters

- -> Gear\_down\_lock\_notification

- @(clk'event and clk = '1')

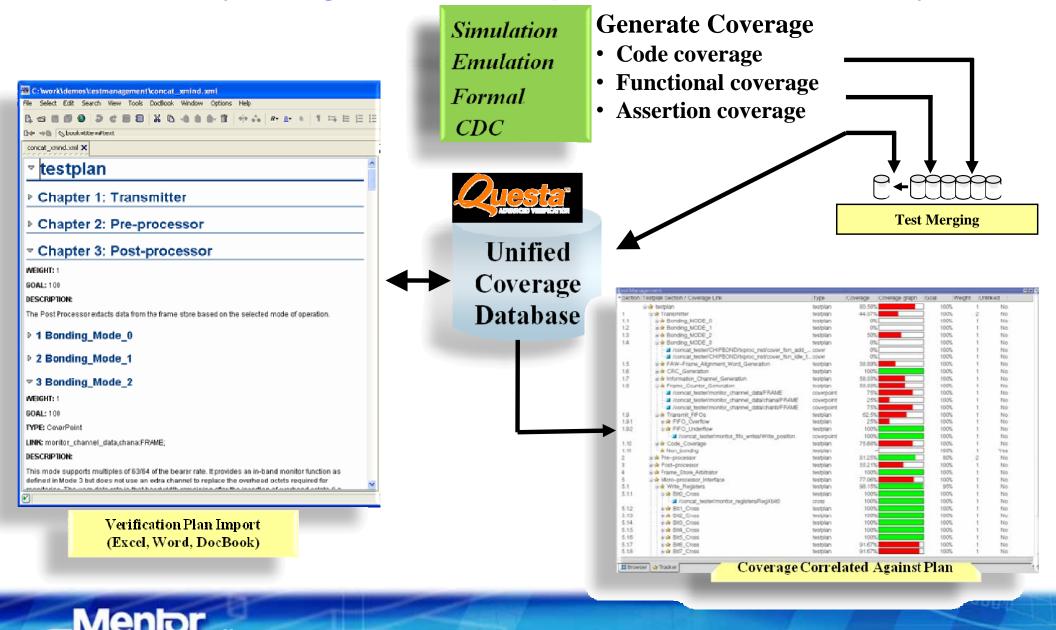

| Managing | Verification | for DO-254 |

|----------|--------------|------------|

|----------|--------------|------------|

| Needs                                              | Mentor Provides the Solution                                                                                |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| <b>Requirements-based</b><br>test and traceability | Verification activities mapped to<br>requirements-driven test plan with<br>links for traceability           |  |

| <i>Coverage</i>                                    | Unified coverage database to store<br>coverage data from a variety of<br>sources, with a variety of metrics |  |

Verification management facilitates reporting of progress (coverage) of requirements

Verification Mgmt

and Reporting data

#### Verification Management and Unified Coverage Quality, Progress and Requirements Traceability

## Model Sim.

# Verification with Mentor

#### **Advanced Methods**

**Assertions** Auto Test Stimulus **Functional Coverage** Verification Management and Unified Coverage

**Formal Verification Clock-Domain** Crossing

Logic Equivalency **Checking**

System Modeling

#### Mentor Leads in Advanced Verification

- **Actively monitor adherence to requirements**

- Automated stimulus generation to reach many more scenarios than directed test

- Measure coverage against design requirements

- Manage and report on verification progress

- Mathematical analysis to exhaustively prove safety-critical requirements, ...

- **Check clock-domain crossings to eliminate** metastability

- Assure two models are functionally equivalent

- Virtual lab for design and analysis of distributed mechatronic systems

**Advanced methods can improve both safety and efficiency!**

# Agenda

- Verification Challenges and Safety-Critical Design

- DO-254 Requirements for Verification

- Safety-Critical Verification: Recommendations

- Conclusion

Conclusion

- Mentor can help you establish a methodology that is efficient, reusable, and certifiable

- Industry leading solutions in wide use

- Supporting DO-254 objectives

- Scalable methods for the simplest to the most complex safetycritical project

- Applying advanced methods will:

- Improve verification efficiency and thoroughness

- Reduce development costs

- Improve safety of hardware systems

# **More Information**

- Visit our web site: <u>www.mentor.com/go/do-254</u>

- Here you will find numerous resources including the following verification-related publications

- "Achieving Quality and Traceability in FPGA/ASIC Flows for DO-254 Aviation Projects"

- "The Use of Advanced Verification Methods to Address DO-254 Design Assurance"

- "Effective Functional Verification Methodologies for DO-254 Level A/B and Other Safety-Critical Devices"

- "Assessing the ModelSim Tool for Use in DO-254 and ED-80 Projects"

- "Automating Clock-Domain Crossing Verification for DO-254 (and other Safety-Critical) Designs"

- "DO-254 Compliant Design and Verification with VHDL-AMS"

# R www.mentor.com