#### **Reconfigurable Computing Task**

## RHESE Reconfigurable Computing (RC) Task Lead: Clint Patrick/MSFC/EV43

RHESE RC – MAPLD 2008 – 15-18 September 2008

Goals and Objectives Reconfigurable Computing Task

#### **Central Goal of RHESE RC:**

#### "Development and Delivery of Reconfigurable Computing Resources for Space Infrastructure"

#### **Resulting in:**

- Hardware and functional interchangeability among CxP elements

- Increased cross-use and reuse of computing resources for multiple purposes

- Reduced flight spares and increased payload capacity

- Ability to change function and performance of a particular computing resource in part or entirely: manually or automatically

- Increased efficiency: lower long-term development cost, faster implementation, decreased power consumption

- Faster servicing, better mission assurance, and increased safety

## **Development Approach**

Reconfigurable Computing Task

## Internal Modularity

Reconfigurable Computing Task

#### Internal Modularity Reconfigurable Computing Task

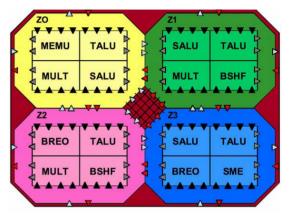

- ElementCXI ECA-64 "Field-Programmable Node Array" (FPNA)

- Field-Programmable Gate Arrays (FPGA)

- SIRF: Rad-Hard Virtex-5 FPGA

- Other viable RC-capable options

- Not restricted to one technology or even one chip

- Digital, Hybrid, or Analog (FPAA: "Analog Arrays")

- CPU technology may be utilized

- New technologies as available

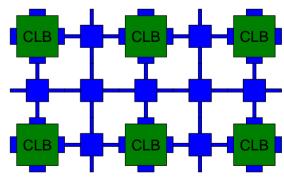

#### • Coarse vs. Fine Granularity

- Gate-level RC allows complete versatility, but costs in development complexity

- Medium to Coarse level adds abstraction, but costs in lowered flexibility

- Compromise, at least for now, should allow earlier development payoffs. E.g.: reconfiguration speed, HOS, fault handling

ECA Structure

Credits: Clive Maxfield, "The Design Warrior's Guide to FPGAs"

**FPGA Structure**

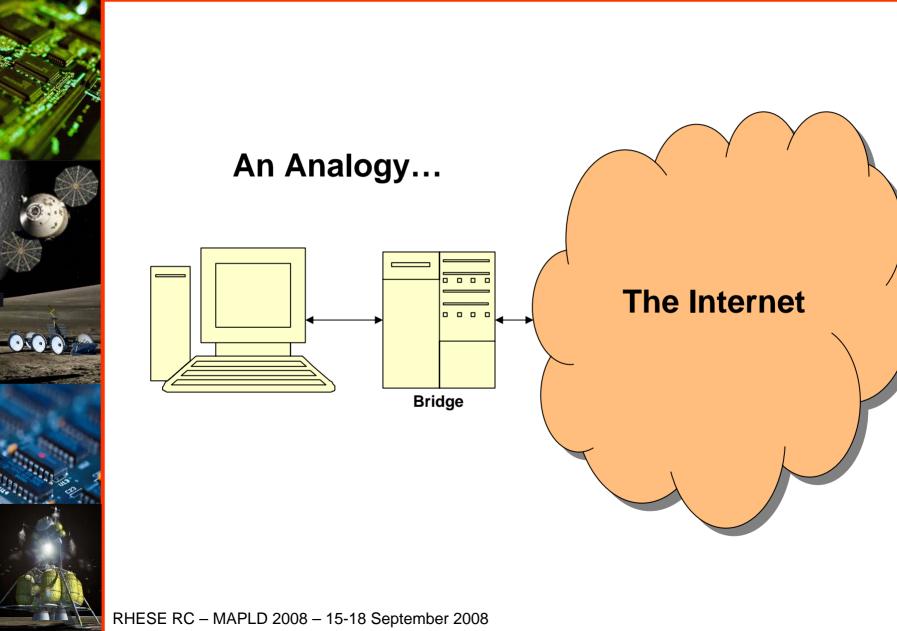

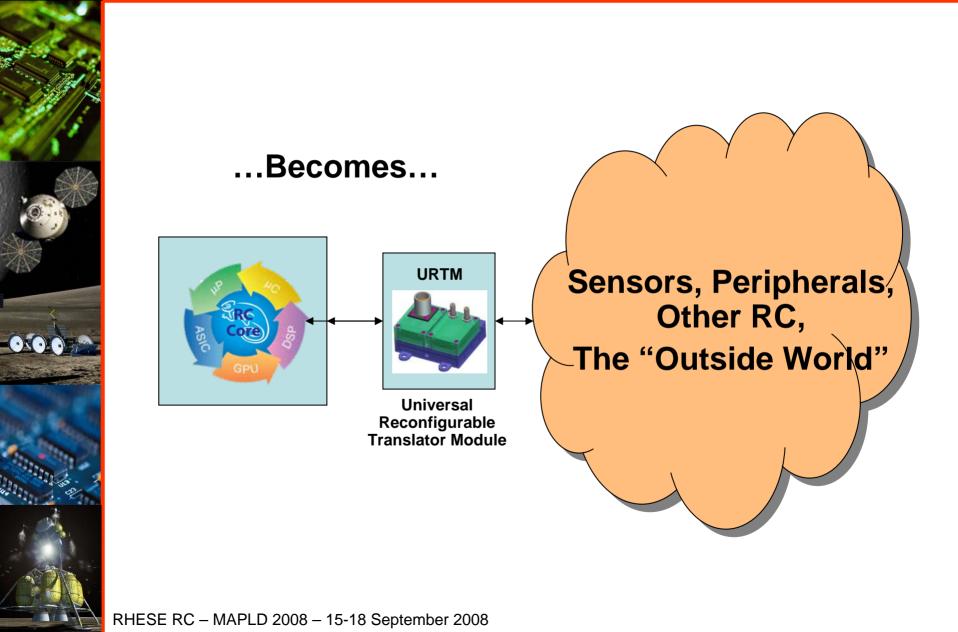

#### External Modularity Reconfigurable Computing Task

## **External Modularity**

**Reconfigurable Computing Task**

#### External Modularity Reconfigurable Computing Task

- Multi-Channel, Reconfigurable Interface Control

- Plug and Play

- Enables Interchangeability and Scalability

- Dynamic Channel and Bandwidth Management

- Fault Detection and Healing

- URTM

- LaRC and Sigma Space

- Currently, reconfigurable in bus standard implementations only

- Three, or possibly four, bus standards:

- SpaceWire

- 1553

- 1194b ("Firewire")

- Gigabit Ethernet option studied

RHESE RC - MAPLD 2008 - 15-18 September 2008

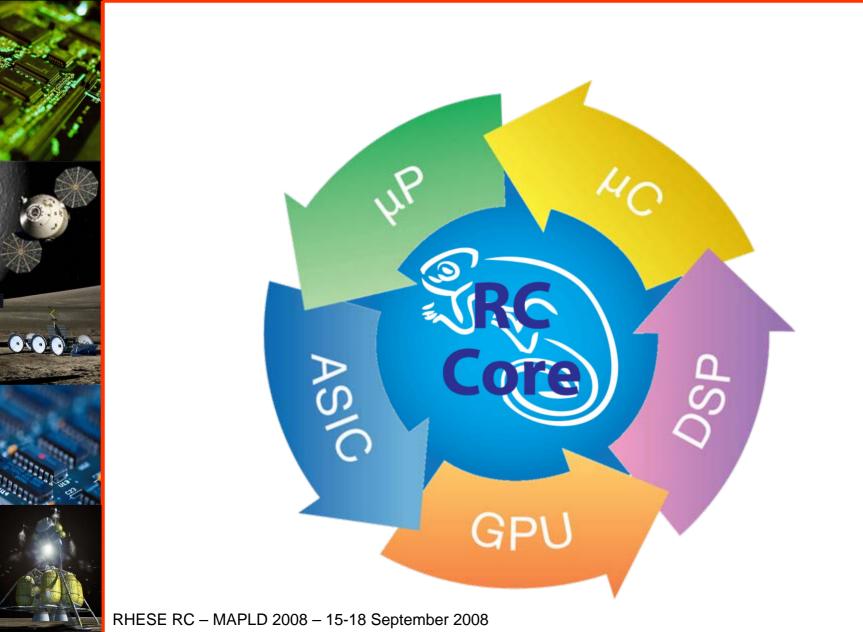

## **Demonstration #1**

**Reconfigurable Computing Task**

- Objectives

- Proof of Concept: Basic Reconfigurability

- Demonstrate multiple discreet configurations separately

- Configurations

- µP: Turing Machine

- DSP: Video FFT

- $\mu$ C: Motor Control and Feedback

- MSFC, September 16, 2008

RHESE RC - MAPLD 2008 - 15-18 September 2008

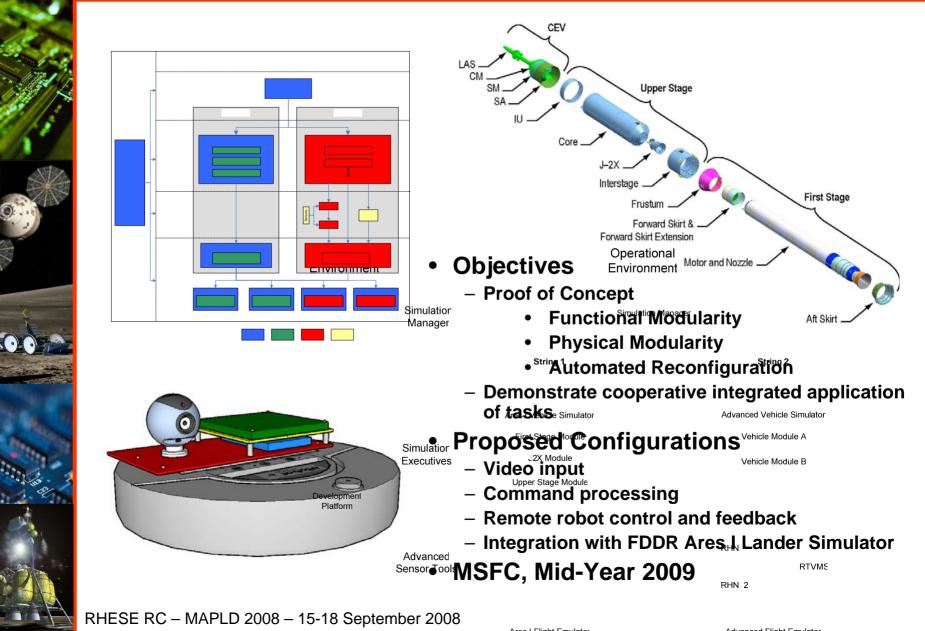

## **Demonstration #2**

**Reconfigurable Computing Task**

#### Fault Handling Reconfigurable Computing Task

Triple-Mode Redundancy (TMR) and Time-Domain Redundancy

- Detection

- Mitigation

- Healing

- Circuit Paging

- RC-as-Hard-Disk

- Circuit Isolation

- Fault Handling is already being explored as time allows, but not scheduled to be addressed until later

## Motivation: Addressing Customer Needs

**Reconfigurable Computing Task**

- Flight-Qualified, Multi-String Redundant Hardware is Expensive

- Development, Integration, IV&V, and Flight Qualification

- Space and Weight

- Power Consumption

- Dissimilar Spares

- Design of Computing Resources "From Scratch" for Every New Flight System is Unnecessary and Wasteful

- Current Options for Harsh/Flight Environment Systems are Limited

- Custom Hardware, Firmware, and Software

- Dedicated and Inflexible

- Often Proprietary

- Increased Requirements for Flexibility

- Reconfigurable and Modular Capabilities will address these

- Capacity to use one system to back up any number of others

- General Reusability of hardware = more payload capacity

- Interchangeability = reduction of development time and expense

RHESE RC – MAPLD 2008 – 15-18 September 2008

### **Schedule and Milestones**

Reconfigurable Computing Task

| ID  | WBS         | Task Name                                                                               | NASA Site |      | 04 | 2005    | 2006   | 2007           | 2008        | 2009           | 2010         | 2011 2<br>1 2 3 4 1   |   | 2013 |

|-----|-------------|-----------------------------------------------------------------------------------------|-----------|------|----|---------|--------|----------------|-------------|----------------|--------------|-----------------------|---|------|

| 256 | 1.2.5       | Reconfigurable Computing                                                                | MSFC      | 54%  |    | 1/24/06 |        | 1234           | 6/30/0      | 4 1 2 3 4<br>3 | + 1 2 3 4    | 1234                  |   | 2/12 |

|     |             |                                                                                         |           |      | _  |         |        |                |             | _              |              |                       |   |      |

| 263 | 1.2.5.7     | Complete Procurement of Testbed HW & SW - Phase 1                                       | MSFC      | 100% |    |         |        | $\bigcirc$     | 9/28/0      | 7              |              |                       |   |      |

| 269 | 1.2.5.13.1  | Develop Initial Testbed Interface                                                       | MSFC      | 100% |    |         | 3/1/07 | <b>    6</b> / | 15/07       |                |              |                       |   |      |

| 271 | 1.2.5.13.3  | Complete Testbed Interface Refinement                                                   | MSFC      | 100% |    |         |        |                | 9/28/0      | 7              |              |                       |   |      |

| 276 | 1.2.5.16.2  | Elemental Computing Array (ECA) Delivery                                                | MSFC      | 100% | -  |         |        |                | <b>12/1</b> | 7/07           |              |                       |   |      |

| 285 | 1.2.5.16.11 | Demonstration #1 of Basic Reconfigurability                                             | MSFC      | 0%   | _  |         |        |                | Ľ           | 3 9/18/08      |              |                       |   |      |

| 291 | 1.2.5.18    | Demonstration # 2 of Reconfigurable Spares                                              | MSFC      | 0%   |    |         |        |                |             | <b>4</b> /2    | 28/09        |                       |   |      |

| 296 | 1.2.5.23    | Demonstrate RC Automated/ Autonomous Fault<br>Response & Recovery                       | MSFC      | 0%   | _  |         |        |                |             |                | <b>D</b> 6/* | 16/10                 |   |      |

| 304 | 1.2.5.25.6  | IP Cores Delivery & Demo                                                                | MSFC      | 0%   |    |         |        |                | C           | 8/15/08        |              |                       |   |      |

| 308 | 1.2.5.27    | Demonstrate Platform/ Vehicle Sys Modularity                                            | MSFC      | 0%   |    |         |        |                |             |                | 6/           | 18/10                 |   |      |

| 312 | 1.2.5.31    | RC Infusion Plan Completed                                                              | MSFC      | 0%   |    |         |        |                |             |                | 3/2/11       | <mark> </mark> 3/2/11 |   |      |

| 314 | 1.2.5.32a   | Demo Platform-Indep Automated / Autonomous<br>Adaptive Env-Hard Avionics Suite Complete | MSFC      | 0%   | _  |         |        |                |             |                |              | 3/15/1                | 1 |      |

RHESE RC – MAPLD 2008 – 15-18 September 2008

## Key Performance Parameters Reconfigurable Computing Task

| Objective                                       | Constellation<br>Milestone<br>Supported | Key Performance Parameters              | Units                          | State of<br>the Art<br>(SOA) | Performance<br>Target (Full<br>Sucess) | Performance<br>Target (Min<br>Sucess) | Validation<br>Method |

|-------------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------|------------------------------|----------------------------------------|---------------------------------------|----------------------|

| Improve<br>Reconfiguration<br>Speed             | LPRP,<br>CEV Block 2                    | I Speed of Dynamic Reconfiguration I se |                                | 5                            | 1.00E-03                               | 1                                     | Test                 |

| Develop<br>Reconfigurable<br>Robust Electronics | LPRP,<br>CEV Block 3                    | Redundancy and Reconfigurability        | Levels of<br>Reconfigurability | None                         | 4                                      | 3                                     | Test                 |

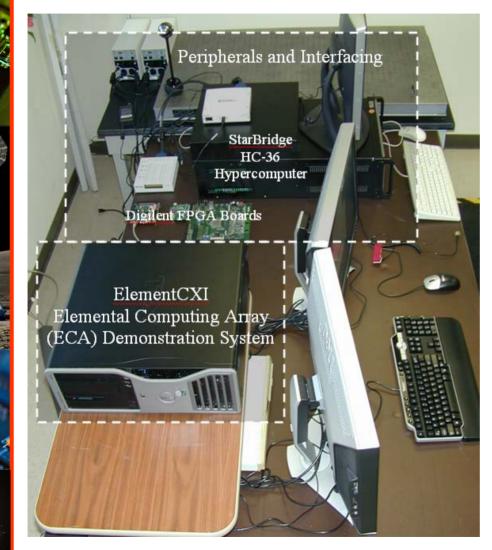

#### Accomplishments Reconfigurable Computing Task

#### **RC Accomplishments include:**

- Substantial groundwork and planning has been completed

- Main body of test bed acquisition and installation is complete

- Elemental Computing Array ECA-64 demo system has been acquired and assembled. Integration and development are ongoing.

- Implementation of large portion of first demo will be a Turing Machine.

- Initial work on Fast Fourier Transform (FFT) implementation

- Peripheral interfacing with ECA-64 progressing

- Student interns utilized as available for exploratory development of advanced demo materials: robotics, vision systems, etc.

- Universal Reconfigurable Translator Module (URTM), being developed by Sigma Space under contract to LaRC, is close to delivery. Acceptance review is planned for August 28, 2008.

## **FY09 Planned Activities**

**Reconfigurable Computing Task**

#### FY09 Planned Activities include:

- Report on first test bed demonstration

- Second demonstration and report(s)

- Begin efforts in basic fault detection, mitigation and healing

- Initial development of advanced external modularity

- Initial advanced test bed procurement and installation

- Forward planning for next phases

- Further advanced concepts development ahead of schedule

where possible

#### **Deliverables** Reconfigurable Computing Task

# NASA

#### **FY09 Deliverables**

- Demo #1 Report

- Demo #2 and Report

- Forward Planning and Engineering

- Initial Results of Advanced Development

#### FY10+ Deliverables

- Flight-Qualified, Radiation-Hardened Universal Modular RC

- TRL-6 Infusion at end of FY10 (aggressive)