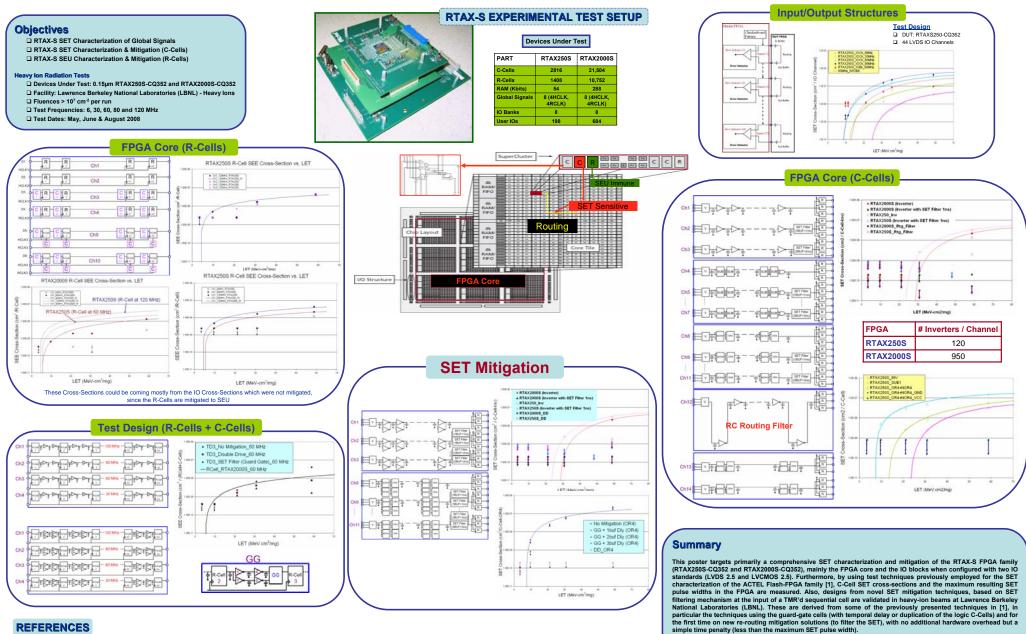

## SET Characterization and Mitigation in RTAX-S Antifuse FPGAs

Sana Rezgui, J.J. Wang, Yinming Sun, Durwyn D'Silva, Brian Cronquist, and John McCollum Actel Corporation, Mountain View, CA94043, USA

## REFERENCES

S. Rezgui, J.J. Wang, E. Chan Tung, J. McCollum and B. Cronquist, "New Methodologies for SET Characterization and Mitigation in Flash-Based FPGAs", *IEEE TNS*, Vol. 54, NO. 6, Dec. 2007, pp 2512-2524.

M. Berg, J. J. Wang, R. Ladbury, S. Buchner, H. Kim, J. Howard, K. Label, A. Phan, T. Invin, and M. Friendlich, "An Analysis of Single Event Upset Dependencies on High Frequency and Architectural Implementations within Actel RTAX-S Family Field Programmable Gate Arrays", *IEEE TNS*, Vol. 53, NO. 6, Dec. 2006, pp 3569-3574.

[3] <u>RTAX-S Antifuse Family FPGAs Datasheet</u>: Available: http://www.actel.com/documents/RTAXSDetailedSpecs\_DS.pdf

[4] J.J. Wang, "<u>RTAX</u> EDAC-RAM Single Event Upset Test Report", Available: http://www.actel.com/documents/RTAX-S%20SEE%20EDAC%20RAM.pdf

SET mitigation in the Combinatorial-Cells (C-Cells) of the RTAX-S family might not be needed (depending on the criticality of the application). Indeed, SET have very little effects on C-Cells and only starting from an LET > 20 MeV-

cm<sup>2</sup>/mg. This is due to the small geometry (0.15-µm) and its unique architecture (non-volatile and a naturally filtering architecture, reducing the SET pulse widths at each C-Cell).