## Single-Event Effects Testing of Embedded DSP Cores within Microsemi RTAX4000D FPGA Devices

Christopher E Perez Melanie D. Berg Mark R. Friendlich MEI Technologies in support of NASA/GSFC August 2011

# NASA

### **Motivation**

- Perform an independent study to characterize DSP core single-event upset (SEU) behavior

- Test DSP cores across a large frequency range and across various input conditions

- Provide flight missions with accurate estimate of DSP core error rates and error signatures

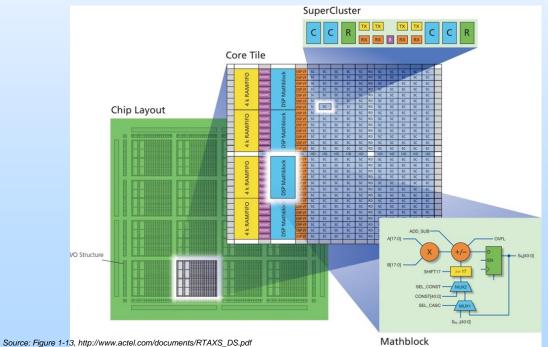

#### **Device Under Test**

- Microsemi RTAX4000D FPGA

- 0.15 µm CMOS logic fabric with anti-fuse configuration technology

- Embedded multiply-accumulate DSP blocks

- Flip-flops SEU-hardened via Localized Triple Modular Redundancy (LTMR) and output buffer triple-drive

#### **DSP Blocks**

#### Functionality

- 18x18 bit multiplier with 41-bit accumulator

- Inputs and outputs can be registered to perform 125 MHz single-cycle multiplyaccumulate functionality

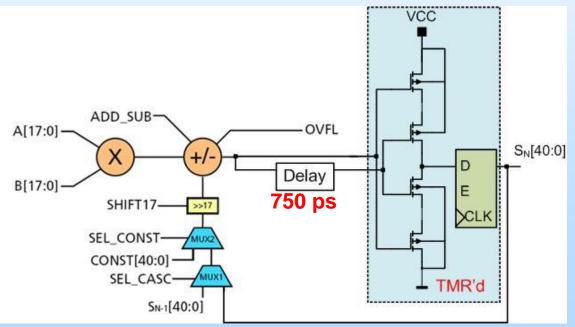

- Hardening

- SEU hardened by LTMR of all flip-flops

- Single-event transient (SET) mitigated by temporal redundant circuit that is placed at the input data pin of each flip-flop

Source: IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 57, NO. 6, DECEMBER 2010, pp. 3537-3546

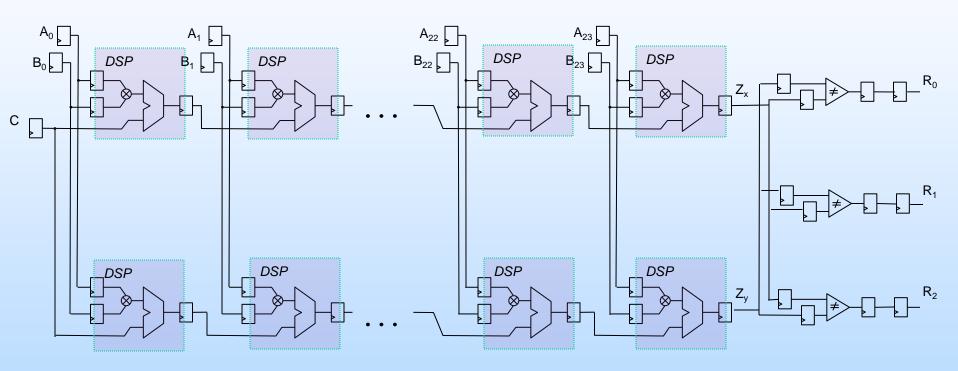

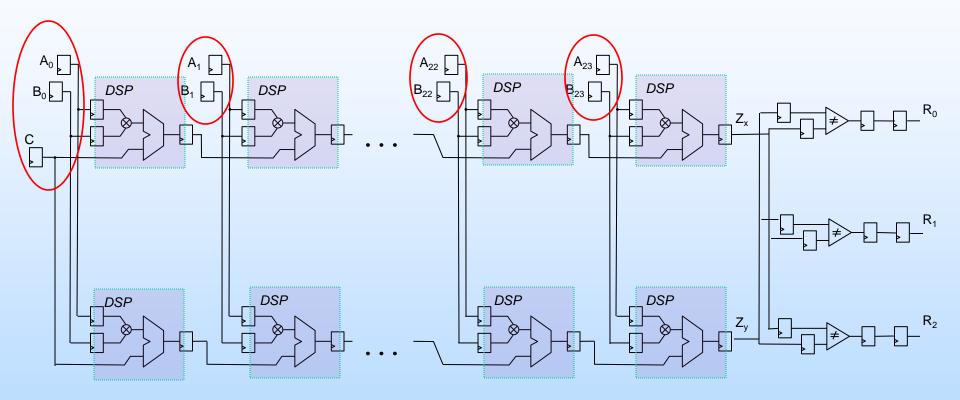

#### **Test Structure – DSP Chains**

- Chains consist of 24 cascaded AxB+C DSP blocks

- All chains are identical

- The chains are paired to perform internal checking

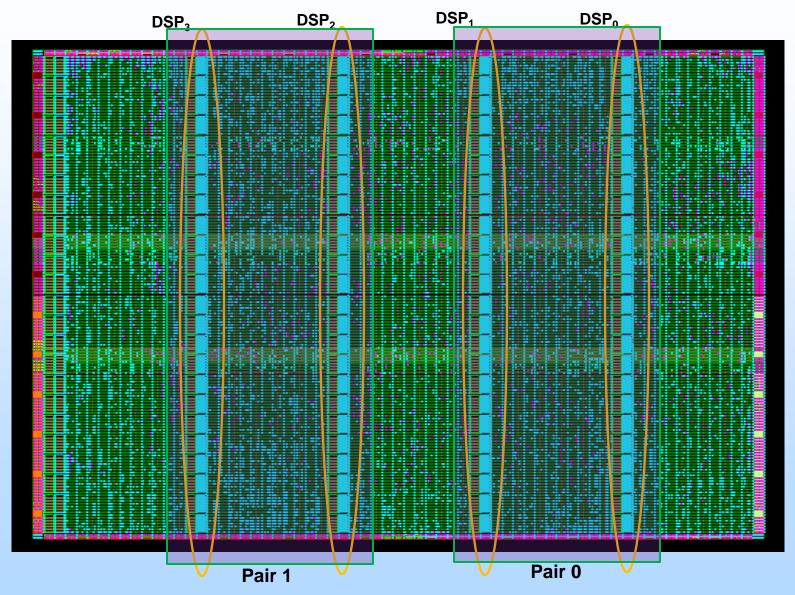

# Test Structure – Layout of DSP Chains

To be presented by Chris Perez at the Revolutionary Electronics in Space (ReSpace) / Military and Aerospace Programmable Logic Devices (MAPLD) 2011 Conference, Albuquerque, NM, August 22-25, 2011, and to be published on nepp.nasa.gov web site.

#### Test Structure – DSP Coefficient Control

- A and B (18-bit) parameters are selected by the tester

- Only the first-stage C (41-bit) parameter is selected by the tester

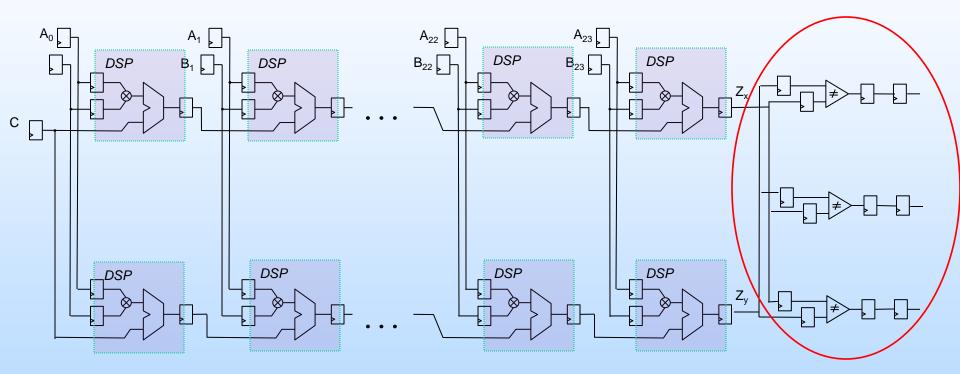

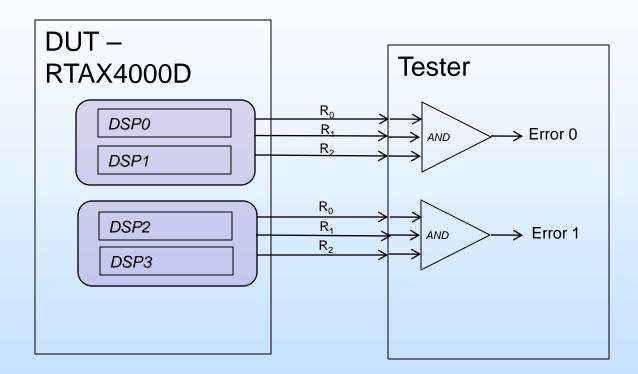

#### Test Structure – DSP Comparison Logic

- DSP blocks to be isolated by triplication of comparison logic

- Eliminate SETs/SEUs contributed from other logic

#### **Example DSP Upset**

- Logic analyzer screenshot of actual SEU in DUT DSP cores captured by tester system

- Sampling clock is >2X frequency of maximum DSP operating frequency

|                                                                                    | Intronix LogicPort Logic An    | alyzer     | - C:\Doo | ument | s and S | ettings | Lab1 Deskt            | op\Test_l | DataVLBNL_05 | _2011 Wactel_F           | RTAX4000D\logic | port\RTAX4     | 000D_DSP. |

|------------------------------------------------------------------------------------|--------------------------------|------------|----------|-------|---------|---------|-----------------------|-----------|--------------|--------------------------|-----------------|----------------|-----------|

| Fi                                                                                 | e Options Setup Acquisition Vi | iew Hel    | lp       |       |         |         |                       |           |              |                          |                 |                |           |

| Waveforms State List Notes 🖻 🗋 🖶 🎒 👬 🕸 🗮 🕨 א 📮 🗉 T! 🖌 👫 🚽 🕀 🗨 🎯 🦉 Buffer Position: |                                |            |          |       |         |         |                       |           |              |                          |                 |                |           |

|                                                                                    |                                |            |          |       |         |         |                       |           |              |                          |                 |                |           |

|                                                                                    | Sample Rate 💌                  | SOOMHz Log |          |       |         | Log     | jic Threshold 🚽 1.50v |           |              | Pre-Trigger Buffer 🗾 50% |                 |                |           |

|                                                                                    |                                |            |          |       |         |         |                       |           | ]            | •                        |                 |                |           |

|                                                                                    | Signal                         | Wire       | Wire     | Edge  | Cursor  | Cursor  | -80ns                 | -60       | Ins          | -40ns                    | -20ns           | T+0            | +20ns     |

|                                                                                    | Jigha                          | ID         | Status   | A     | В       | A       |                       |           |              |                          |                 | , <u>,</u> , , |           |

|                                                                                    | TMRO_O                         | DO         | L        | t     | 0       | 0       |                       |           |              |                          |                 |                | 1         |

|                                                                                    | TMR1_0                         | D1         | L        | t     | 0       | 0       |                       |           |              |                          |                 |                |           |

|                                                                                    | TMR2_0                         | D2         | L        | t     | 0       | 0       |                       |           |              |                          |                 |                |           |

|                                                                                    | TMRO_1                         | D3         | L        | t     | 0       | 0       |                       |           |              |                          |                 |                |           |

|                                                                                    | TMR1_1                         | D4         | L        | t     | 0       | 0       |                       |           |              |                          |                 |                |           |

|                                                                                    | TMR2_1                         | D5         | L        | t     | 0       | 0       |                       |           |              |                          |                 |                |           |

|                                                                                    | NONZERO_0                      | D6         | Н        | ļ     | 1       | 1       |                       |           |              |                          |                 |                |           |

|                                                                                    | NONZERO_1                      | D7         | Н        | ļ     | 1       | 1       |                       |           |              |                          |                 |                |           |

|                                                                                    |                                |            |          |       |         |         |                       |           |              |                          |                 |                |           |

#### **Initial Phase Test Parameters**

- For first round of testing, A<sub>i</sub>, B<sub>i</sub> set to counter for all cases

- Each clock cycle, A and B parameters increment by 1

- C parameter remained variable

- Test matrix:

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

|-----------|-----------|-----------|-----------|-----------|

| C=0       | C = 0     | C = 0     | C = 0     | C = 0     |

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

| C = +1    |

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

| C = -1    |

| 1 MHz     | 15 MHz    | 30 MHz    | 60 MHz    | 120 MHz   |

| C = count |

### **Heavy Ion Testing at LBNL**

- Energy : 15 MeV

- Fluence : up to 4.0E+7, OR until significant number of upsets observed

- Fluxes

- 2.0E+5 to 2.3E+5 : Ne

- 9.7E+4 to 1.1E+5 : Ar

- 7.0E+4 to 1.0E+5 : Cu

- Angles of incidence tested : 0°, 45°, and 60°

- Effective linear energy transfer (LET) values tested : 3.94 to 29.94 MeV·cm<sup>2</sup>/mg

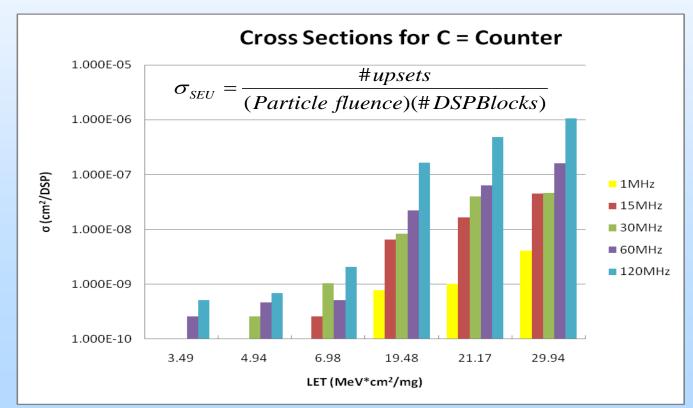

### Initial Phase Heavy Ion Test Results: SEU cross section (σ<sub>SEU</sub>) Frequency Effects

- $\sigma_{SEU}$  increases as frequency increases

- At low LET values, SEUs are minimal with low frequency operation

- As frequency increases, SEUs become more apparent

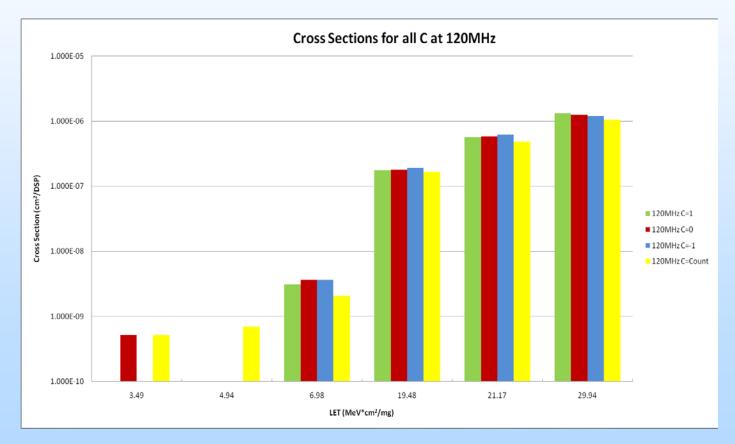

### Initial Phase Heavy IonTest Results: Coefficient Effects

- Choice of C parameter does not appear to have significant effect on  $\sigma_{\text{SEU}}$

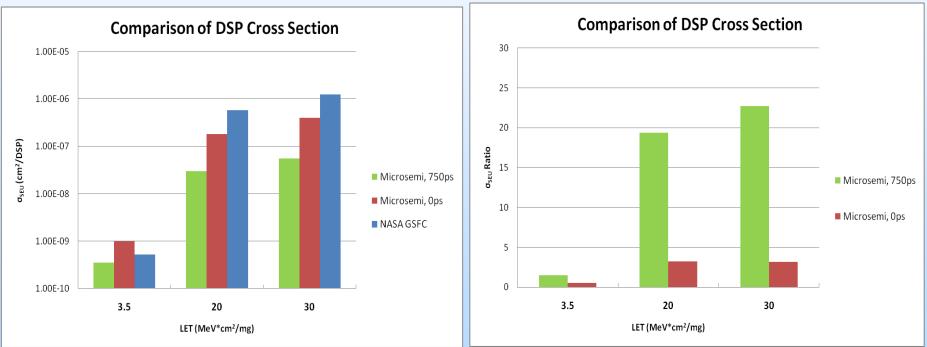

#### Comparison of NASA Radiation Effects and Analysis Group (REAG) results with Microsemi results

- At low LET, results are statistically similar

- As LET increases, differentiation becomes more pronounced

Source for Microsemi data: IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 57, NO. 6, DECEMBER 2010, pp. 3537-3546

#### Are SETs effectively being filtered by delay chain of 750ps and guardgate?

### $\sigma_{SEU}$ Analysis Using NASA REAG SEU **Model**

#### NASA REAG SEE Model for FPGAs

**Probability for Design Specific** system SEU

$P(fs)_{error} \propto P_{Configuration} + P(fs)_{functionalLogic} + P_{SEFI}$ Probability forProbability forConfiguration SEUFunctional logic

Functional logic SEU

**Probability for** Single Event **Functional** Interrupt

For RTAX-DSP target device...

$P_{configuration} \rightarrow 0 \quad P_{SEFI} \rightarrow low \quad P_{DFFSEU} \rightarrow 0$

$$P(f_s) \propto P(f_s)_{SET \rightarrow SEU} \propto \sum_{i=1}^N P_{gen}(i) \times P_{prop}(i) \times \tau_{width}(i) \times f_s$$

#### **Next Phase of Testing**

- Future testing to validate expected cross section saturation and threshold LET

- May limit testing to worst-case conditions (120 MHz) to increase data points

- Test at higher LETs to observe if any potential DSP functional interrupts or global functional interrupts

- Test at all other input conditions (A<sub>i</sub>, B<sub>i</sub> coefficients set static instead of dynamic)

### **Acknowledgements/Closing**

- RTAX-DSP FPGA devices remain good choice for designers of DSP algorithms targeting FPGAs for space

- All upsets observed appear to stem from transient capture at output registers of DSP cores

- How effective is the implemented temporal filter for the DSP blocks?

- I'd like to thank Melanie Berg, Mark Friendlich, Hak Kim for their expertise, assistance during test planning, design, execution, and analysis

- Questions?