# ReSpace/MAPLD 2011 Presentation Sandia Rad-Hard, Fast-Turn Structured ASIC The ViArray

August 23, 2011

K. K. Ma, John Teifel, Richard S. Flores Advanced Microelectronics & Radiation Effects Sandia National Laboratories MS 1072, P.O. Box 5800, Albuquerque, NM 87185 (505) 844-6469 makk@sandia.gov

Sandia National Laboratories is a multiprogram laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

### Outline

- Motivation of ViArray development

- ViArray architecture and platforms

- ViArray features

- Trusted ViArray

- Future direction

- Conclusion

### **Motivation of ViArray Development**

- Sandia's Microelectronics Program provides high-reliability, radiation-hardened Application Specific Integrated Circuits (ASICs) for system applications. Typical customer has

- Multi-year development program with spiral design process

- Low-volume production requirement, if any

- The schedule to design, layout, fabricate and package a cellbased ASIC is long, and the development cost is escalating.

- $\Rightarrow$  Designers using FPGAs for design iterations

- $\Rightarrow$  FPGA to ASIC conversion issues

# We need a faster and cheaper way to design and develop ASICs

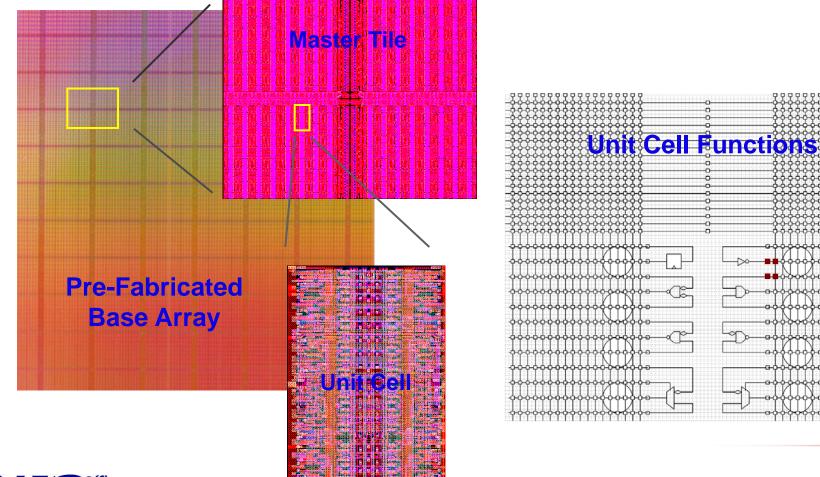

## **ViArray Architecture**

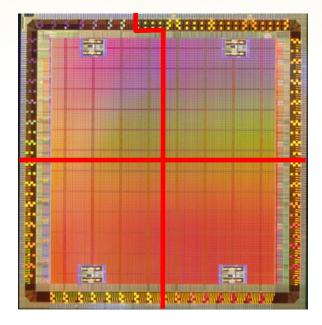

- Structured architecture

- Pre-fabricated base-array of repetitive functional fabrics

- Pre-determined vertical and horizontal signal routing channels

- One-mask metal-via configuration based on ViASIC<sup>®</sup> ViaMask<sup>™</sup>

### **ViArray Platforms**

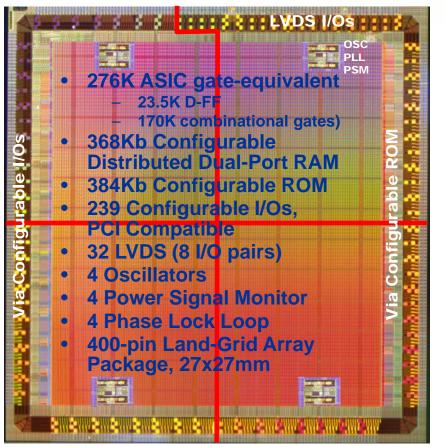

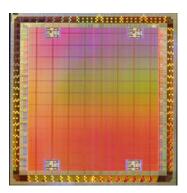

#### **Eiger** – A Digital ViArray Platform

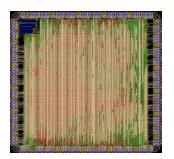

#### Whistler – A Mixed-Signal ViArray Platform

| 10           | na ang ang ang ang ang ang ang ang ang a                                                                                                                                                                 | LVDS I/Os                                                                                                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| jurable I/Os | Analog Elements     - 4 Cyclic ADC     - 4 Pipeline ADC     - 8 8-bit DAC     - 9 32-channel MUX     - 48 Generic     amplifiers     - 64 Generic     comparators                                        | • Digital Elements<br>- 138K ASIC<br>gate-<br>equivalent<br>- 184Kb<br>Configurable<br>Distributed<br>Dual-Port RAM |

| Via Config   | <ul> <li>128 Analog<br/>switches</li> <li>4 Band gap voltage<br/>reference</li> <li>1 High-speed S/H</li> <li>2 Temperature<br/>sensors</li> <li>2K ohm resistors</li> <li>2pf MIM capacitors</li> </ul> | Configurable E<br>ROM<br>• 239 Configurable                                                                         |

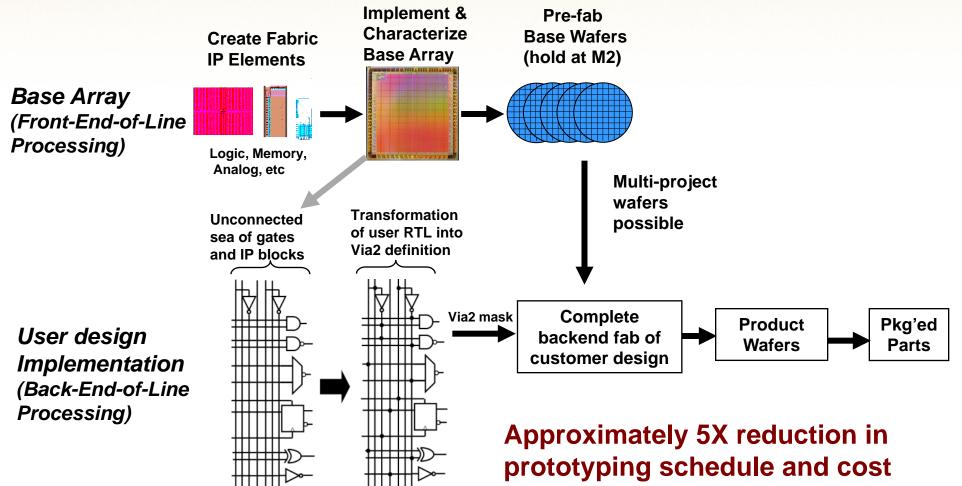

### **ViArray Implementation Flow**

prototyping schedule and cos compared to cell-based ASIC approach

### ViArray vs. Cell-based ASIC Comparison – Speed

#### **ViArray Operating Speed**

- For pipelined logic circuits with no static random access memories (SRAMs)

- up to 100 MHz

- For pipelined logic circuits with SRAM

- Up to 50 MHz

- Cell-based ASIC and ViArray have comparable speed because they have similar cell performance

- It is possible to operate at a higher speed with highly customized ASIC design

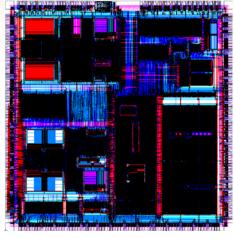

### Cell-based ASIC vs. ViArray Comparison – Density

# Typical Sandia CMOS7 0.35 μm rad-hard SOI cell-based ASIC density

• Logic: 8K – 10K gate equivalent per mm<sup>2</sup>

## Sandia CMOS7 0.35 $\mu$ m rad-hard SOI Eiger ViArray density

3.1K gate equivalent + 4.1Kbits Distributed DP RAM per mm<sup>2</sup>

# Cell-based ASIC and ViArray have comparable transistor density

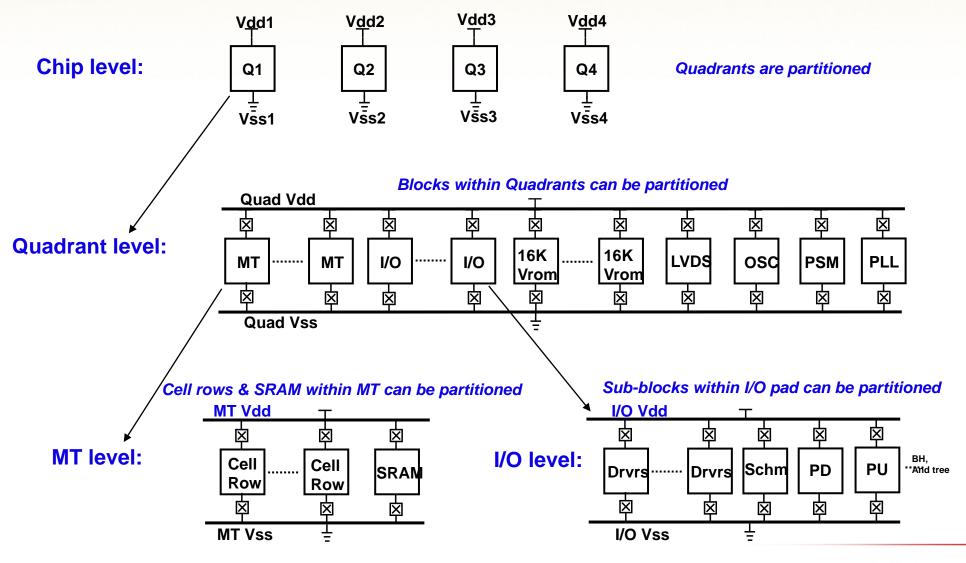

### ViArray Power Management Features – Power Partitioning

- Power sequencing

- Redundancy

- Sleep-mode operation

- Multiple applications

#### **Examples**

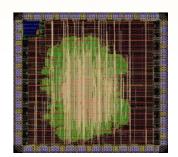

#### ViArray Power Management Features – "Off-grid" Unused Resources

### **Trusted ViArray**

#### The ViArray has an open architecture with

- highly compacted and optimized repetitive functional fabrics that are tightly laid out. Minor modifications could affect the overall layout.

- fine-grain configurable architecture. Resources in the ViArray are uncommitted until implementation of a specific application, i.e., until via-2 mask is defined.

- power management features. Resources in the ViArray may not be connected to power and ground.

- ⇒ The ViArray could achieve certain degree of trustworthiness even if the base-array is fabricated in an uncontrolled environment, IF back-end-of-line fabrication for specific application is controlled.

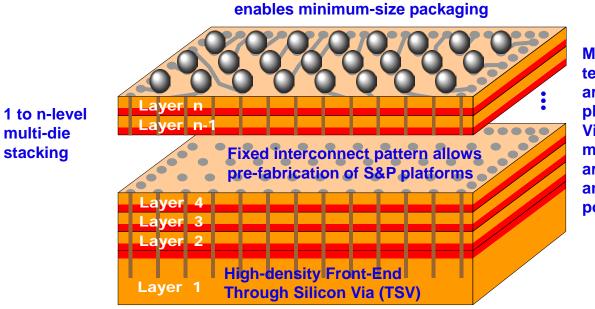

### **Future Direction**

- Additional ViArray Platforms

- Increase resources

- Special applications in extreme radiation environment

**Redistributed I/Os to Area Array**

- Precision analog functions

- Stack & Pack

Multi-function, multitechnology, multiarchitecture S&P platforms – ViArrays, memories, 3D multi-core processor architecture, precision analog, HBTs, MEMS, power devices...

### Conclusion

- Beginning in 2004, Sandia has developed the ViArray family of structured ASIC base arrays for its internal 350-nm radiation-hardened SOI foundry

- The ViArray architecture is highly efficient, competitive to custom designed cell-based ASIC in speed, power, and circuit density

- The ViArray has unique features to enhance power management, reliability and redundancy architecture for embedded applications

- The ViArray could achieve certain degree of trustworthiness even when the base arrays are fabricated in an uncontrolled environment

- The ViArray implementation approach achieves approximately 5X reduction in schedule and NRE costs compared to cell-based ASIC

- Sandia has a long-term plan to support the ViArray product family