# Agile Design Practices and High-Level Verification for Spacecraft Electronics Workshop

Moderator:

Tim Gallagher

Lockheed Martin

## Workshop Agenda

| 15:50 – 16:00                                                                                                       | Tim Gallagher                                                                            | Intro                                                                                     |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 16:00 - 16:07<br>16:07 - 16:14<br>16:14 - 16:21<br>16:21 - 16:28<br>16:28 - 16:35<br>16:35 - 16:42<br>16:42 - 16:49 | Tim Gallagher Mike Wirthlin Mir Sayed Ali Doug Krening Mike Horn Doug Johnson JP Walters | Agile Design Rapid Design HLS for DSP SystemVerilog OVM/UVM Virtual Proto FT Verification |

|                                                                                                                     |                                                                                          |                                                                                           |

**Panel Session**

Audience Q&A

9/9/2011

16:49 - 17:09

17:09 -

- Tim Gallagher on Agile Design

- LM Fellow, Reconfigurable Computing Technologies Lockheed Martin Space Systems Company

- Principal Investigator SSC SW Multi-Core Research

- Agile Design Practices and Processes for FPGAs

- Joint RTL and High-Order Language (HOL/ESL)

Based Development Methodologies

- Dr. Mike Wirthlin on Rapid Design

- Associate Professor ECE, Brigham Young University

- Associate Director of the BYU Configurable Computing Laboratory

- Faculty Advisor in the NSF Center for High-Performance Reconfigurable Computing (CHREC)

- Principle Investigator, DARPA Study on FPGA Design Productivity

- Research Interests

- Fault Tolerant FPGA design and reliable FPGA computing

- FPGA Design Productivity

- Mir Sayed Ali on HLS for DSP

- Sr. Staff Applications Engineer Microsemi Corp

- 11 years experience in the areas of FPGA design, verification and implementation

- Expertise on Microsemi IPs for space applications such as 1553, PCI and DSP

- Master's degree in Electrical Engineering from University of Oklahoma, Norman, USA

- ✓ "Digital Signal Processing (DSP) Design Flow and Design Techniques Using RTAX-DSP FPGAs" Thur 8:50 MAPLD Session C

- Doug Krening on SystemVerilog

- Advanced Functional Verification utilizing SystemVerilog Consultant

- Currently: Supporting Lockheed Martin / GOES-R

- Verification Methodology Development

- Verification Team Training

- FPGA Verification

- o Previously:

- President / Principal Engineer, FirstPass Inc

- Director / Principal Engineer, Vitesse Semiconductor

- Mike Horn on OVM/UVM

- Principal Verification Architect Mentor Graphics

- Primary responsibility to help organizations deploy UVM and OVM

- One of the authors of the UVM/OVM Online Methodology Cookbook

- http://verificationacademy.com/cookbook/

- Used High-level Verification Languages (HVL) since 1999 including Specman E, Vera and SystemVerilog

- ✓ "Applying OVM (UVM) to GOES-R C&DH

Development" Wed 13:50 MAPLD Session B

- Doug Johnson on Virtual Prototyping

- Staff Applications Consultant at Synopsys, Inc.

- 30+ years of industry experience in communication design engineering, electronic design automation (EDA) tools, applications engineering, digital signal processing (DSP), intellectual property (IP) licensing and account management

- BSEE from the University of Illinois at Urbana-Champaign.

- John Paul Walters on Verifying Fault Tolerance

- USC/ISI Computer Scientist, Adaptive Parallel Execution Group

- Research interests include fault tolerance and reliability, HPEC, multi-core processing

- Co-developed Virtex-4 fault injector

- Co-developed SpaceCube software fault tolerance layer

- ✓ "Radiation Hardening of FPGA-embedded CPUs via Software, Validated with Fault Emulation" Wed 13:25 MAPLD Session B

## Applying Agile Software Techniques to Hardware Design (FPGA)

Tim Gallagher

Space Systems Company

## **Agile Design for Hardware**

- Why?

- Multiple programs with "red" FPGA deliveries

- Reprogrammability has made designers lazy

- - Design as quickly as possible, troubleshoot in-circuit

- » Just throw together some code and hope it all works

- » Spend little time on design architecture and analysis

- Multiple Synthesis, Place & Route, Debug cycles

- » Place & Route runs can take days on tough designs

- » Difficult to debug in-circuit with today's complexity

Cost, schedule, customer satisfaction issues!

- Need a "one time to get it right" approach!

- Agile sets the attitude for error free designs!

## **Agile Design for Hardware**

- What?

- Agile Development Methods

- Rapid, short iteration design cycle

- Concurrent development and rapid-turnaround between HW, SW, Systems, and Verification Teams

- Delay decisions and deliver code whenever possible

- Test Driven Design (TDD)

- Verification team drives requirements, architecture, and design

- High-Level Verification

- Independent design and verification teams

- Different tools, languages, and methods to enforce isolation of efforts

## **Agile Design for Hardware**

1

- What?

- Agile Development Methods

- Static Analysis

- Eliminate tedious line-by-line reviews

- Design Patterns

- Templates for common design issues such as CDC, interrupts, I/O links/buses

- Just-In-Time Training (JIT<sup>2</sup>)

- Training delivered when needed

- Metrics and Bug Tracking/Reporting

- Includes real-time response to issues

**Proven Agile Techniques for Error Free Design**

## Reuse, Reuse, and More Reuse

Mike Wirthlin

Brigham Young University

NSF Center for High Performance Reconfigurable Computing (CHREC)

- Dr. Mike Wirthlin,

- Associate Professor, Brigham Young University (Department of Electrical and Computer Engineering)

- Associate Director of the BYU Configurable Computing Laboratory

- Faculty Advisor in the NSF Center for High-Performance Reconfigurable Computing (CHREC)

- Principle Investigator, DARPA Study on FPGA Design Productivity

- Research Interests

- Fault Tolerant FPGA design and reliable FPGA computing

- FPGA Design Productivity

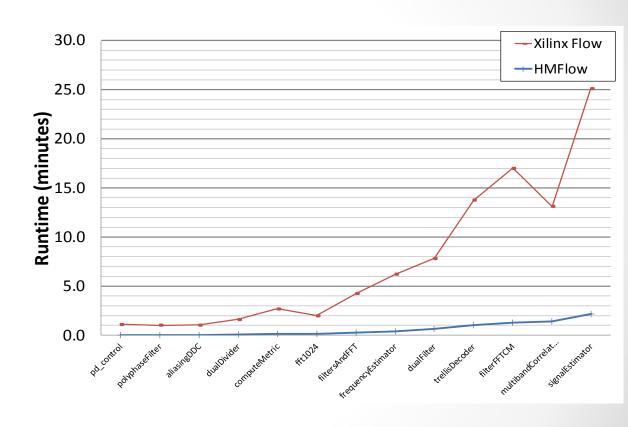

## DARPA Study on FPGA Design Productivity

## REUSE

gcc -o netmon netmon.c -lpthread -lm -lc

C threads library:

285 functions defined

C math library:

400 functions defined

Standard C library: 2080 functions defined

## DARPA Study on FPGA Design Productivity

Reuse a key component of design productivity

Design Effort = Initial Design Effort  $\times$  [(1-R) + (O  $\times$  R)]

R: Fraction of design exploiting reuse

O: Overhead of reuse

Example: R = .8 (reuse 80% of the code), O=.1 (10% overhead for reuse) Design effort with reuse =  $\frac{1}{4}$  the design effort without reuse

#### It is difficult to reuse

- Lack of documentation, test vectors, etc.

- Too specialized

- Not invented here (NIH)

"If the cost of reuse is more than 30% than the cost without reuse, reuse will seldom occur"

## Reuse RTL Code with Meta-Data (B1-09)

Facilitate Automated Reuse

| Loop Filter Parameterization |      |  |  |

|------------------------------|------|--|--|

| Accumulation Width           | 32   |  |  |

| Loop Bandwidth               | 0.01 |  |  |

| Loop Damping Factor          | 1.0  |  |  |

| Phase Detector Gain          | 6.0  |  |  |

| DDS Gain                     | -1.0 |  |  |

| Samples Per Symbol           | 2    |  |  |

| K Precision                  | 44   |  |  |

| Order                        | 2    |  |  |

Interface Synthesis

## Reuse Module Placement and Routing (B1-11)

#### Regular Design

Hard Macro Design

#### Reuse Bitstreams

View pre-verified and mapped hardware circuits as reuseable "chip"

Compose systems through bitstream "plug and

play"

## High Performance RTAX-DSP Design Using Synphony

Mir Sayed Ali Application Engineering August 2011

### **Topics**

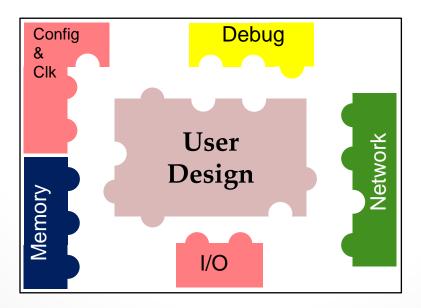

- RTAX-DSP Design Flow Overview

- Analyzing Architecture for Hand-Coded RTL

- Synphony Model Compiler Overview

- RTAX-DSP Design using Synphony AE

- Conclusion

## RTAX-DSP Design Flow Overview

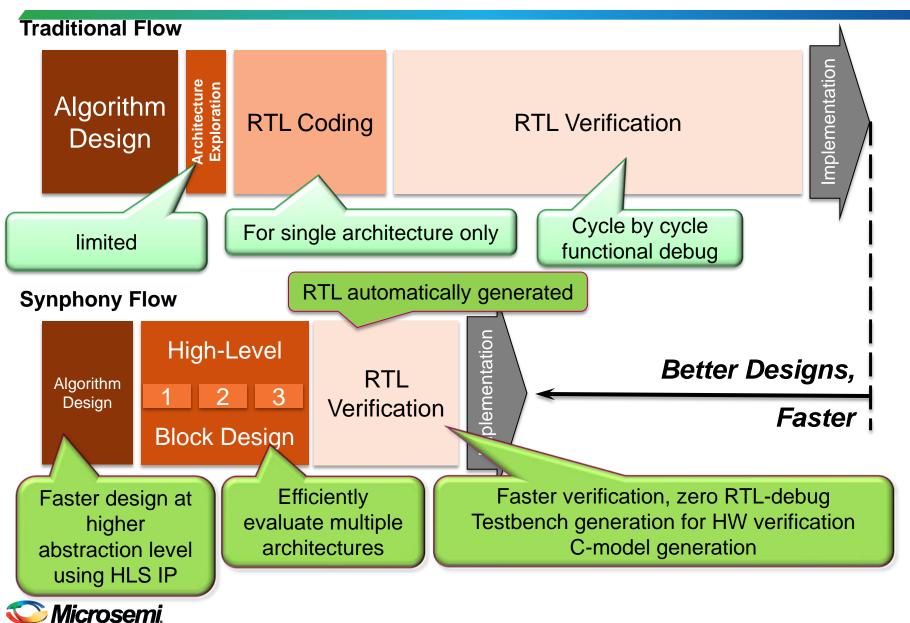

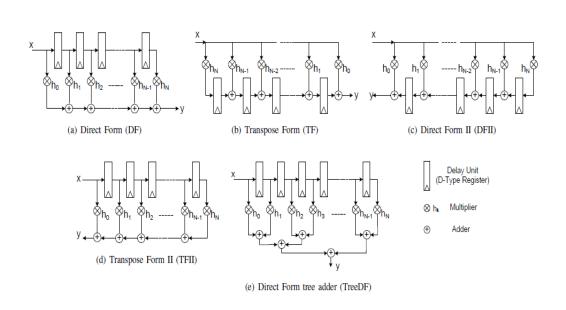

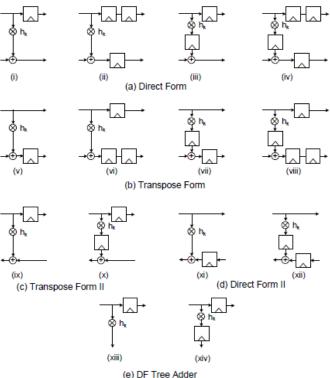

## Analyzing Architecture for Hand-Coded RTL

- Hand-coding RTL is time consuming

- Limited ability for the designer to fully explore the design space.

Example: A FIR filter can be implemented in various ways and with various pipeline options (Ref: Ramsey Hourani, Ravi Jenkal, W. Rhett Davis, Winser Alexander "Automated Design Space Exploration for DSP Applications" Journal of Signal Processing Systems Volume 56, Numbers 2-3, 199-216, DOI: 10.1007/s11265-008-0226-2)

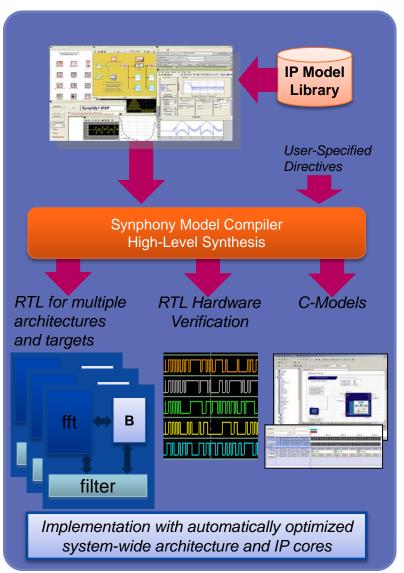

## Synphony Model Compiler Overview

- Quickly create synthesizable multi-rate algorithms using optimized IP model library

- Verify & validate early using Simulink® simulation and debugging

- Globally optimize IP and system architectures using high-level synthesis

- Achieve superior QoR with high quality RTL optimized for ASIC and FPGA

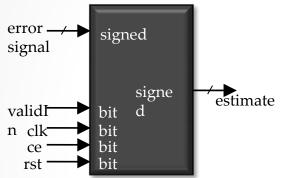

## RTAX-DSP Design using Synphony AE

Create Design in Simulink Using Microsemi/ Synphony Libraries

- Make sure that all design in-outs are defined with Port In and Port Out blocks from the Synphony blockset

- Simulate and verify the design in Simulink to ensure correct functionality

Add Signal Compiler to Model and create encrypted RTL Code and Testbench for simulation

Convert the encrypted rtl to a regular RTL Netlist (Optional)

Create a Libero project and import Files and perform RTL simulation

Add other logic/block in the Libero if needed

Synthesize HDL Code Run Place & Route Program Device Simulink

Libero

#### Conclusion

- Synphony allows Superior Simulink implementation flow

- Quickly create synthesizable multi-rate algorithms

- May need addition steps to convert encrypted RTL

- May not always give higher performance compared to Hand\_coded RTL

- Higher capacity and superior optimization technologies for FPGA

- Tight integration with Synplify (FPGA)

- Best ease-of-use, portability and also re-use

## Functional Verification with SystemVerilog

Panel Member:

Doug Krening

Advanced Verification Consultant

#### Motivation

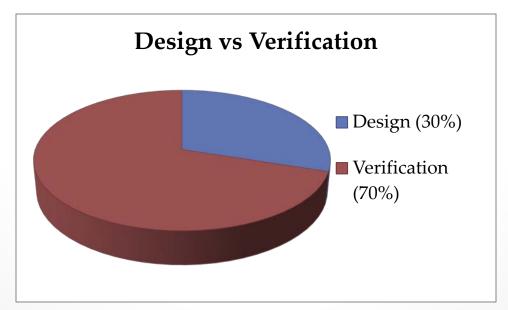

- FPGA/ASIC Design and Verification Reality

- Chip Complexity is Ever Increasing

- Verification Complexity Growth Outpaces Design

- High Quality, On Schedule, Within Budget ... or Fail

## **Project Management View**

- Better, Faster, Cheaper Pick Two?

- New Technology helps Solve the Dilemma

- Advanced Functional Verification Languages

- e -> Vera -> SystemVerilog

## The Engineer's View

"Functional verification is a tedious, mind-numbing task."

Doug Krening, c2000

"Functional verification is awesome. I love breaking a good design."

Doug Krening, c2010

- The Difference? Advanced Verification Languages

- Old School == Lackluster Engineer

- Advanced == Enthusiastic Engineer

## Organizational Implications

- Requires a Dedicated Verification Organization

- o Engineers, Training, Methodology, etc.

# Universal Verification Methodology (UVM) – Taking SystemVerilog to the Next Level

Panel Member: Michael Horn Mentor Graphics

UVM

## Why Use a Standard Methodology?

- SystemVerilog is a huge language

- Data Types

- RTL constructs

- o Classes/OOP

- Assertions

- Need to provide structure and guidance

- Limit the choices to improve reuse/interoperability

- Avoid chaos & repetition

- Provide off the shelf training and support options

- Most Important Allow people to efficiently work together

**Fo**oter Text

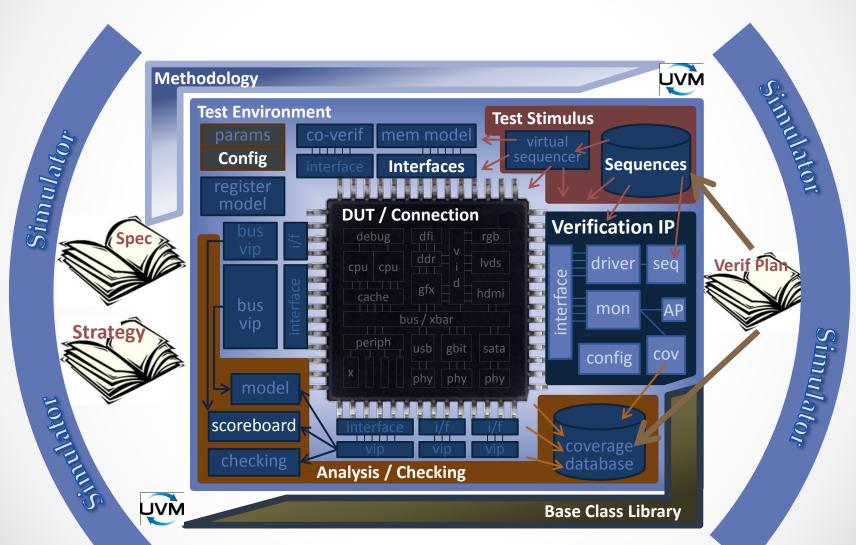

#### What is the UVM?

- Universal Verification Methodology

- Accellera industry standard for verification methodology

- ARM, Aldec, AMD, Atrenta,

Cadence, Cisco, Cypress, Duolog,

Freescale, IBM, Intel, Jasper,

Magillem, Mentor Graphics, Nokia,

NXP, Oracle, Paradigm Works,

Qualcomm, Renesas, Semifore,

SpringSoft, ST Microelectronics,

Synopsys, Texas Instruments,

Verilab, Xilinx

- Reference Implementation

- SystemVerilog Base Classes

- Based on OVM2.1.1

### **UVM** Foundations

#### Objective

#### **Justification**

- Separation of stimulus generation from Several people can develop stimulus delivery

- Raise the abstraction level of stimulus \_\_\_\_\_\_ Increase productivity and checking

- Test bench configuration

Avoid expensi

- Interoperability

- Standard class library & API

- Reuse

- o VIP

- Testbench components

- Stimulus

# Enabling Pre-Silicon Hardware/Software Validation With Virtual and FPGA Prototyping

ReSpace/MAPLD August, 2011

Doug Johnson

Staff Applications Consultant

Synopsys, Inc.

### Why Prototype?

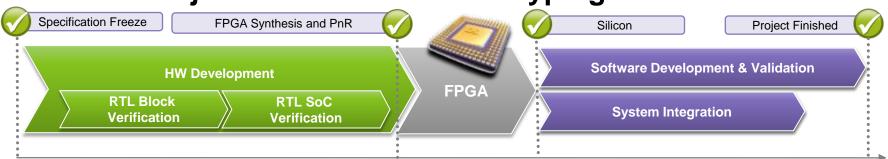

### Faster HW/SW Integration & System Validation

**Standard Project Flow Without Prototyping**

#### **Reduced Development Time with Prototyping**

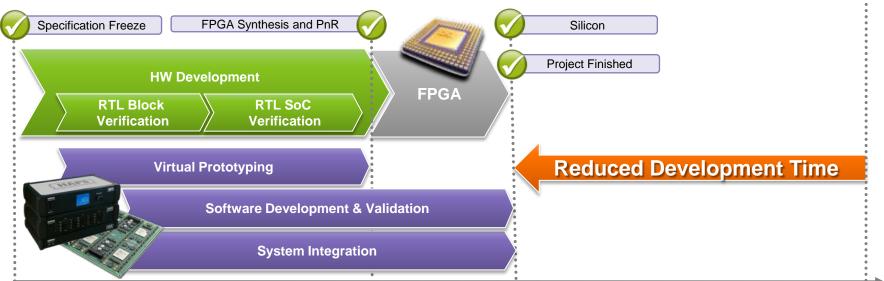

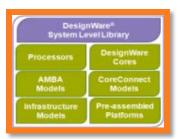

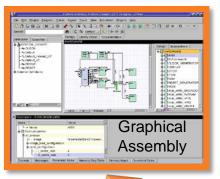

### **Virtual Prototyping Flow**

### Virtual Prototype Creation

Model Libraries 3<sup>rd</sup> Party Model Integration

Debug: Source RTL Code and SystemC/TLM Aware

Automated Packaging

High-Level Synthesis -Component Creation

Algorithmic

Component

Modeling and

Implementation

Automation

- Exploit C-Synthesis for algorithmic, DSP and communications modules

- Exploit FPGA processors, interconnect, peripherals and platform models

- Support for standard based technologies SystemC/TLM 2.0

- Efficient graphical assembly of virtual prototypes

- Support for fast simulation at multiple abstraction levels

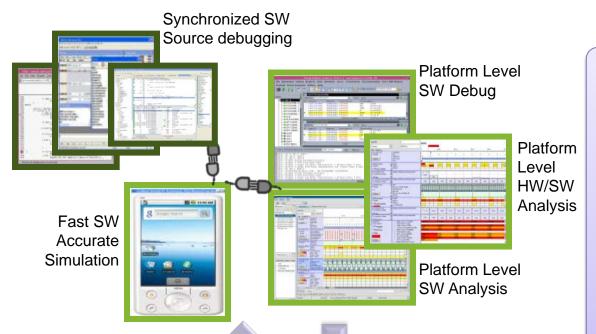

### Virtual Prototype *Use*

**Co-Simulation and External Connectivity Interfaces**

FPGA Prototyping

RTL Simulators

Physical System Sim

Test Benches

- Advanced software debugging and analysis tool for virtual prototypes

- Synchronized integration and execution with 3<sup>rd</sup> party SW debugging tools (ARM, GDB..)

- RTL Co-Simulation for system level validation

- FPGA Prototyping for real-world hardware/software validation

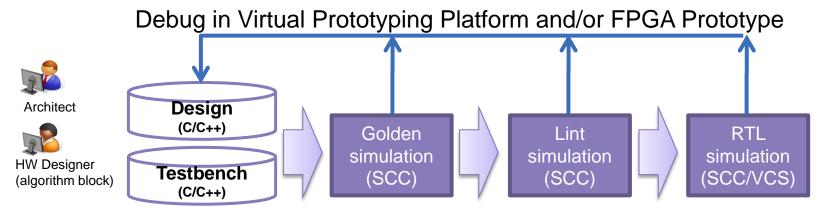

## Synphony C Compiler Designer for Algorithmic Model Development

- SCC synthesizes untimed C/C++ code into timed RTL code for implementation

- Three verification levels within SCC and Virtual Prototyping tools

- Golden: Simulates synthesizable C/C++ code and compares to the reference vectors

- Lint: Checks for common coding errors such as overflow and out-of-bounds

- RTL: Checks exact performance and verifies results match reference

- Designer can quickly verify system-level test vectors

- Coarse-level vectors created to verify system-level functionality

- Designer can quickly additional vectors to apply to RTL and FPGA prototype

- Virtual prototyping tools provide detailed graphical views and reports for debug if any simulation fails at any level of abstraction

- High-level models

- RTL

- FPGA prototype with co-simulation interfaces

### **Advantages of FPGA and Virtual Prototyping**

Increased Level of Architectural Exploration

**High-Level Synthesis**

Synphony C Compiler High-Level Synthesis

Links to Virtual Prototyping

Higher Performance & Earlier Validation

Faster BringUp

Co-Simulation with VCS

## Fault Tolerance Verification Through Software Fault Injection

John Paul Walters

USC/ISI

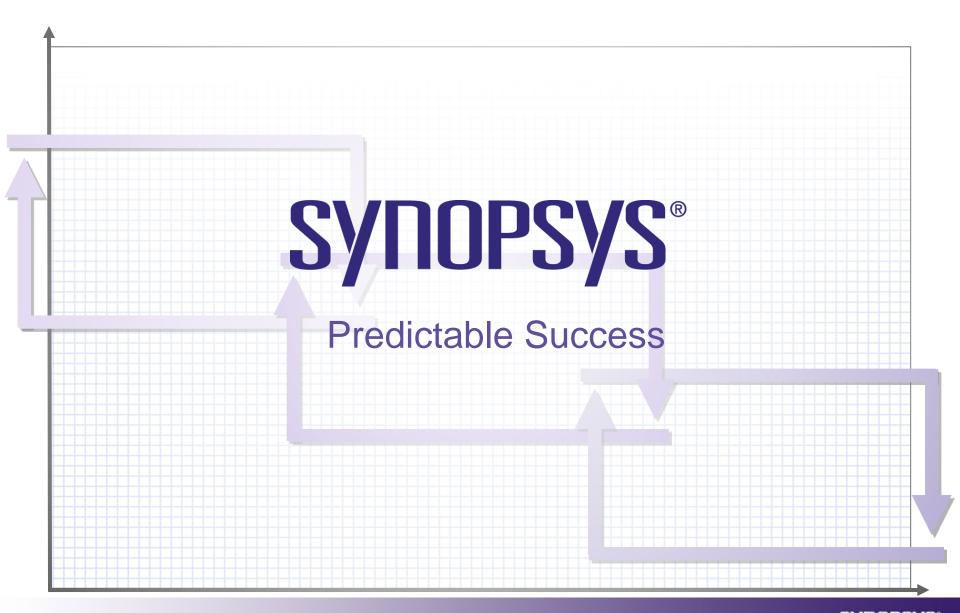

### **FPGAs Today**

#### FPGAs have evolved, becoming heterogeneous

Hard core processors, Ethernet cores, Giga-bit transceivers

Legacy features (known mitigation techniques)

**New features**

#### Xilinx V5FXT Datasheet

### FPGA Embedded PowerPC outperforms radiation hardened RISC processors

| Processor      | Mongoose V | RAD6000 | RAD750 | Virtex4 PPC405 | Virtex 5 PPC440 |

|----------------|------------|---------|--------|----------------|-----------------|

| Dhrystone MIPS | 8          | 35      | 260    | 900            | 2,200           |

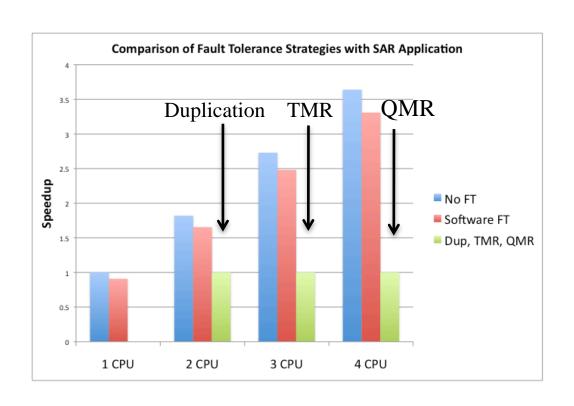

### Software Fault Tolerance vs. Traditional Mitigation

- Software-based approach leverages additional hardware for useful computation

- Heartbeats and assertions cause minimal overhead

- Checkpoints are taken according to the expected upset rate

Software fault tolerance allows more computation and fewer wasted cycles

### **Evaluating Fault Tolerance**

- Several options: radiation testing, laser testing, software fault injection

- Software provides a low-cost way of evaluating fault tolerance at-speed

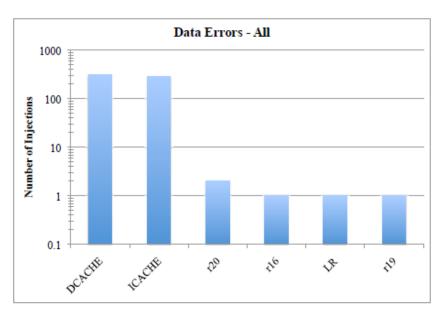

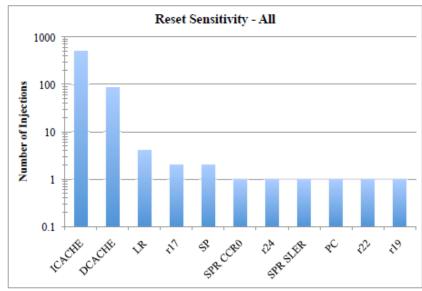

- We can now inject faults into registers, caches, memories through software

### **Summary and Open Questions**

- Devices and software are becoming more complex

- □ Current strategies don't scale

- □ Start to push fault tolerance to the application-level

- We can help to provide some fault tolerance constructs

- □ Checkpointing, heartbeats, control flow assertions, etc.

- **■** Programmers must leverage application-specific details

- Improve application efficiency

- **■** Improved detection

- Software fault injection is becoming more rigorous

- □ Complements radiation and laser testing strategies

- □ Level of fault detail much higher than radiation and laser testing

- □ Inexpensive can inject faults over days, weeks costing only board time

- Further work is needed to correlate software fault injection to radiation and laser results.