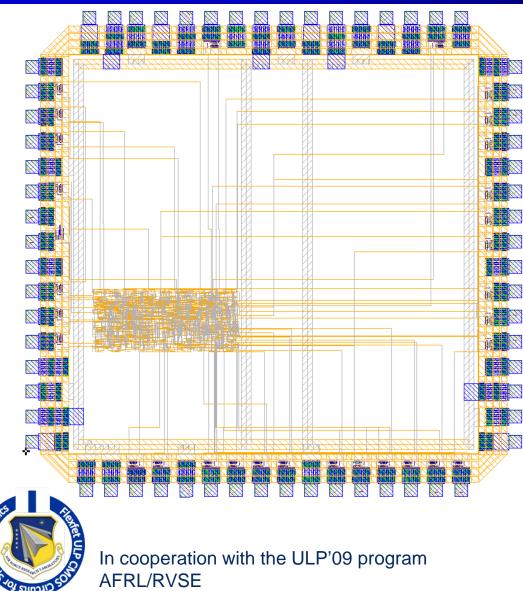

This work is sponsored by the Air Force Research Laboratory (AFRL/RVSE) TPOC: Mr. Keith Avery

### A SPA-1 ASIC Operating at 0.5V Fabricated in 130nm Double Gated CMOS

24 August 2011

©2011 American Semiconductor, Inc. All rights reserved.

- Phase 1 SBIR Feasibility Demonstration

- Ultra low power PIC (picL) microprocessor core

- Performance capable of meeting ASIM needs

- Radiation tolerant for space applications

- Proved feasibility of Double Gate Flexfet technology for ASIC development

- Phase 2 SBIR Build Prototypes of SPA-1 Mini-PnP ASIC

- Phase 3 SBIR Technical Qualifications, Flight Testing, and other ASIM Derivatives (SPA-U, SPA-S, ...)

**Program Vision**

2

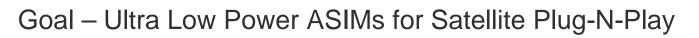

SPA-*x* Space Plug-and-play Avionics

3

©2011 American Semiconductor, Inc. All rights reserved.

Source: J. Lyke, "Bringing the Vision of Plug-and-play to High-Performance Computing on Orbit" HPEC 2009, Sept. 2009

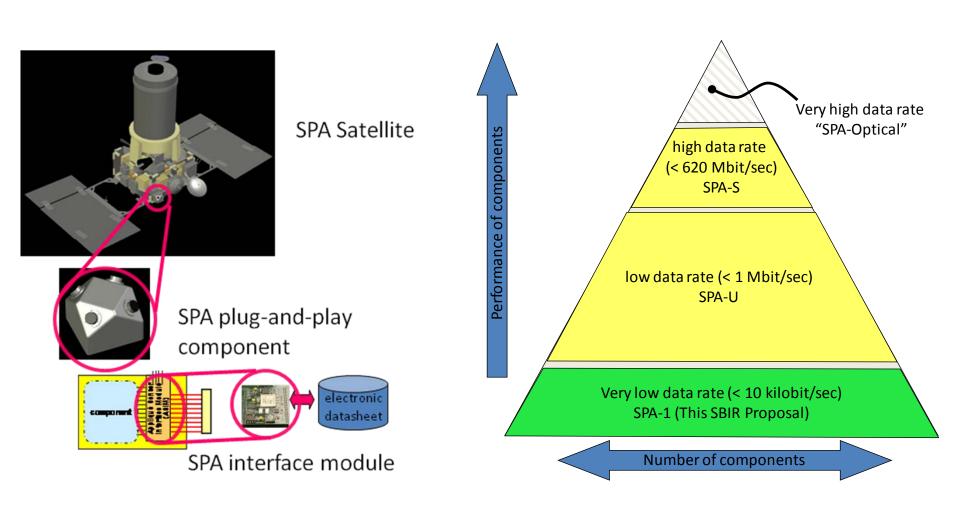

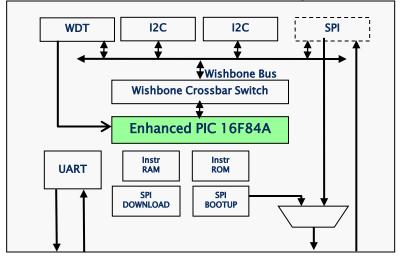

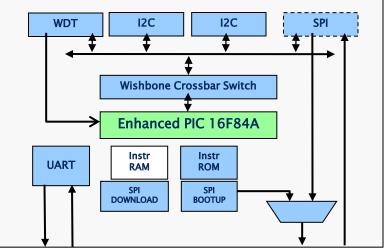

### AFRL SPA-1 Mini-PnP Block Diagram

4

# rights reserved.

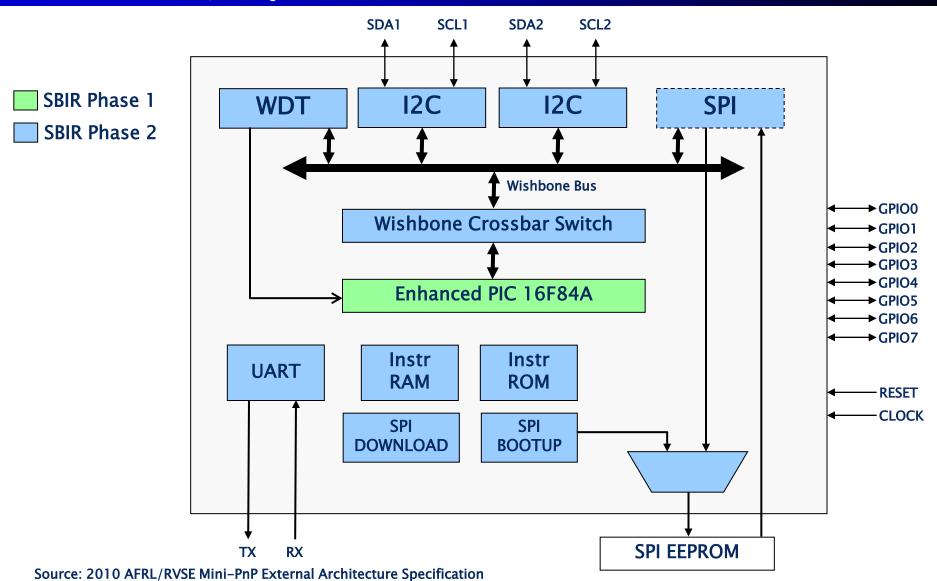

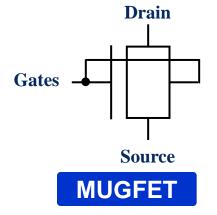

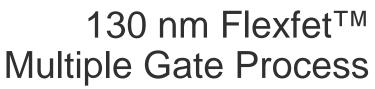

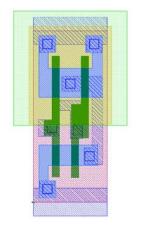

### Flexfet features

- MIGFET (Multiple Independent Gate FET)

- MUGFET (Multiple Gate FET)

- Fully depleted SOI MOSFET Top Gate

- Self-aligned JFET Bottom Gate

Benefit Dynamic Threshold Control

<u>Benefit</u> Ultra Low Power

BOX

©2011 American Semiconductor, Inc. All rights reserved.

**American Semiconductor Inc.**

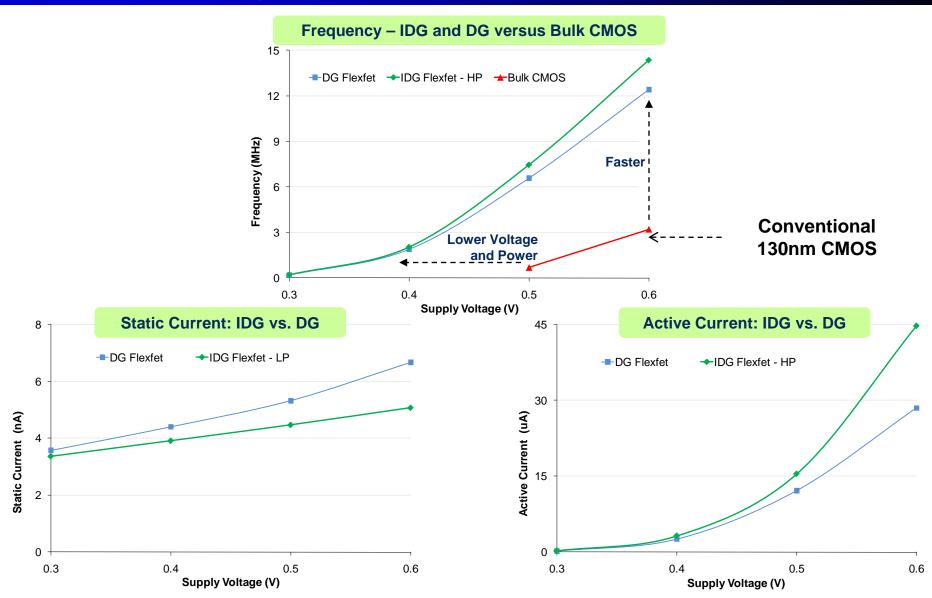

- Ring oscillator performance comparison

- > 130nm Flexfet IDG, DG, and high volume commercial bulk CMOS

- > 25 inverters with loading of 4x inverter load plus wiring capacitance

### Flexfet vs. Bulk CMOS Technology Comparison

7

©2011 American Semiconductor, Inc. All rights reserved.

**American Semiconductor Inc.**

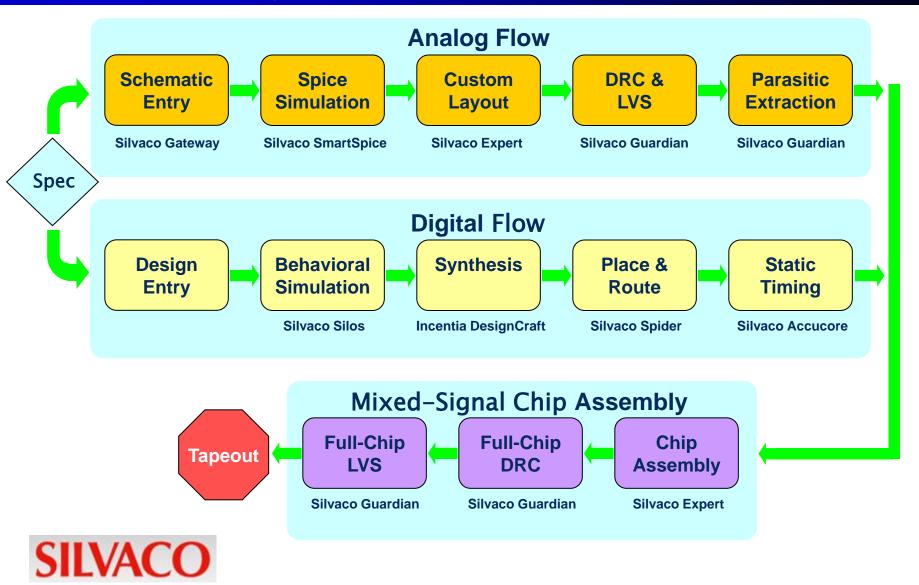

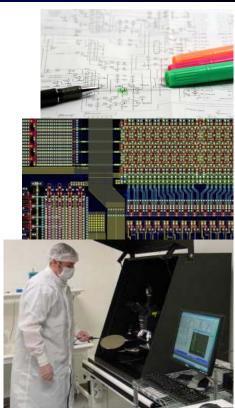

**Design Flow and Tools**

8

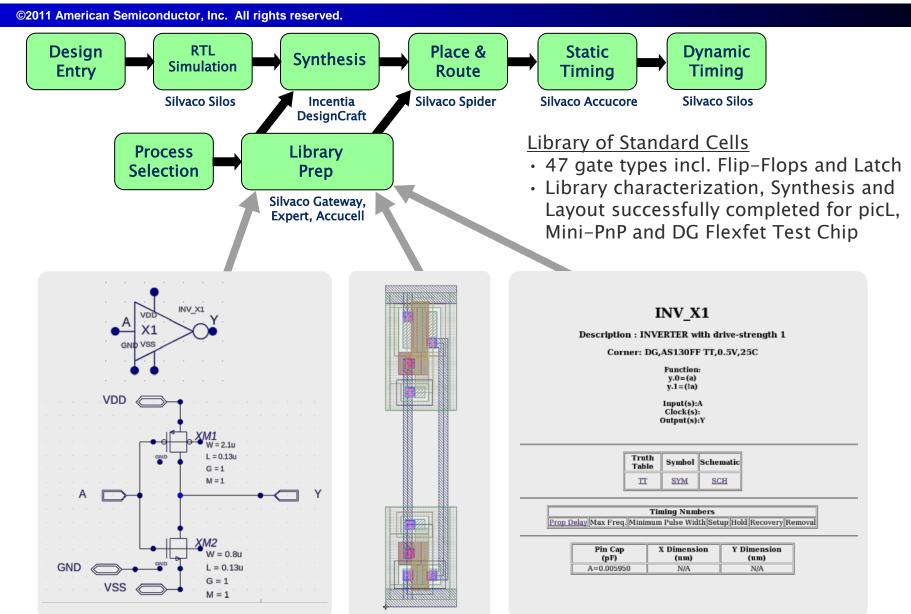

### Microprocessor Core Development

9

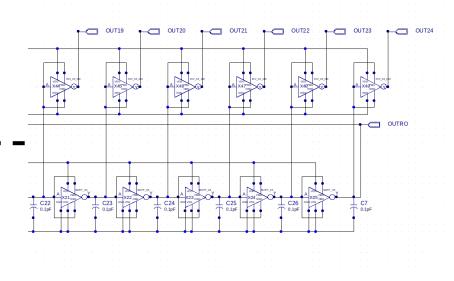

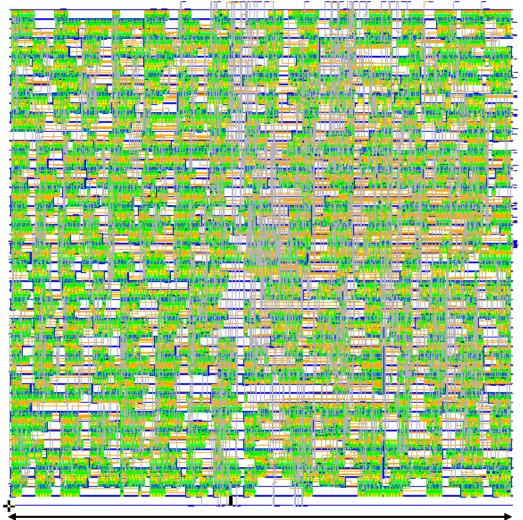

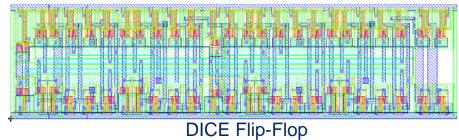

## American Semiconductor Inc. picL Core Place and Route

10

©2011 American Semiconductor, Inc. All rights reserved.

#### AFRL Mini-PnP Block Diagram

- picL ULP Core

- PIC 16F84A Core

- 50MHz Synthesis at 0.5V

- Clock tree inserted

- 2063 components

- 2420 signal nets, 1clock net

- 3 layer metal with local interconnect

700um

## Synthesis Comparison

11

©2011 American Semiconductor, Inc. All rights reserved.

| 50MHz synthesis                  | Flexfet<br>0.5V, 130nm | Bulk CMOS<br>1.5V, 130nm | Unit |

|----------------------------------|------------------------|--------------------------|------|

| Cells used                       | 2063                   | 1610                     | #    |

| Total Cell Input switching power | 0.43                   | 1.41                     | mW   |

| Leakage Power                    | 61.9                   | 45.2                     | nW   |

| Average Leakage power per cell   | 30.2                   | 28.1                     | pW   |

• No area penalty for Flexfet's second gate

| Std Cell Example     | Flexfet<br>130nm (um <sup>2</sup> ) | Bulk CMOS<br>130nm (um <sup>2</sup> ) |

|----------------------|-------------------------------------|---------------------------------------|

| NAND2, NOR2          | 58.3                                | 53.7                                  |

| D-type Flip-Flop     | 279.9                               | 348.5                                 |

| Inverter x1          | 46.7                                | 40.3                                  |

| Total picL cell area | 183,246                             | 183,986                               |

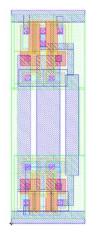

### NAND Gates

DG Flexfet 130nm

Bulk CMOS 130nm

4.5um X 12.96um

4.9um X 12.1um

### SPA-1 Mini-PnP Place and Route

#### ©2011 American Semiconductor, Inc. All rights reserved.

#### AFRL Mini-PnP Block Diagram

#### Top Level Mini-PnP

- Synthesized ROM

- Required Latches, Set and Reset

FFs, and Tri-State buffers

- 50MHz synthesis at 0.5V

- Clock tree inserted

- 14504 Components

- 14987 Signals, 1 clock net

- 3 Layer metal

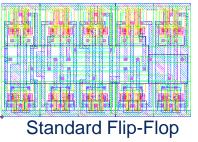

**Radiation Tolerance**

- SEL: Flexfet is an SOI process (inherently immune to latch-up)

- TID: Flexfet bottom gate is designed to minimize the effect of charge trapped in the BOX

- SET: Cell library design Rising and falling logic delays were balanced to minimize pulse spreading associated with Single Event Transients

- SEU: Mitigation per AFRL recommendations

- Added DICE Flip-Flops to DG standard cell library

- EDAC to be incorporated into SRAM

- Radiation Testing

- Pending support and access to AFRL test facilities

#### ©2011 American Semiconductor, Inc. All rights reserved.

- Silicon in a Phase 1 SBIR

- Design and Layout using 0.5V DG Flexfet cell library and digital design flow developed for picL

- Demonstrates 0.5V DG Standard Cells

- Evaluates SPICE models against silicon results

- Enhances Phase 2 effort

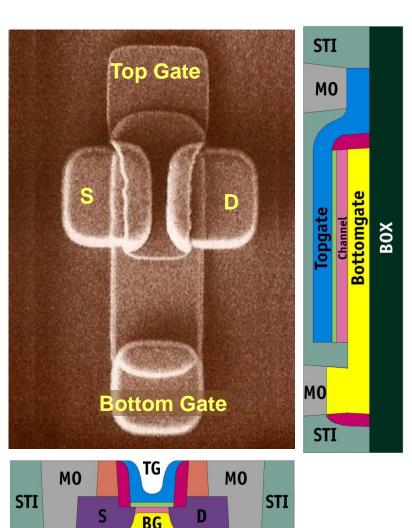

#### Test Chip Circuits

- 16-bit configurable Timer

- Scan chain with all combinatorial logic gates observable

- Ultra low voltage pads (0.5V)

- Clock oscillator for use with external crystal

Summary

15

- Phase 1 Complete

- Technology evaluation

- Microprocessor core selection

- Library preparation and design flow development

- Performance, power, and radiation tolerance analysis

- Test circuits in silicon

- Initial place and route of SPA-1 ASIM RTL

- Phase 2 Awaiting Contract

- ASIM ULP SPA-1 Prototype Design Start 2011

- Detailed device specification

- RTL design optimization

- Rad-hard SRAM with compiler

- Rad-hard ROM with compiler

- I/O library

- 1<sup>st</sup> Silicon ULP SPA-1 Prototype 2012

- 2<sup>nd</sup> Silicon ULP SPA-1 Prototype 2013

- Creates Platform and Design Capability for Derivative Products

# Thank You

### View a video demonstration of ultra-low-power Flexfet at americansemi.com/Flexfet

© 2011 American Semiconductor, Inc. All rights reserved. American Semiconductor Inc., the American Semiconductor logo, Flexfet, FleX, and the Flexfet logo are trademarks of American Semiconductor, Inc. All other trademarks are the property of their respective owners.