## Non Volatile Flash Memory Radiation Tests

Farokh Irom, Duc N. Nguyen and Greg Allen Jet Propulsion Laboratory, California Institute of Technology Pasadena, CA 91109

The research in this talk was carried out at the Jet Propulsion Laboratory, California Institute of Technology, under contract with the National Aeronautics and Space Administration (NASA), under the NASA Electronic Parts and Packaging Program.

Copyright 2012 California Institute of Technology Government Sponsorship Acknowledged.

- Commercial flash memory industry has experienced a fast growth in the recent years, because of their wide spread usage in cell phones, mp3 players and digital cameras

- On the other hand, there has been increased interest in the use of high density commercial nonvolatile flash memories in space because of ever increasing data requirements and strict power requirements

- Because of the complex structure of flash memories; they cannot be treated as just simple memories in regards to testing and analysis. It becomes quite challenging to determine how they will respond in radiation environments

- Samsung 1,2,4 and 8Gb

- Micron Technology 1,2,4,8,16, 32 and 64Gb

- Feature sizes from 120-25 nm

#### TEST FACILITIES

- » SEU MEASUREMENTS BNL RADEF TAMU

- » TID MEASUREMENTS JPL Co-60

#### TEST METHODS

- Data were taken using a commercial memory tester from JDI

- Prior to irradiation, the DUTs were programmed with all '0' pattern

- The sample size for all measurements was three

#### SEU MEASUREMENTS

- The DUTs were etched to remove the plastic packaging and expose the die to the ion beam

- During high LET SEU measurements the beam flux was set to ~ 2x10<sup>2</sup> ions/cm<sup>2</sup>/sec and the DUT was irradiated for 10-12 seconds in order to reduce the likelihood of occurrence of SEFIs in a given run

#### SEU MEASUREMENTS

During irradiation, the DUT was dynamically operated in READ mode. After irradiation and the completion of the final READ cycle that was started during irradiation, the device's power was cycled, the DUT was read again, checked for errors, and logged. This method insured that the errors are from bit upsets in the FGs.

#### TID MEASUREMENTS

- Dose rate of 50 rad (Si) per second at room temperature

- In all measurements the DUTs were under static bias (3.6V) during irradiation, but not actively exercised

- Measurements were made in No Refresh Mode (READ only) & Refresh Mode (Erase/Program/Read)

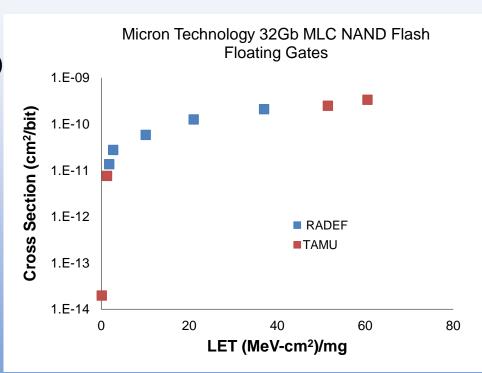

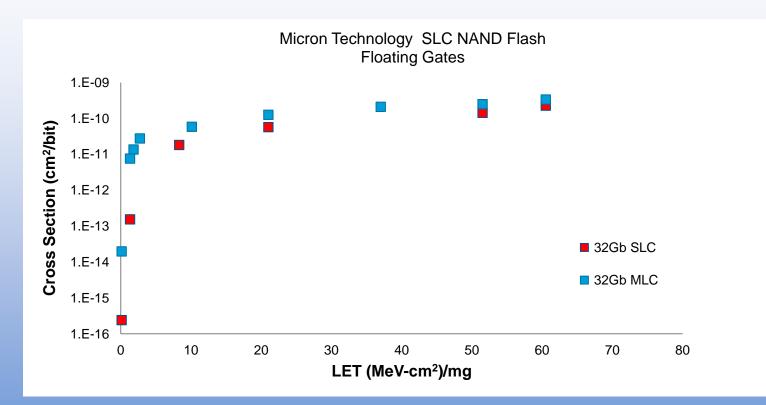

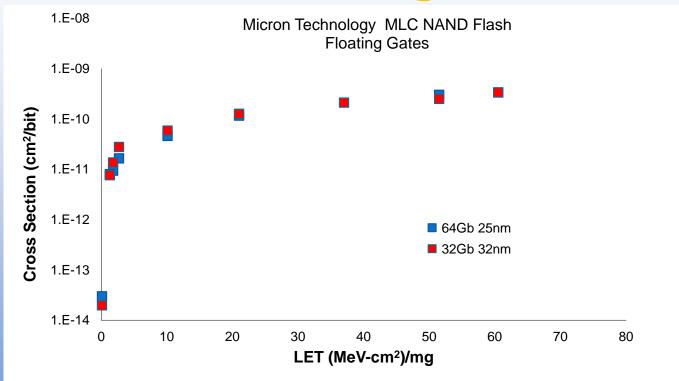

- SEU events were measured at RADEF and TAMU on MLC 32Gb (LET 0.1- 62 MeV-cm<sup>2</sup>/mg)

- The FG SEU cross-section per bit is on the order of 3×10<sup>-10</sup> cm<sup>2</sup>/bit

- The FG SEU rate is 5.1x10<sup>-9</sup> per bit per day for the background GCR environment

SEU cross-section for Micron 32Gb MLC NAND flash memory. Error bars are smaller than the plotting symbols

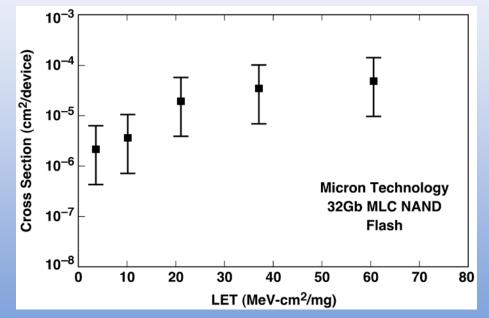

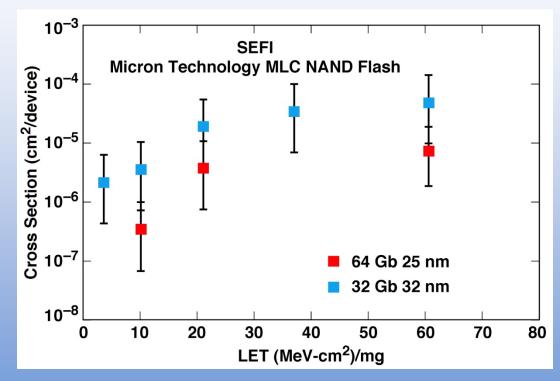

- SEFI events were measured at RADEF on MLC 32Gb (LET 3.6- 62 MeV-cm<sup>2</sup>/mg)

- The SEFI cross-section per bit is on the order of 5×10<sup>-5</sup> cm<sup>2</sup>/bit

- The SEFI rate is 2.1x10<sup>-4</sup> per device per day for the background GCRs environment

SEFI cross-section for Micron Technology 32Gb MLC NAND flash memory

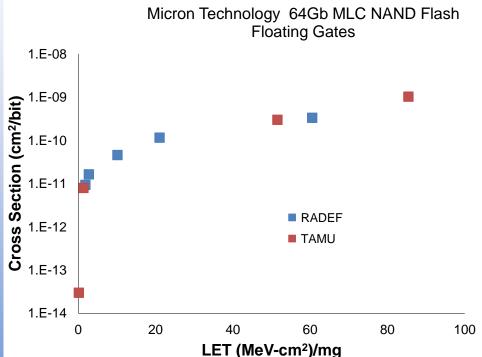

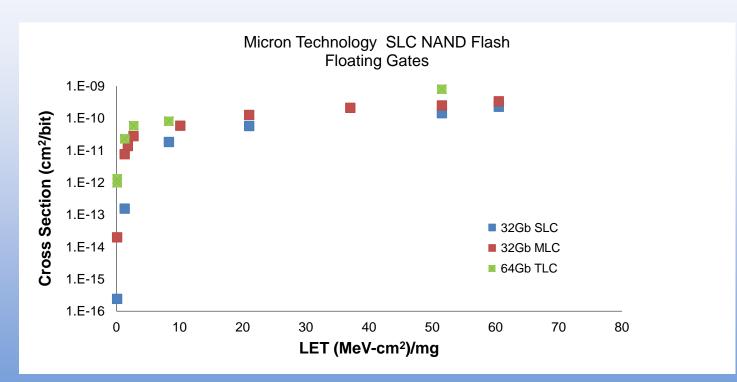

- SEU events were measured at RADEF and TAMU on MLC 64Gb

<sup>1</sup> (LET 0.1- 85 MeV-cm<sup>2</sup>/mg) = 1

- The FG SEU cross-section per bit is on the order of 1×10<sup>-9</sup> cm<sup>2</sup>/bit

SEU cross-section for Micron Technology 64Gb MLC NAND flash memory. Error bars are smaller than the plotting symbols

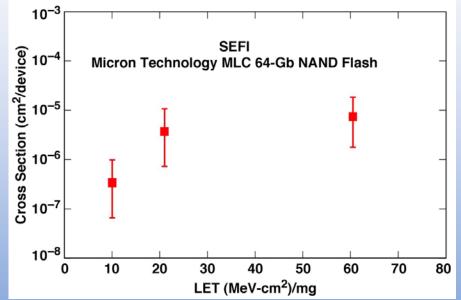

- SEFI events were measured at RADEF on MLC 64Gb (LET 10.1- 62.5 MeV-cm<sup>2</sup>/mg)

- The SEFI cross-section is on the order of 7×10<sup>-6</sup> cm<sup>2</sup>/device

SEFI cross-section for Micron Technology 64Gb MLC NAND flash memory.

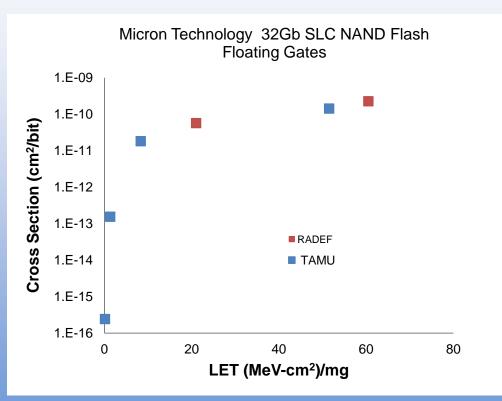

- SEU events were measured at RADEF and TAMU on SLC 32Gb (LET 0.1- 62 MeV-cm<sup>2</sup>/mg)

- The FG SEU cross-section per bit is on the order of 2×10<sup>-10</sup> cm<sup>2</sup>/bit

SEU cross-section for Micron 32Gb SLC NAND. Error bars are smaller than the plotting symbols

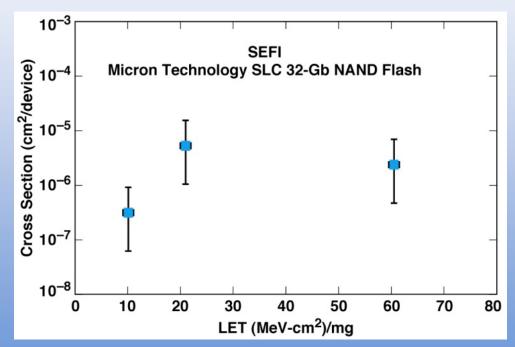

- SEFI events were measured at RADEF and TAMU on SLC 32Gb (LET 10.1- 62 MeV-cm<sup>2</sup>/mg)

- The SEFI cross-section per bit is on the order of 2×10<sup>-6</sup> cm<sup>2</sup>/device

SEFI cross-section for Micron 32Gb SLC NAND flash memory.

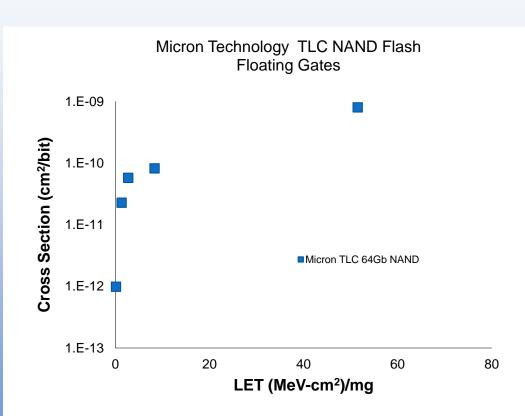

- SEU events were measured at TAMU on TLC 64Gb (LET 0.1- 51 MeV-cm<sup>2</sup>/mg)

- The SEU cross-section per bit is on the order of 8×10<sup>-10</sup> cm<sup>2</sup>/bit

FG SEU cross-section for Micron 64Gb TLC NAND flash memory. Error bars are smaller than the plotting symbols.

Comparison of SEU cross-section for Micron 32Gb SLC and MLC NAND flash memories. Error bars are smaller than the plotting symbols.

To be presented at the 3rd NASA Electronic Parts and Packaging (NEPP) Program Electronic Technology Workshop June 11-13, 2012, NASA GSFC, Greenbelt, MD.

Comparison of SEU cross-section for Micron SLC, MLC and TLC NAND flash memories. Error bars are smaller than the plotting symbols.

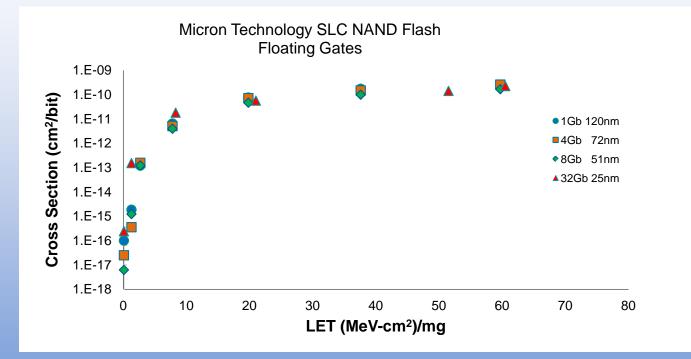

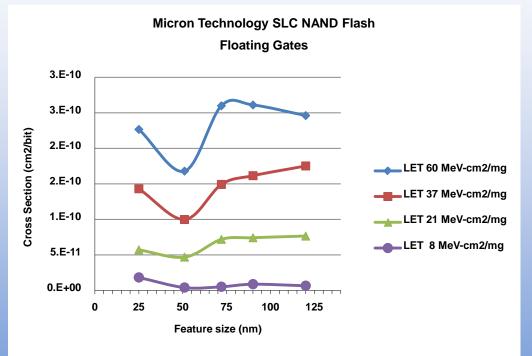

Scaling effect of FG SEU cross-sections for Micron SLC NAND flash memories. Error bars are smaller than the plotting symbols

- No noticeable scaling effect for the 120 to 72nm feature sizes

- There is a reduction in the SEU cross section at high LETs for 50nm feature size and increase cross section at 25nm

SEU cross-sections for Micron SLC NAND flash memories. Error bars are smaller than the plotting symbols

Scaling effect of FG SEU cross-section for Micron MLC NAND flash memories. Error bars are smaller than the plotting symbols

Scaling effect of SEFI cross-section for Micron MLC NAND flash memories

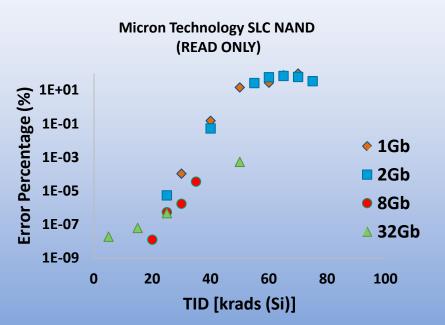

### TID Results Scaling

- The SLC parts (1, 2, 4, 8 and 32Gb) were irradiated up to 80 krad

- For a particular TID level, the number of errors scales with feature size

Percentage of data errors versus dose for Micron Technology 1, 2, 8 & 32Gb SLC NAND flash memory

- The FG SEU cross section doesn't scale with feature size, except for SLC 8-32Gb devices which are built with 51-25 nm feature size. The FG SEU per bit cross section for SLC 1Gb device which is built with 120 nm feature size is 60% higher than SLC 32Gb device which is build with 25nm at high LETs

- No change in threshold LET was noticed in the range of 120-25 nm feature size

- In general the TID response improves with scaling