# Update on Reliability Testing of CGA/LGA Packages by

Reza Ghaffarian, Ph.D.

**JPL-Caltech**

(818) 354-2059

Reza.Ghaffarian@JPL.NASA.com

Jet Propulsion Laboratory National Aeronautics & Space Administration California Institute of Technology

Copyright 2012 California Institute of Technology

Government sponsorship acknowledged

NASA Electronic Parts and Packaging Program (NEPP) 3<sup>rd</sup> Annual Electronics Technology Program (ETW) NASA Goddard Flight Center (GSFC), Greenbelt, MD June 11-13, 2012 Published on nepp.nasa.gov

# Outline

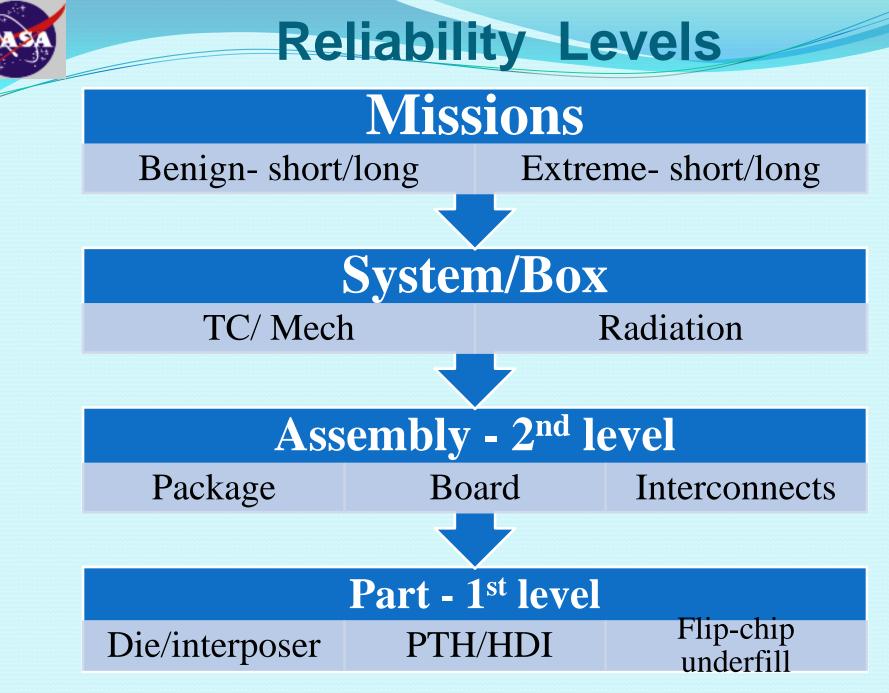

### Reliability Approaches

- Mission requirement/system level

- 2<sup>nd</sup> level, assembly/package

- 1<sup>st</sup> level, part

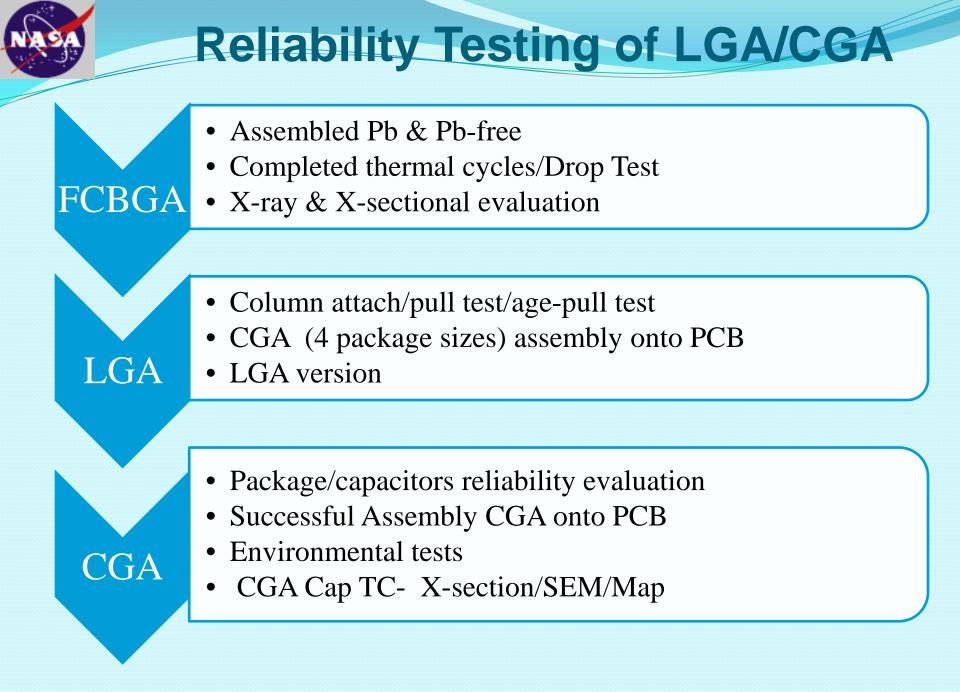

### CGA/LGA Reliability Test Results

- LGA/CGA

- Chip Cap., Optical/SEM characterization

- LGA/CGA assemblies

- CGAs, thermal cycles status

- Chip Cap., SEM/X-section/elemental maps after TCs

#### Summary

NEPP ETW 2012 @ NASA GSFC

## **SMT Array Reliability -**

### SMT

- Area Array (single/stack)

- PCB, (PTH/HDI)

- Interconnects (CBGA/CGA)

- Stake/Coat/Underfill

**Advanced Arrays**

- Hermetic/Non-H

- LGA

- FCBGA/interposer

# **SMT Array Reliability-II**

### **SMT/Advanced Arrays**

### Assembly, 2<sup>nd</sup> level

- Class Y, >1000 I/Os

- Hermetic, <1000 I/Os

- Interconnects, Pb & Pb-free

#### Part, 1<sup>st</sup> level

- Chip cap

- FC balls/underfill

- Interposer

NEPP ETW 2012 @ NASA GSFC

NEPP ETW 2012 @ NASA GSFC

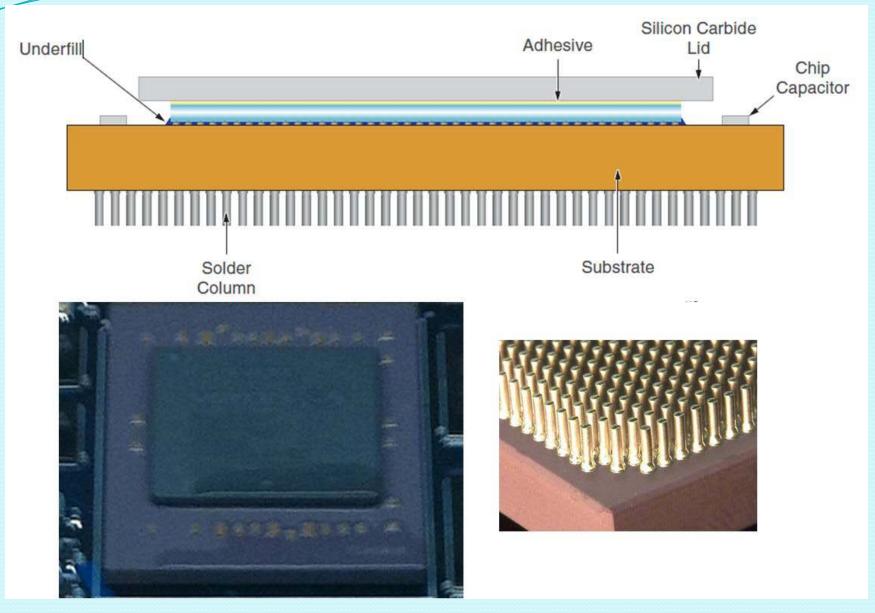

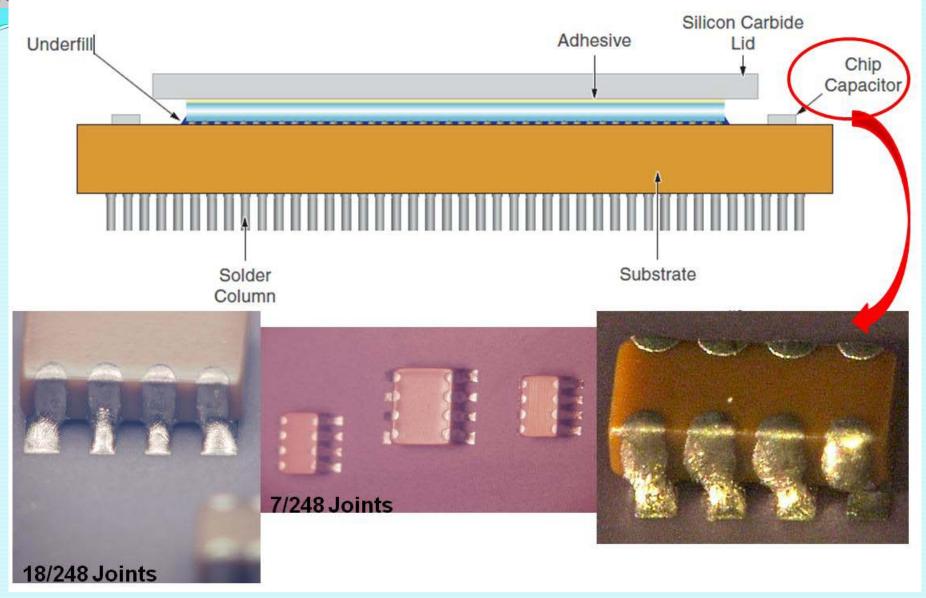

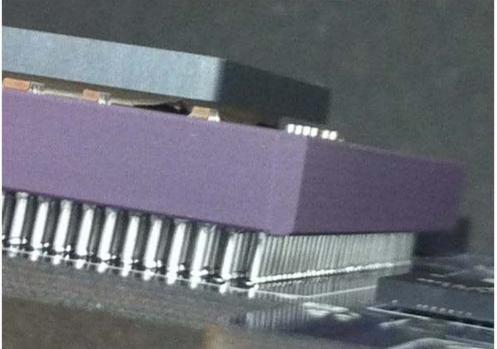

## **CGA with 31 Chip Capacitors**

NEPP ETW 2012 @ NASA GSFC

### CGA with 31 Chip Caps

NEPP ETW 2012 @ NASA GSFC

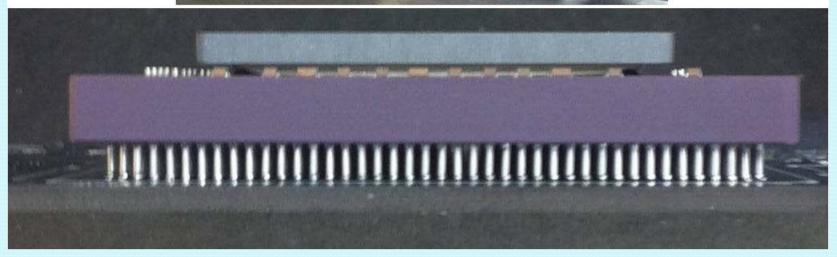

### **Two CGA Assembly**

NEPP ETW 2012 @ NASA GSFC

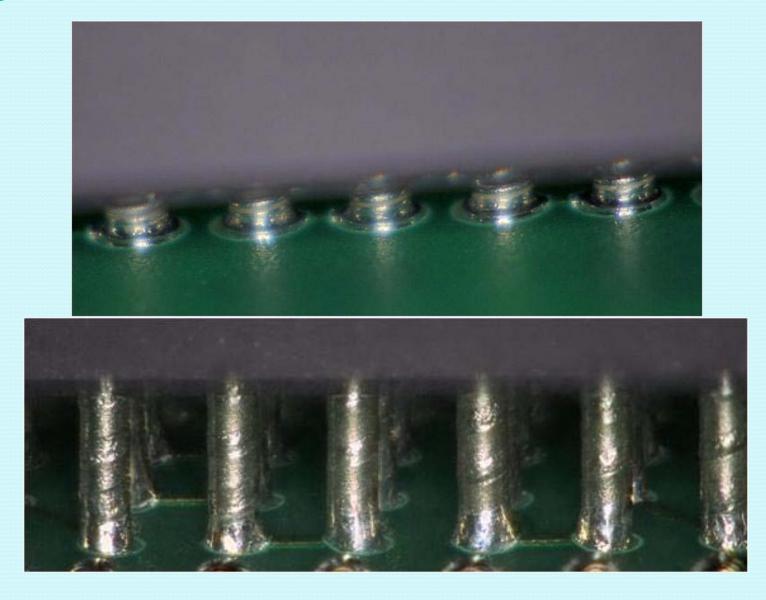

### **CGA Solder Joint Assembly**

NEPP ETW 2012 @ NASA GSFC

### Solder Joints/Columns for 2 CGAs

NEPP ETW 2012 @ NASA GSFC

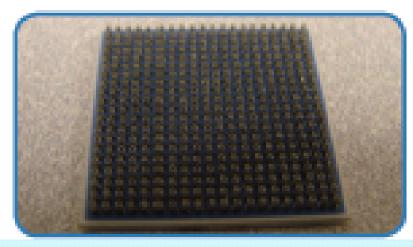

### LGA/CGA/Assembly

NEPP ETW 2012 @ NASA GSFC

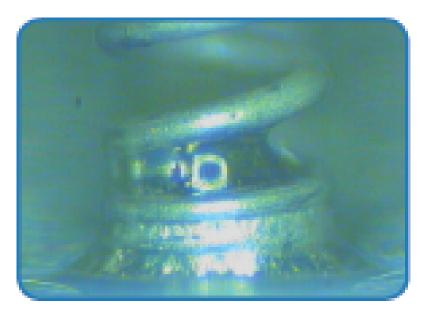

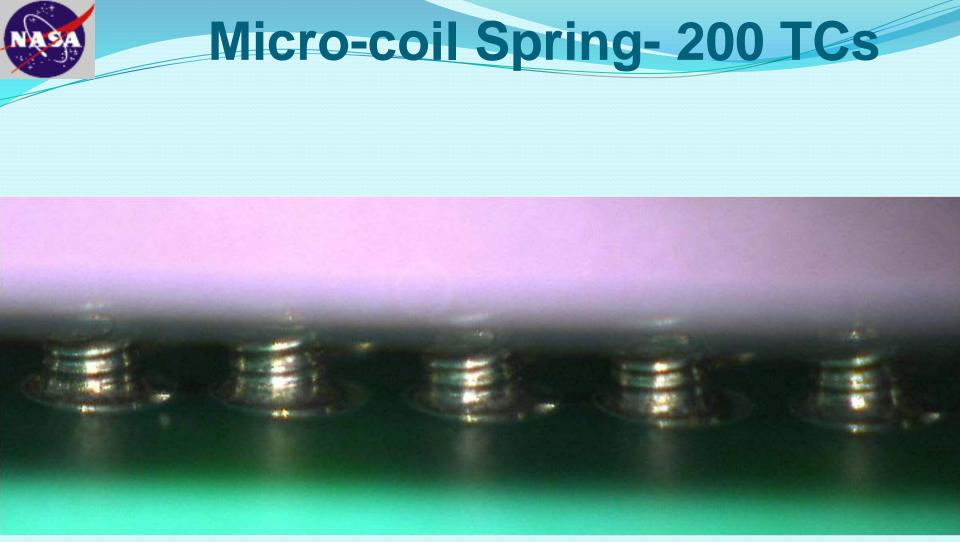

#### NASA Micro-Coil Spring License to STI Electronics Inc

#### MICRO-COIL SPRING ARRAY BY: MARK MCMEEN

#### INTRODUCTION:

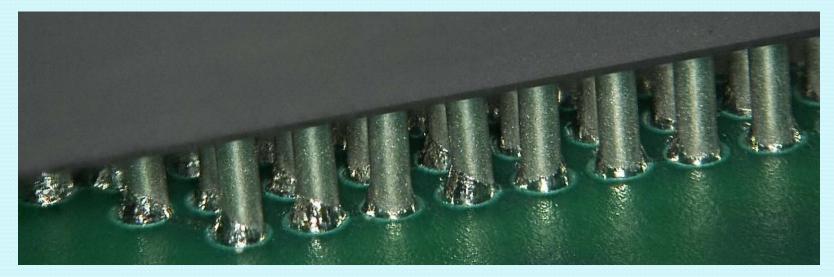

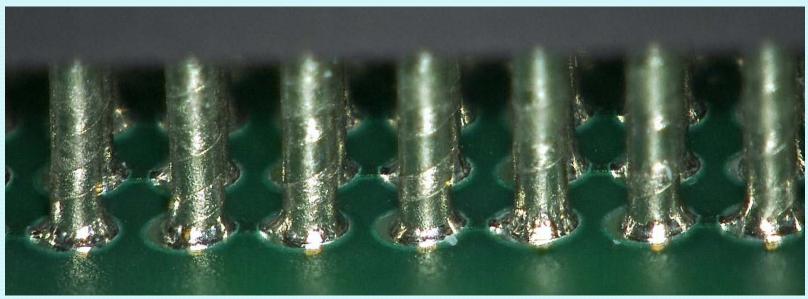

Micro-Coll Spring Array is being introduced as an improved alternative to standard rigid arrays to replace the Column Grid Array (solder columns) commonly used on Integrated Circuits (IC) with a very high lead count. The Micro – Coll Spring Array was developed by NASA for higher degree of reliability over conventional Column Grid Arrays and this technology was licensed to STI Electronics, inc. for its commercialization and production capability.

Micro springs will form a more robust solder joint. The interconnect of the spring to the substrate consists of the wire on one side of the spring resting on the solder pad in a circular pattern. The result is two separate solder joints along the length of the circular pin, one internal to the spring and one external to the spring.

#### **Micro-Coil Spring Column**

#### INNOVATION:

The Micro-Coll Spring Array consists of an IC connected to PC Board via micro springs. The springs are soldered to the IC substrate then the package is mounted to the PC substrate using conventional Pick and Piace equipment.

The flexibility of the micro springs provide a robust interconnect from the IC substrate to the PC substrate that is much more reliable than rigid interconnects such as Column Grid Arrays. The ability to be compliant and not rigid aids in long term reliability

#### SPEED/ THROUGHPUT IMPROVEMENTS: Micro-Coll Spring Array is installed using conventional Surface Mount Pick and Place equipment. This technology allows for the elimination of underfills because its capability for handling and distributing stress – compliance under loading allows the stresses to be negated.

#### QUALITY CONTRIBUTION:

The use of the micro coll springs provides contomity from the PC substrate to the IC substrate. The flexing of the springs will prevent solder cracks from forming by absorbing thermal or mechanical stress that would normally transfer to the solder joint via rigid interconnects.

#### COST BENEFITS:

Competitively priced to be lower than column grid array solder columns as well as lower production assembly costs for manufactured of the column grid array package.

#### ENVIRONMENTAL CONSIDERATION:

The objective from day one was to develop a solder column that could be compliant to environmental loading such as mechanical and thermal stress and thus create a more robust solder connection. The end of objective is greater reliability by surving longer thermal cycles and minimizing latigue fracturing.

#### EASE OF USE/IMPLEMENTATION:

The Micro-Coll Spring Array is a drop in replacement for a BGA column grid array packaging applications that want greater reliability and long term robustness.

#### MAINTAINABILITY/REPAIRABILITY:

The Micro-Coll Spring Array can be easily repaired using a standard BGA rework station and reworking of the column grid array. High temp solder is used for attachment to the component BGA package and then one can use leaded or lead free solder when attaching to the printed circuit board itselt.

NEPP ETW 2012 @ NASA GSFC

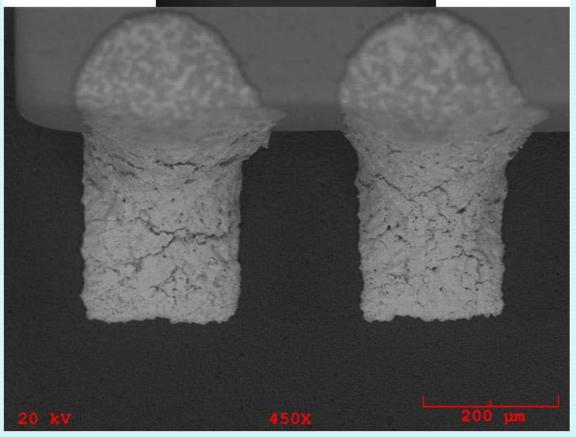

### Cap. Solder Joints after TCs

NEPP ETW 2012 @ NASA GSFC

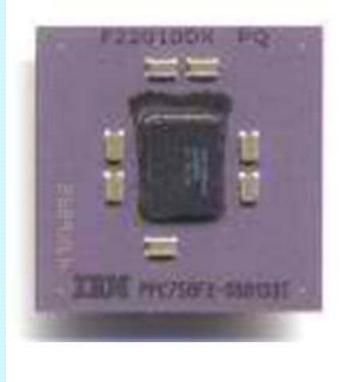

## **BME History**

#### BME Caps

- Decoupler Caps on Power PC, BGA type

- Advanced CGAs

#### Reliability of BME Caps BME/PME (NASA: Liu/Sampson, 2011, NEPP)

- Higher dielectric variations for same BME

- Denser and uniform microstructures

- 0.3-0.5 microns

- Thinner and more layers

- PME random failures under HALT

- HALT (25volt rated Caps, 155/165/175°C, 150/200/250Volts)

- BME early failure/Avalanche break down

- Fabrication defect

- Critical : Number of stack grains

- Longer- Wear out of dielectric

- MTTF, 10<sup>5</sup> years at RT (excluding early failures)

#### • Recom.

- Improve processing controls/defects

- Use below extrinsic defect triggering

NEPP ETW 2012 @ NASA GSFC

## **MLCC Capacitors**

• PME (precision Metal Electrode)

- Reliability (bias/temp) well established

- Mix of Palladium Silver Electrode

- BME (Base Metal Electrode)

- High density, commercial/cost

- Ni electrode

- Barium Titanate- BaTiO<sub>3</sub>

- Tetragonal (0/130C) on face centers, Barium at corners

- Titanium, 1% nanometer offset, voltage/move/storage

- Thinner dielectrics/more layers than PME

- Increase in capacitance/volumetric efficiency

- Reliability compromise?

NEPP ETW 2012 @ NASA GSFC

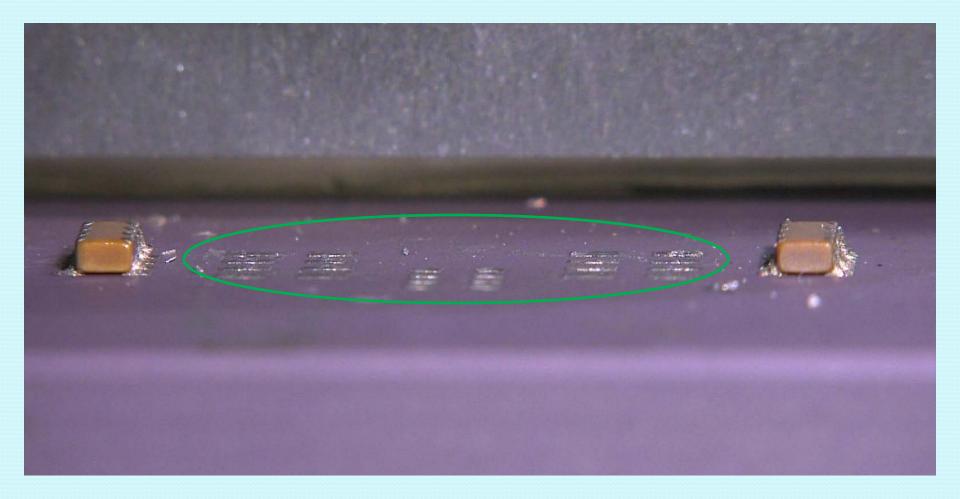

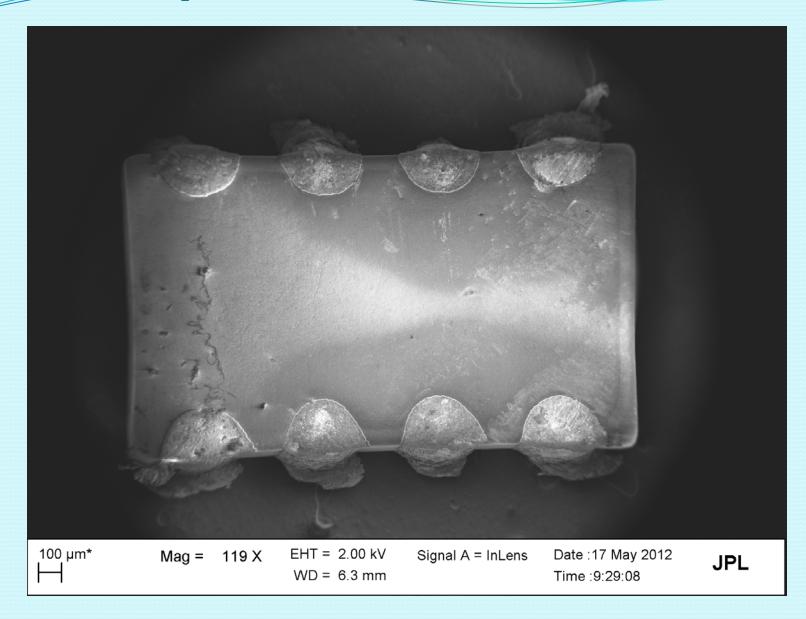

### **Caps Removed for Eval**

NEPP ETW 2012 @ NASA GSFC

## **Caps on CGA after TCs**

#### • CGA Thermal History

- Package subjected to thermal shock (-55/130°C)

- Reflow for Assembly ( 218°C)

- Additional TCs package on board

- Characterize CGA assemblies

- Caps Removal

- Mechanical

- Solder cut, then Caps pushed/removed

- Shear off by twisting, concern, mechanical damage

- De-soldering

- High Temp Solder

- Not tried yet, concern thermal shock

NEPP ETW 2012 @ NASA GSFC

## **Cap after TC/Removal**

#### NEPP ETW 2012 @ NASA GSFC

NEPP ETW 2012 @ NASA GSFC

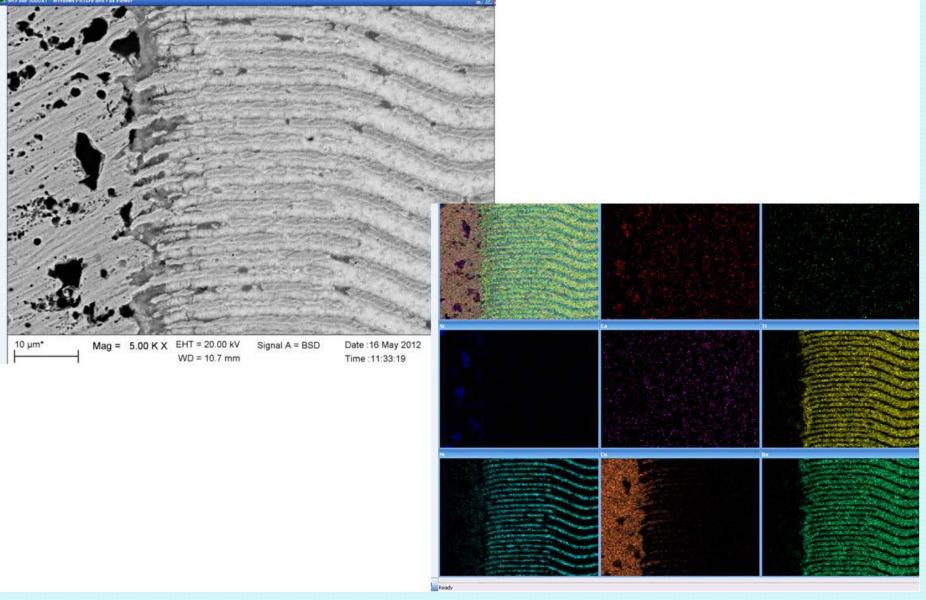

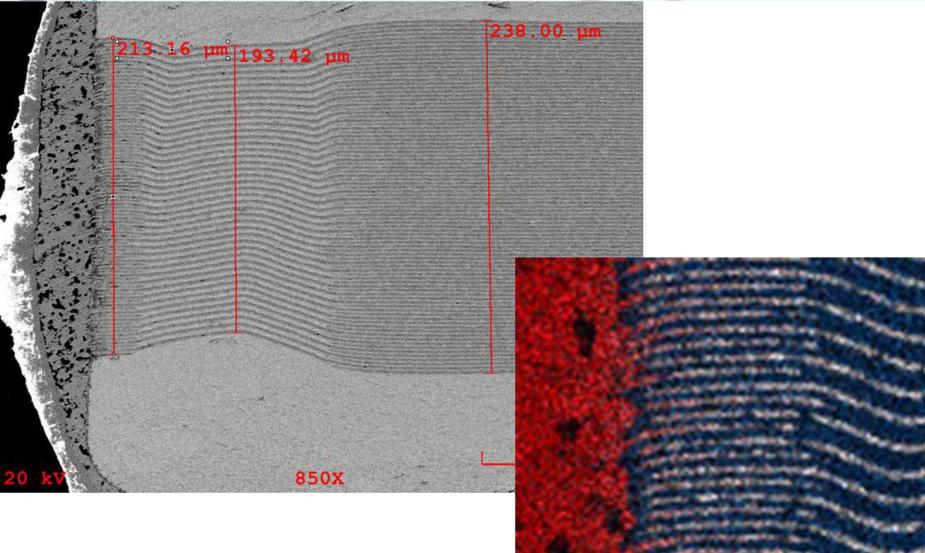

### **Elemental Map**

#### NEPP ETW 2012 @ NASA GSFC

### **Elemental Map**

NEPP ETW 2012 @ NASA GSFC

### Summary-I

#### Advanced LGA

- Success on Cu wrap column attach

- Column pull test as attached

- Column pull tests at intervals of aging at 125°C/500 hrs

- Success on Micro-coil spring column attach

- No signs of damage after 200 thermal cycles

- Advanced CGA

- Caps on CGA

- Inspected solder joint quality

- CGA thermal shock cycles

- No failures of caps

- One solder joint apparent separation

NEPP ETW 2012 @ NASA GSFC

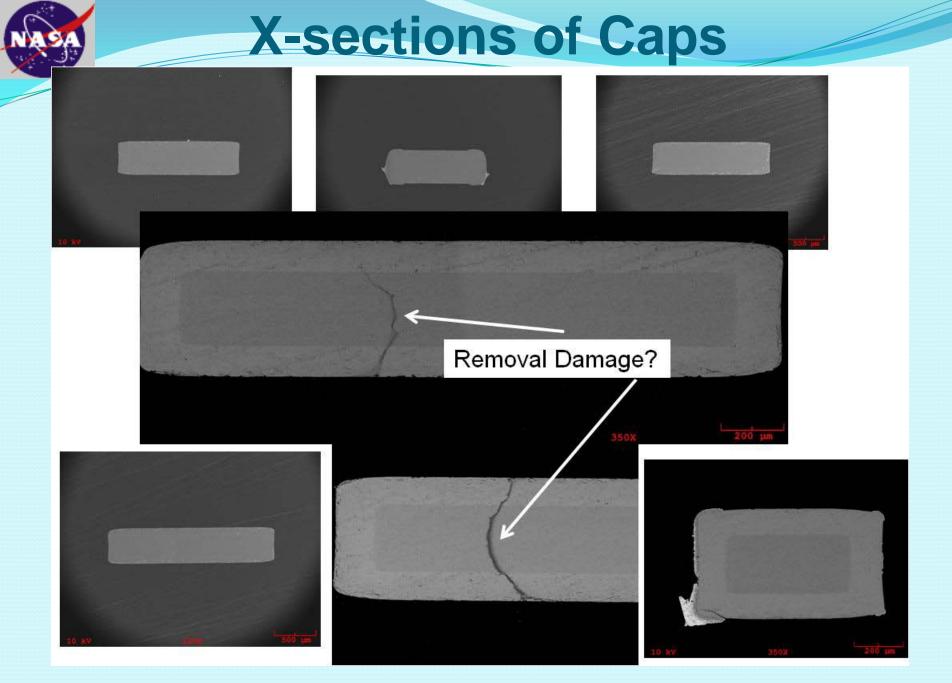

### Summary-II

#### Success on LGA/CGA on PCB Assembly

• Released interim report

#### Advanced LGA/CGA

- Reliability testing of CGA assemblies

- LGA/CGA & assembly on standard PCB

- Daisy chain monitoring when applicable

- Damage monitoring and NDE/SEM evaluation

- Caps after TCs

- Literature search understand reliability

- X-sectioned 6 caps, SEM evaluation

- Elemental Maps

- Caps are BME with BaTiO<sub>3</sub> cap/Ni electrodes/Cu terminals

#### • Design boards with HDI (microvia)

- Assemble onto HDI board/optimize process

- Reliability testing

#### • Active die, HDI, Reliability

- Use lessons learned for efficient resource utilization

- Release report

#### NEPP ETW 2012 @ NASA GSFC

# Acknowledgment

The research described in this publication is being conducted at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration.

Copyright 2012 California Institute of Technology. Government sponsorship acknowledged.

The author would like to acknowledge industry/university partners. Special thanks to the JPL fabrication and failure analysis lab personnel including Atul Mehta and Ronald Ruiz for their supports. The author also extends his appreciation to program managers of NASA Electronic Parts and Packaging Program (NEPP) including co-managers Michael Sampson and Kenneth LaBel at GSFC, and Drs. Charles Barnes and Douglas Sheldon at JPL, for their continuous support and encouragement.

# References http://NEPP.nasa.gov