## DC DC Converters meets the FPGA

Jack Shue GSFC

## Start with some Quotes

Nobody trust a computer simulation except the guy that did it, and everybody trust experimental data, except the guy who did it. Why not combine the two and get results everybody can mistrust a little.

Tony Kordyban Hot Air Rises and Heat Sinks

## Start with some Quotes

If it were not for the FPGA, the DC DC Converter would be the number one problem on Center

#### What can we gain?

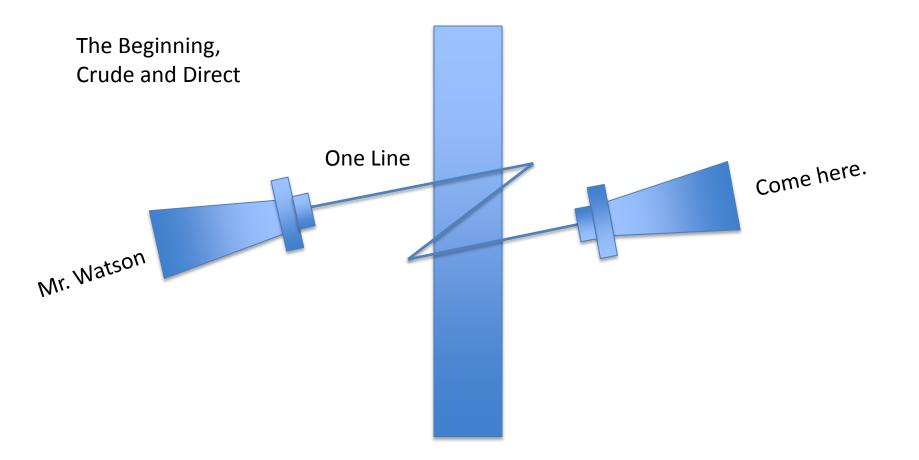

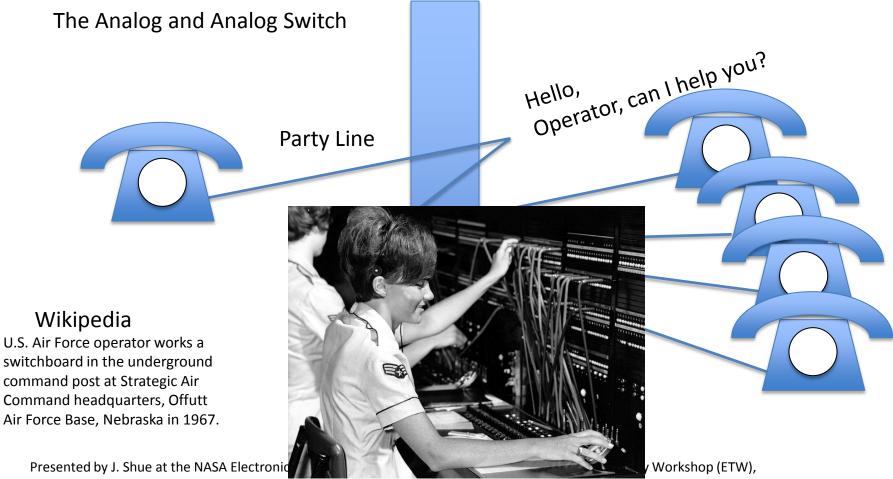

## Historical Note: A Lesson from the Phone Industry

# Historical Note a Lesson from the Phone Industry

NASA Goddard Space Flight Center in Greenbelt, MD, June 11-13, 2012 and published on nepp.nasa.gov.

## Historical Note a Lesson from the Phone Industry

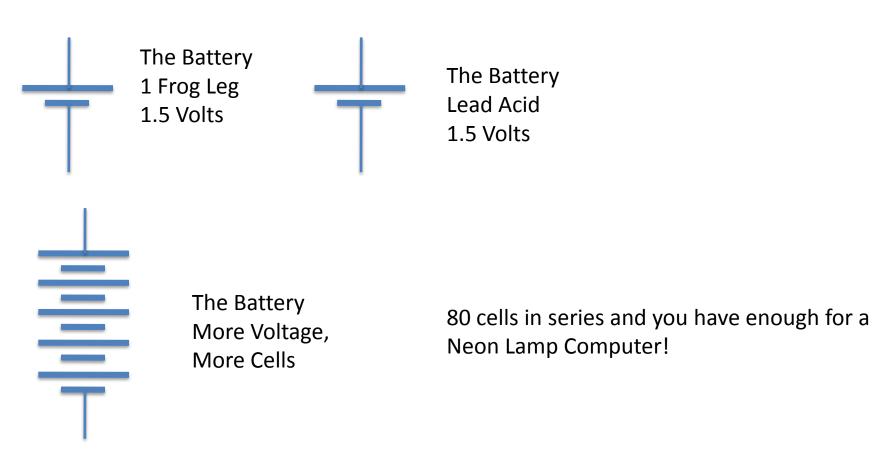

## The Original Voltage Control

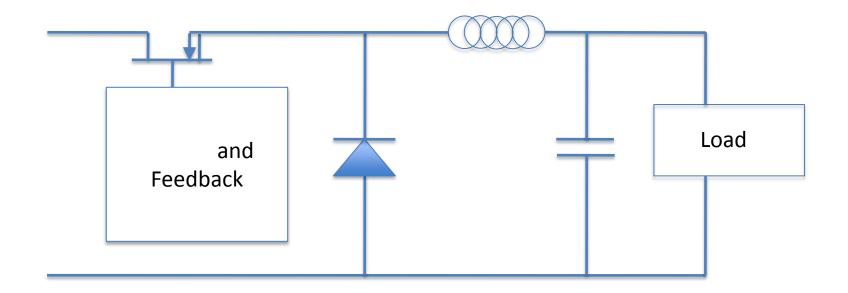

## **Buck Converter**

### **Quick Tutorial on DCDC Converters**

#### Analog Feedback

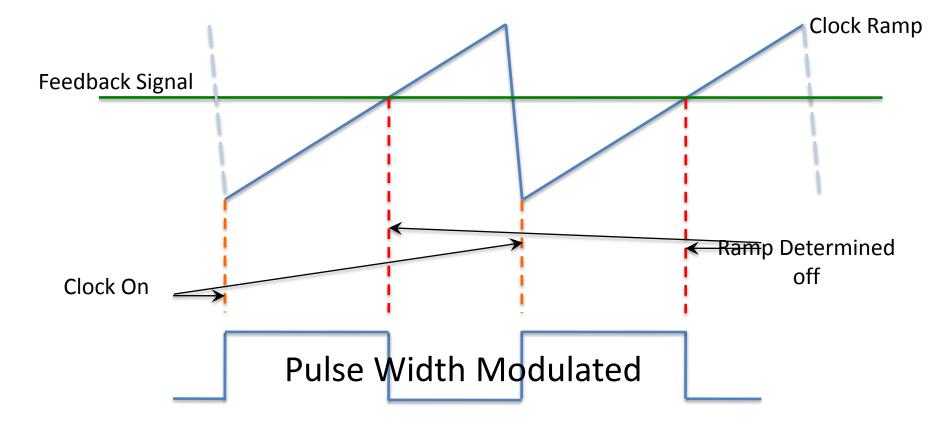

## Quick Tutorial on DCDC Converters The PWM

## **Controls - Active**

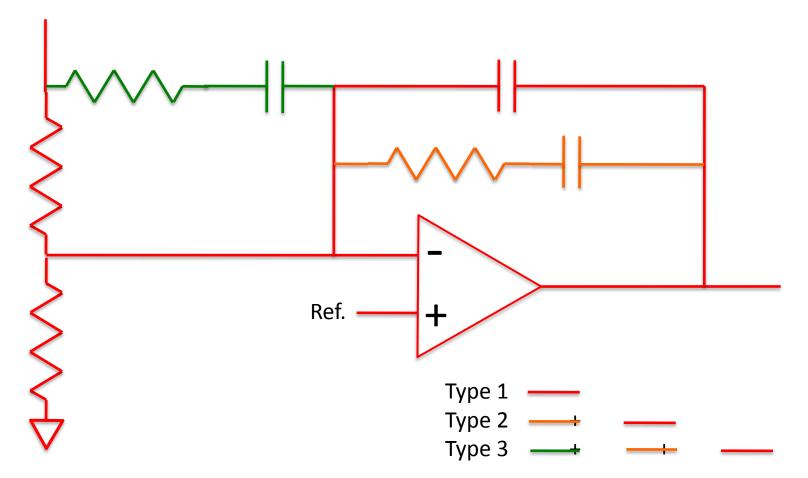

Signal filtering (Feedback Loop Analog)

### **Quick Tutorial on DCDC Converters**

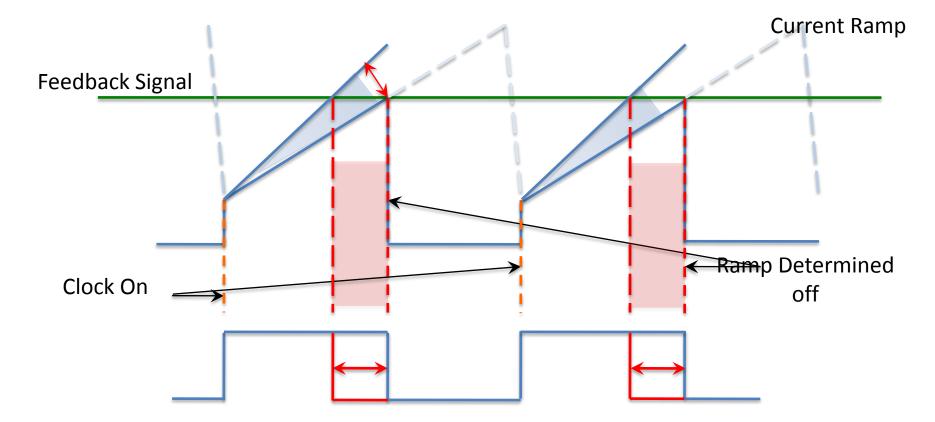

#### Analog / Current Controlled Feedback

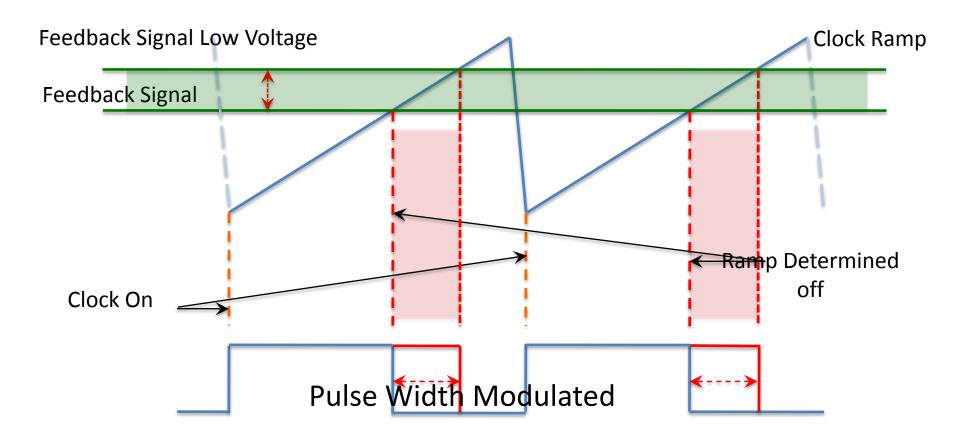

## **Quick Tutorial on DCDC Converters**

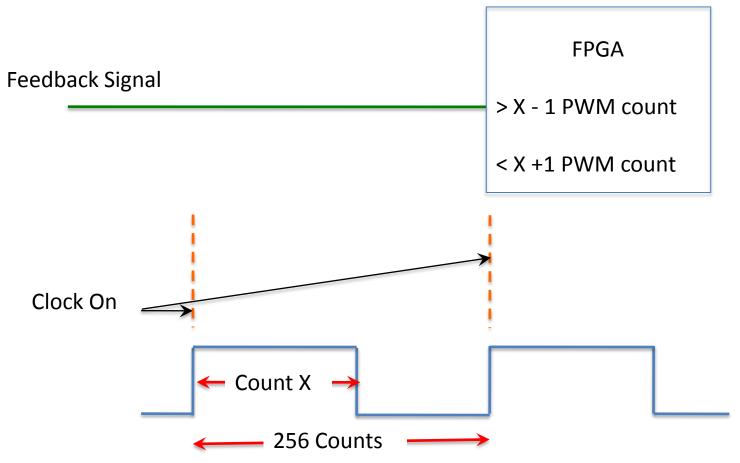

#### **Digital Feedback**

Presented by J. Shu Grt at her Ecount Baforn different gran Ner ty tronics Technology Workshop (ETW), NASA Goddard Space Flight Center in Greenbelt, MD, June 11-13, 2012 and published on nepp.nasa.gov.

### **FPGA** Controls – Simple Passive

- Monitor Voltages

- Make adjustments in PWM.

For: Lower voltage = X - 1 count Same voltage = X Higher voltage = X + 1 count

## FPGA joins TWITTER!

FPGA can talk to themselves.

With self-monitoring, an FPGA could be able to ask for more power before normal feedback loop could respond, or even just before it needs it.

With FPGA protection, circuits could be added with no extra parts. Voltage Protection Current Limiting Power Correction

## **Digital Filtering**

Internal Noise Filtering External Noise Filtering Input Output

## FPGA could enable.

Active Noise Suppression

Use of Power Lines for Signal Lines

## FPGA Control

We are now at the beginning

Where it will take us is at the moment unknown.