NEPP Electronic Technology Workshop June 13-16, 2016

# A Good Idea That Didn't Pan Out – Single Event Test Results of Altera MAX10

#### **Greg Allen** NASA JPL, California Institute of Technology

#### Acknowledgment:

This work was sponsored by:

NASA Office of Safety & Mission Assurance,

NASA Electronics Parts and Packaging Program

# Altera MAX10 FPGA Task Overview

- Task Description—perform initial SEL and TID characterization of Altera's CPLD Based MAX10 FPGA.

- General Test strategies based on Field Programmable Gate Array (FPGA) Single Event Effect (SEE) Radiation Testing [Berg, 2012], and SoC SEE Test Guideline Development [Guertin].

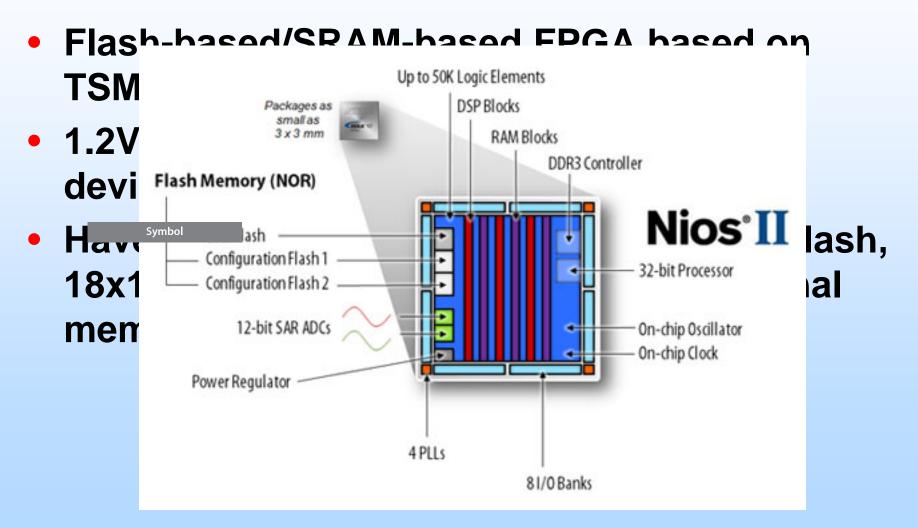

### **Altera MAX10 Architecture Overview**

# **FY16 Major Accomplishments-MAX10**

Performed SEL characterization test on MAX10 devices Jet Propulsion Laboratory California Institute of Technology

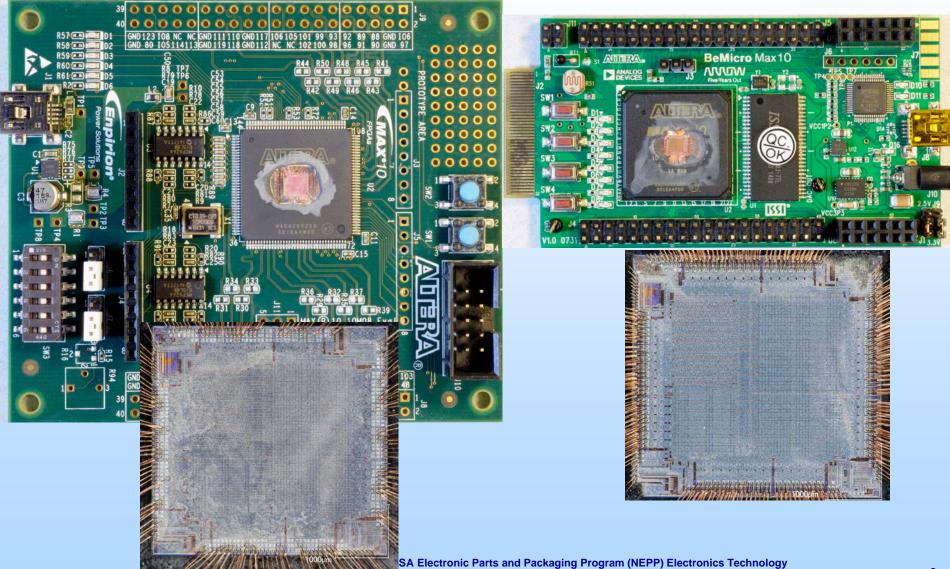

#### **Test Boards**

Workshop (ETW), NASA Goddard Space Flight Center in Greenbelt, MD, June 13-16, 2016 and published on nepp.nasa.gov.

## **TID Test Plan**

- Phase 1 Test (Completed)

- Initial test structures:

- Simple shift register with combinatorial logic

- Inverter chain

- Single Supply (VCC\_ONE)

- Biased, no-refresh mode

- Phase 2 Test (Cancelled due to SEL results)

- Full processor implementation, ADC, PLL, etc.

- Both FPGA types to be tested (single and dual supply).

- Initially biased only, using both program refresh mode and no-refresh mode.

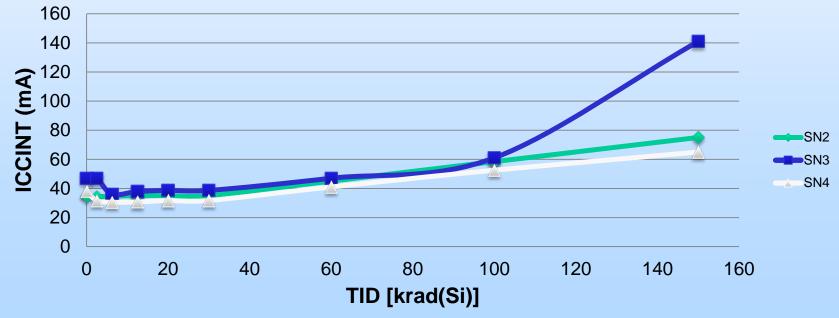

# Initial TID Results (FY15)

- Tested at Co-60 facility at JPL.

- Tested MAX10 VCC\_ONE device at 25 rad(Si)/second, biased, no-refresh.

- No timing degradation observed. Functional failure between 100 and 150 krad(Si).

#### ICC\_ONE vs. TID

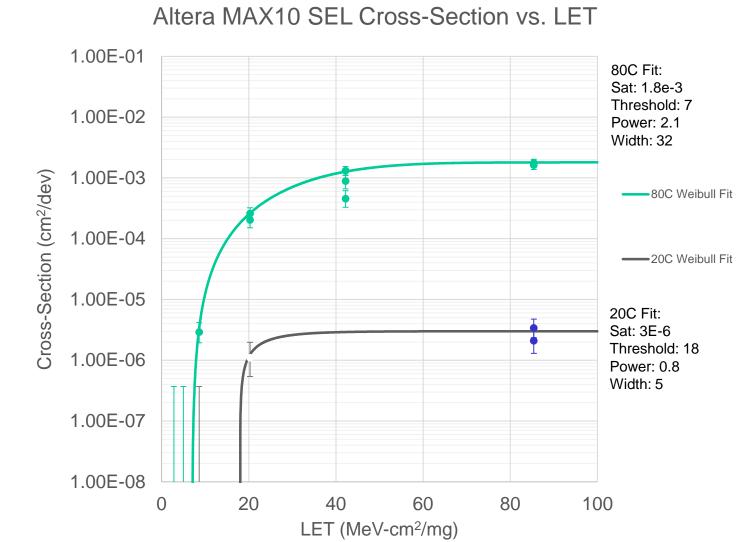

### **SEL Test Plan**

- Basic SEL test (6 devices, three of each supply type), worst-case datasheet bias and temperature, 1x10<sup>7</sup> ions/cm<sup>2</sup> per DUT or statistically significant events

- Simple functional design

- Regulators removed from evaluation board and power directly supplied

- Custom software used to monitor and strip chart power, and automatically power cycle in the event of an SEL

## **SEL Test Results**

#### **Jet Propulsion Laboratory**

California Institute of Technology

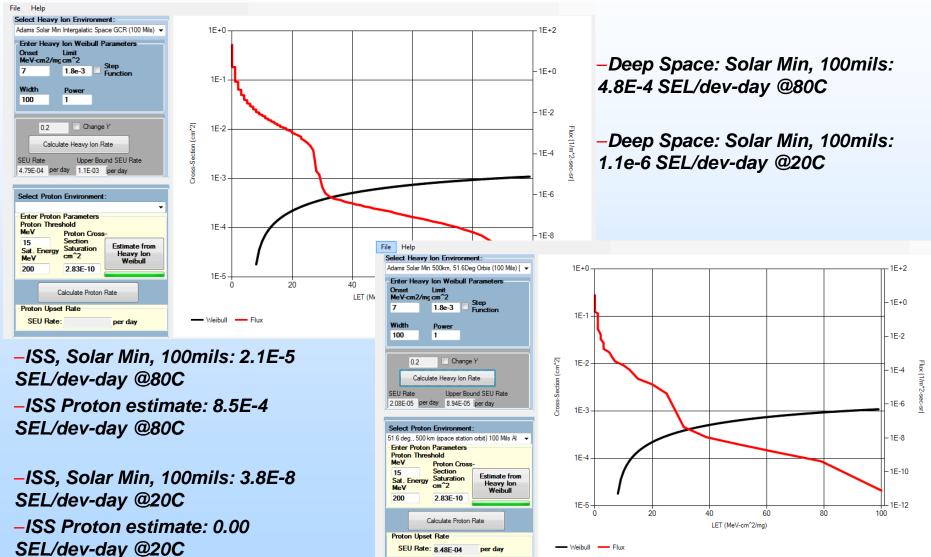

### **Representative SEL Rates**

# **Other SEL Test Notables**

- SEL only occurred while in a configured state

- e.g. if the DUT was held in an unconfigured state, the effect was not observed.

- Indicates ADC unpowered during un-configured state

- With Au, the configuration was knocked out instantly and required reprogramming.

- With Ag and below, both devices maintained configuration

- Opened power supply clamps and SEL maintained ~1.1A

#### Conclusions

- Lower budget missions (e.g. class D) will often select commercial devices

- Methodologies for determining baseline SEE/TID susceptibility can be scaled to mission budgets

- Altera MAX10 is susceptible to SEL and not recommended for use in space