### High Density Packaging Technologies Through Silicon Via (TSV)

- .

### by

### Reza Ghaffarian, Ph.D.

NASA-JPL-CalTech

(818) 354-2059

Reza.Ghaffarian@JPL.NASA.gov

Copyright 2020 California Institute of Technology Government sponsorship acknowledged

NEPP Electronics Technology Workshop (ETW 2020) June 15-18, 2020, NASA GSFC

## http://nepp.nasa.gov

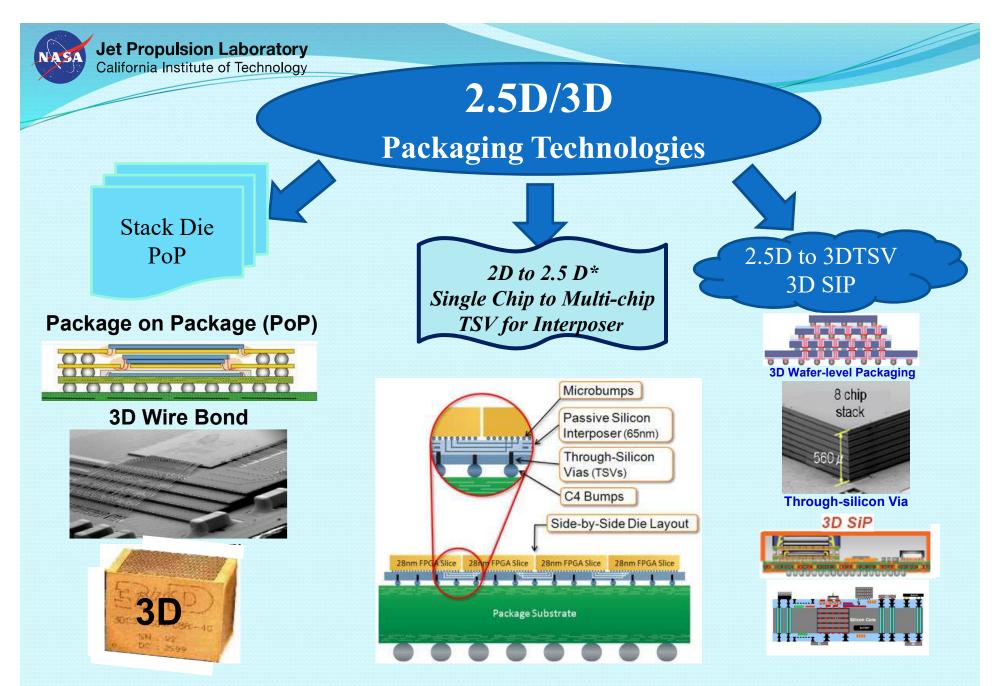

#### 2.5/3D Packaging Trends

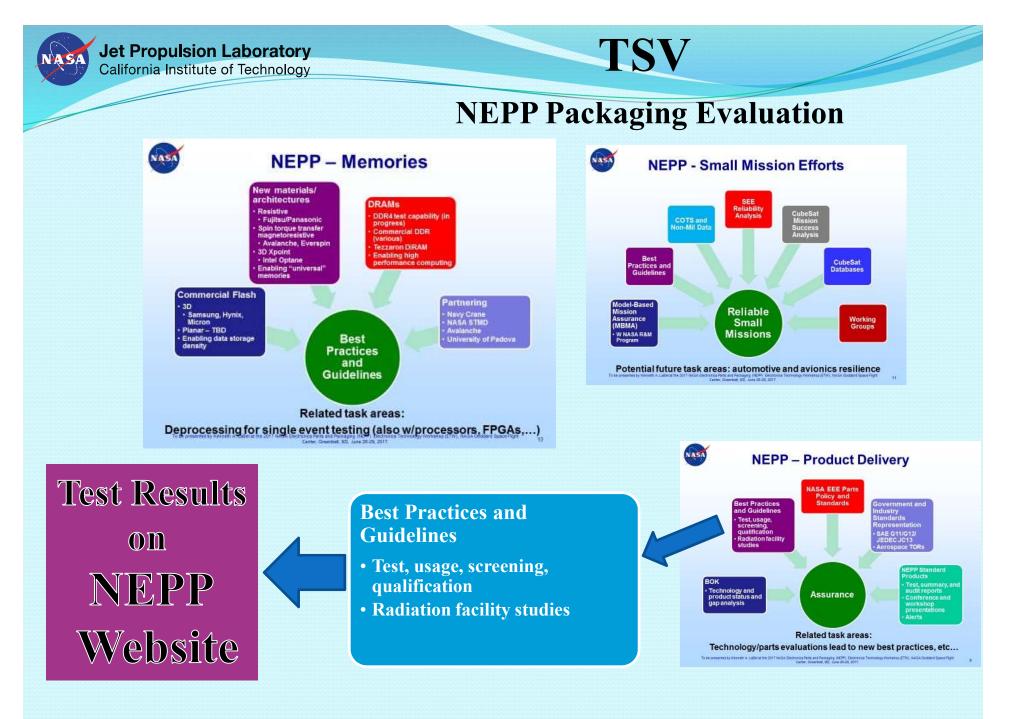

- NEPP Task Deliverable: TSV Evaluation

- Industry 2.5/3D Packaging Technologies

- NEPP on High-Density Packaging Technologies: Current and Previous

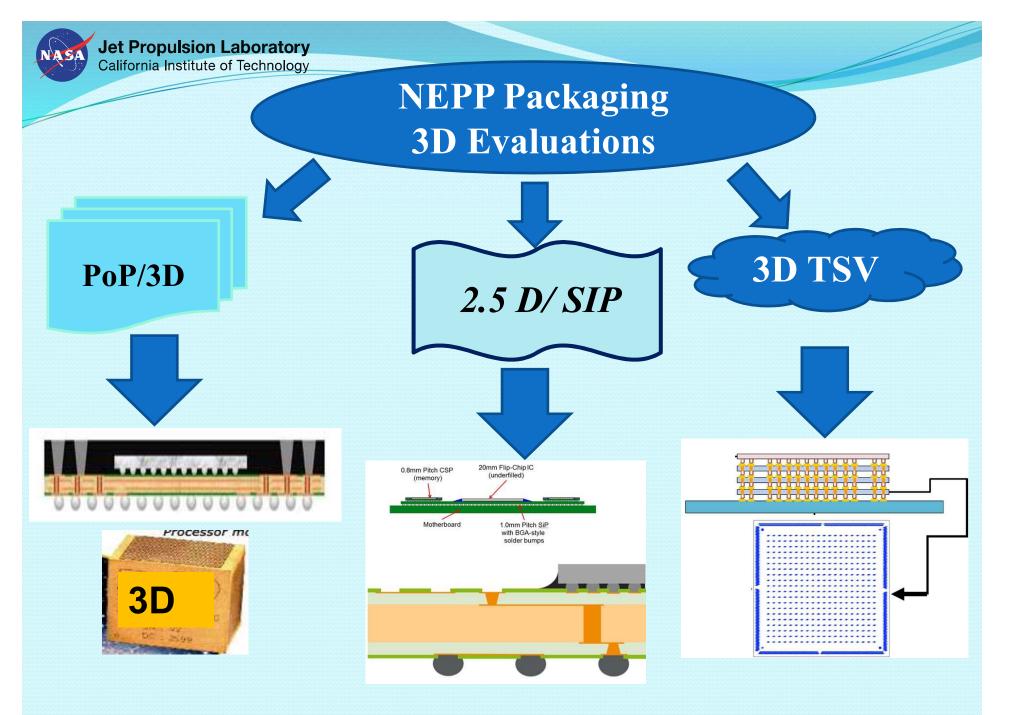

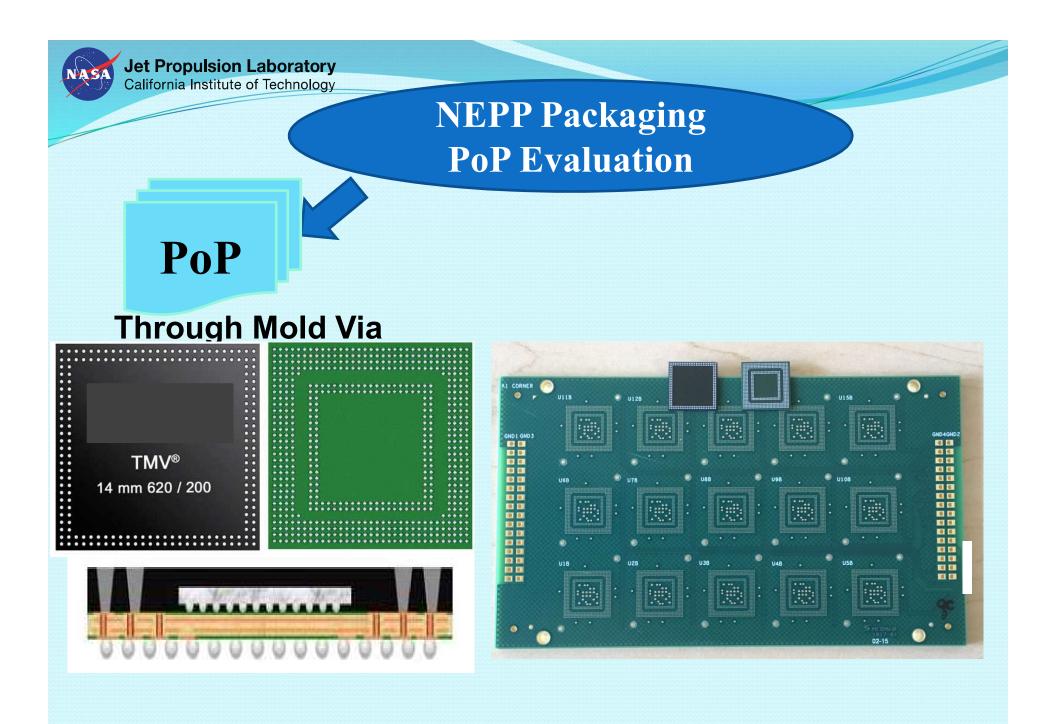

- PoP/3D

- SiP

- TSV-Through Silicon Via Daisy-Chain Evaluation

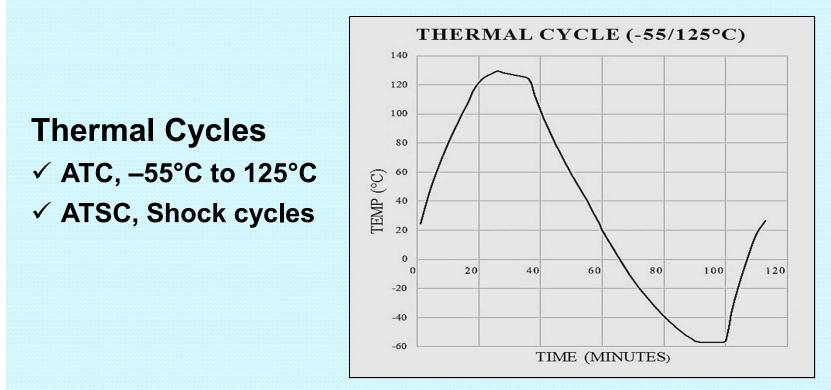

- PoP/3D Reliability under Thermal Cycling

- PoP: 4 assembly configurations

- PoP: Thermal cycle (-55/125°C)- Results & failures

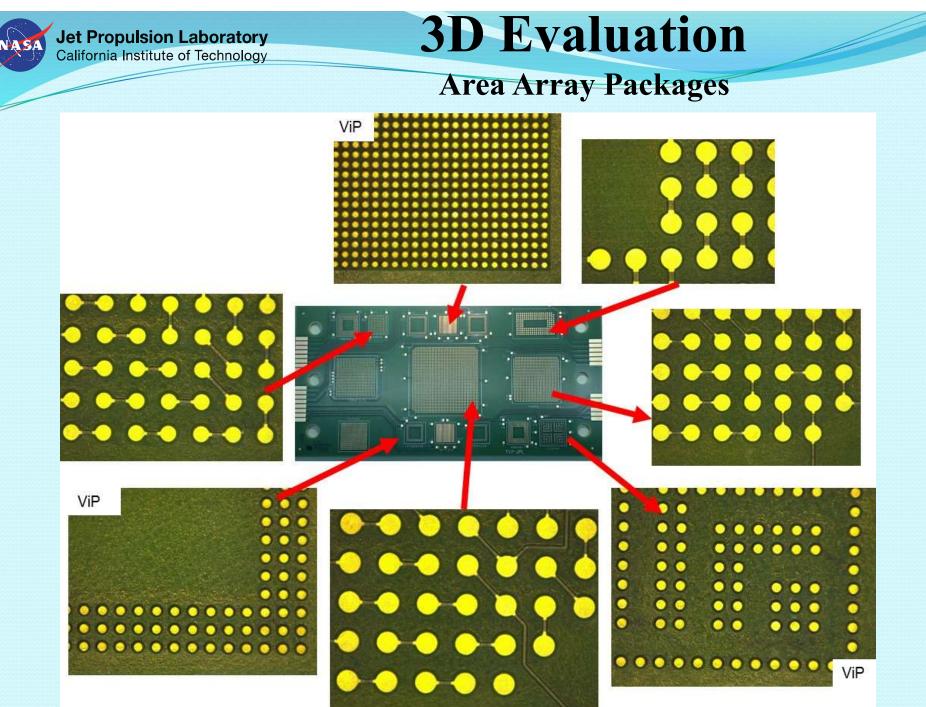

- 3D : Single and double-side under thermal cycles (-55/100°C)

- SiP Reliability under Thermal Cycling

- Flip chip and BGA on BGA Interposer

- Thermal cycle (-40/125°C) TC & failures

- Weibull plots and the effect of BGA underfill

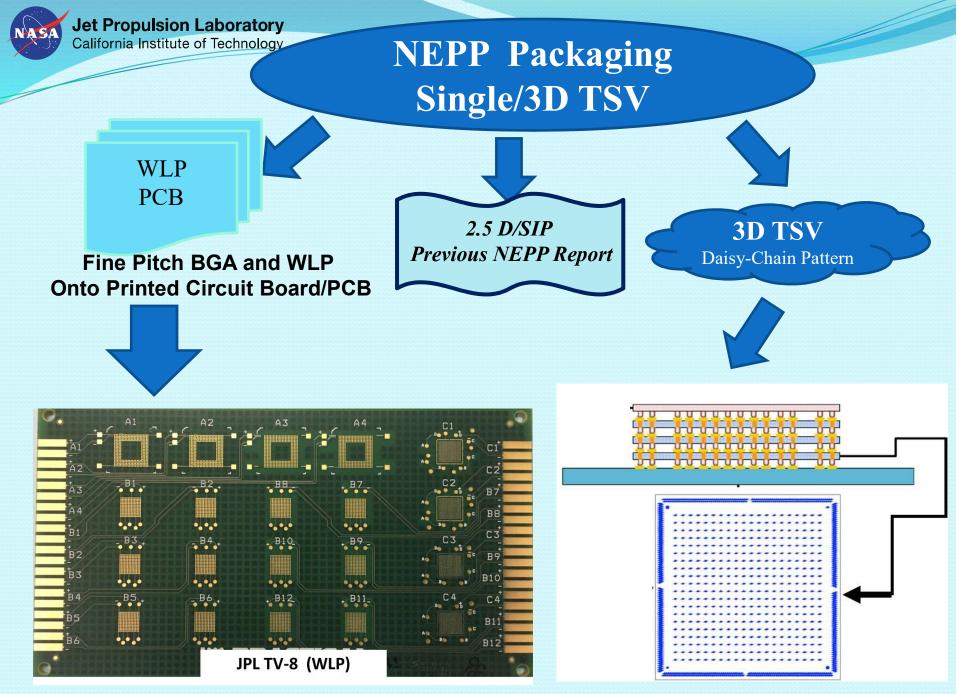

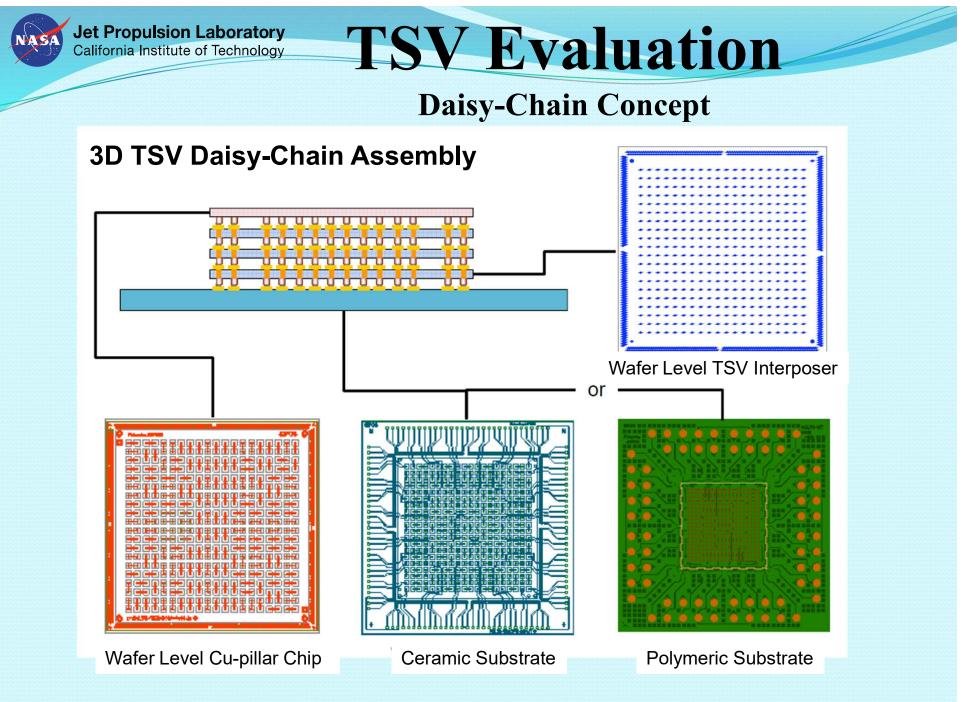

- TSV Daisy-Chain Evaluation

- TSV Daisy-chain concept

- 3TSV build with two interposers

- PCB Design for WLP & TSV

- Summary

**NEPP ETW- 2020**

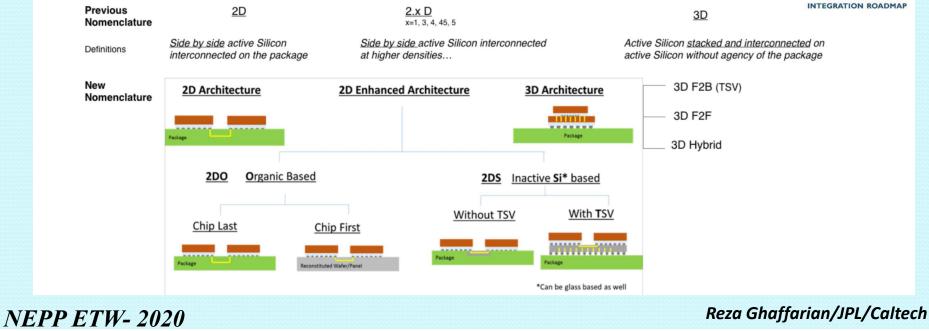

\* 2.5D now 2DS (on silicon substrates) and 2DO (on organic substrates) NEPP ETW- 2020 Reza Ghaffarian/JPL/Caltech

### Nomenclature Converges 2DO/2DS & 3D

# A 2D architecture is defined where two or more active silicon devices are placed side-by-side and are interconnected on the package

- ✓ 2DO (2D Organic) uses an organic medium

- ✓ 2DS uses an inorganic medium (e.g. a silicon/glass/ceramic interposer or bridge)

- ✓ A 3D architecture is defined where two or more active silicon devices are stacked and interconnected without the agency of the package

Converged Nomenclature Framework for 2D & 3D Architectures

#### Assemblies

- ✓ Top flux/Bottom SnPb paste onto PCB

- ✓ Top paste/Bottom SnPb paste onto PCB

- ✓ Top paste/Bottom SAC305 paste onto PCB

- ✓ Top paste reflowed. PoP onto SnPb paste onto PCB

**NEPP ETW- 2020**

#### Jet Propulsion Laboratory California Institute of Technology

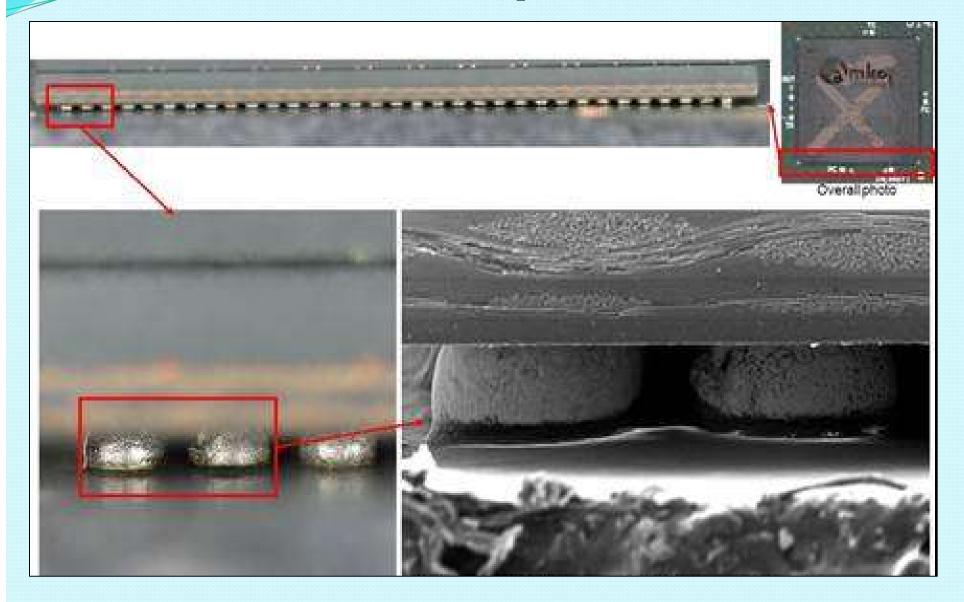

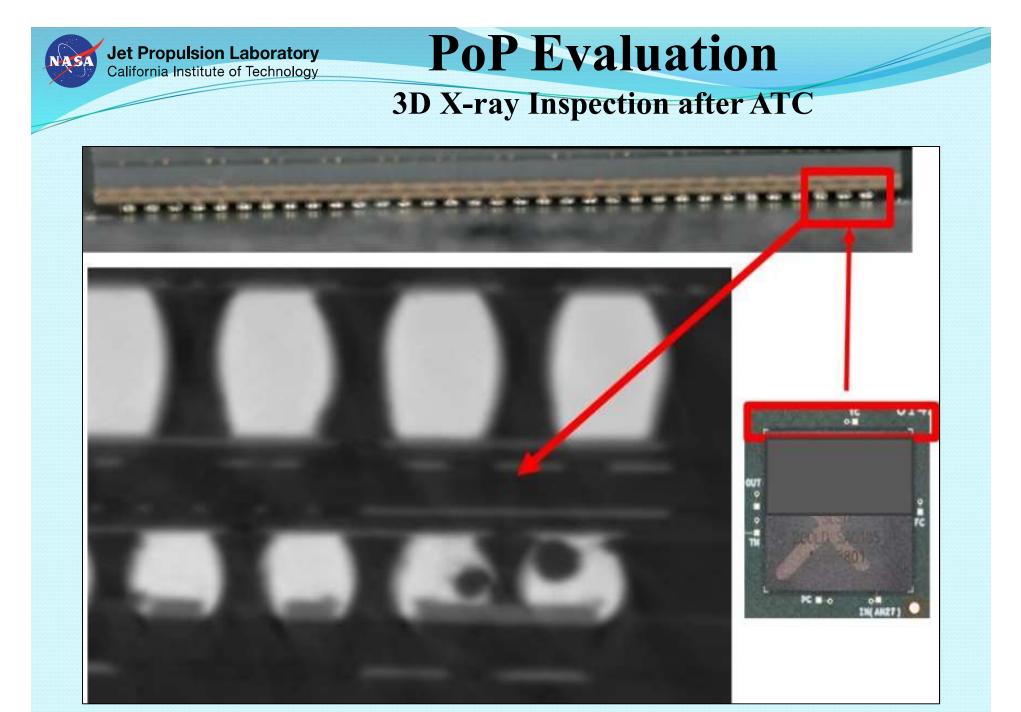

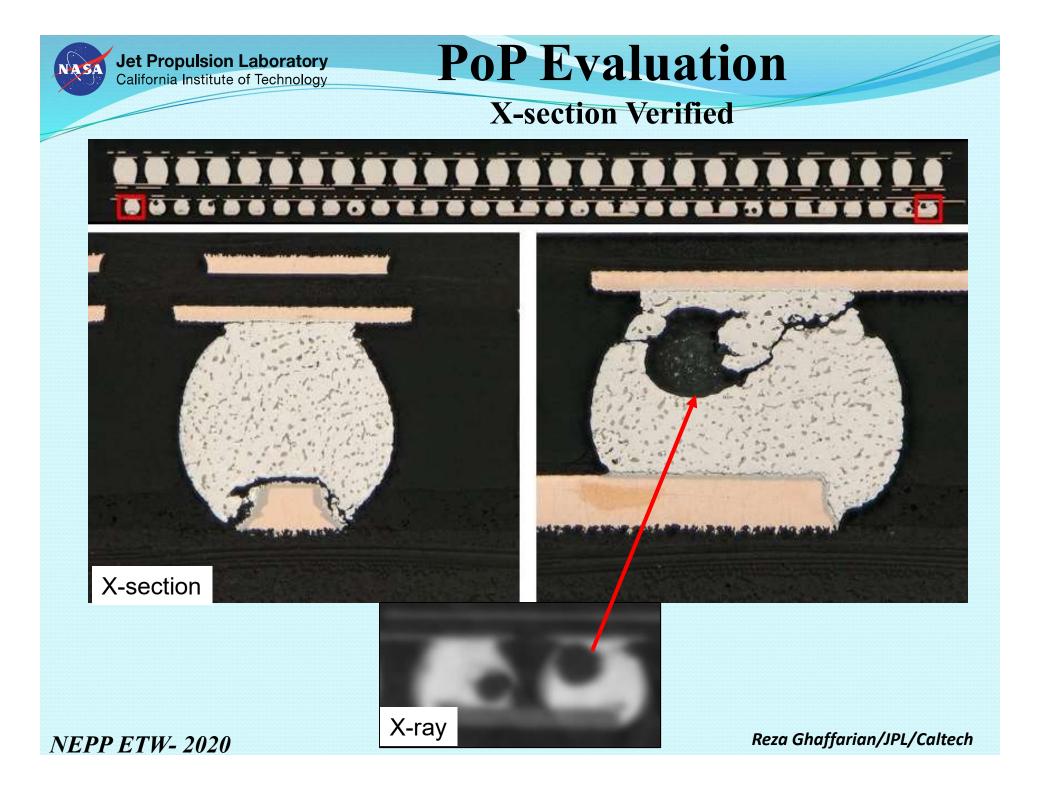

### **PoP Evaluation** SEM Inspection after ATC

**NEPP ETW- 2020**

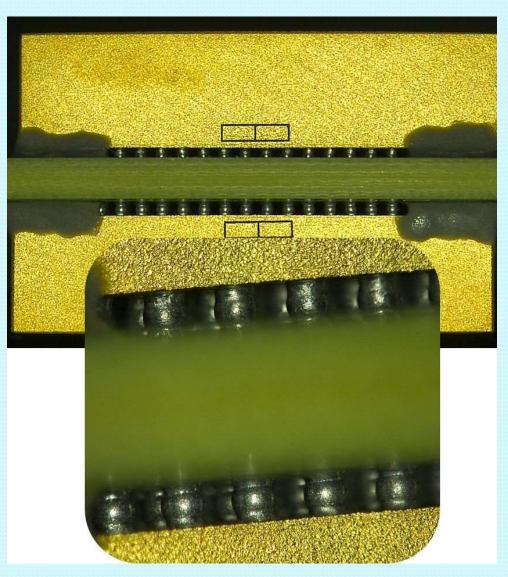

#### Single & Double-sided

**NEPP ETW- 2020**

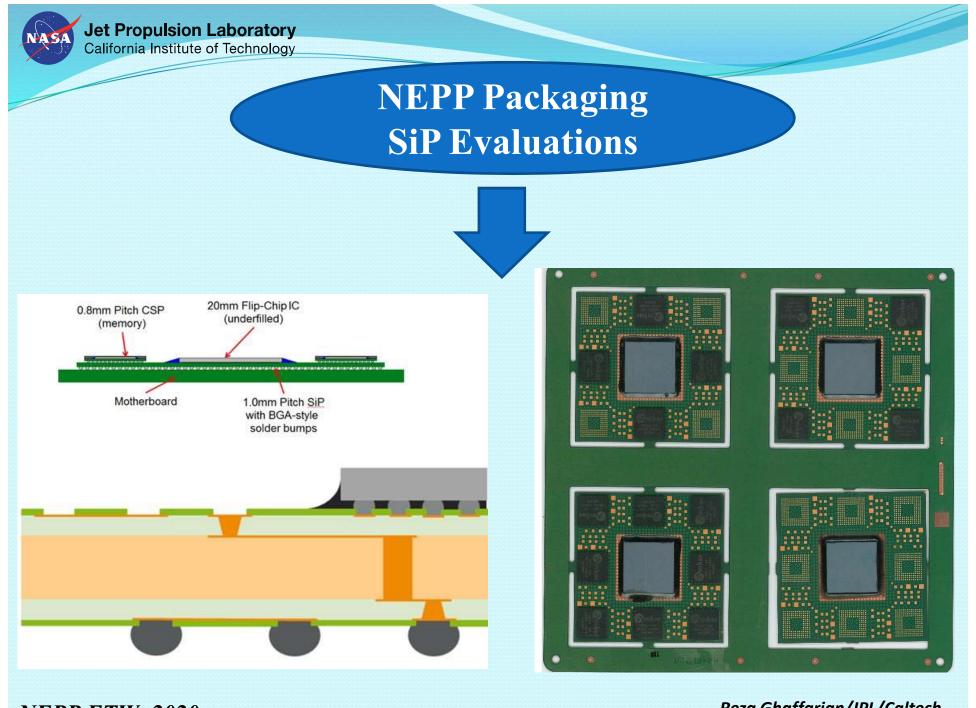

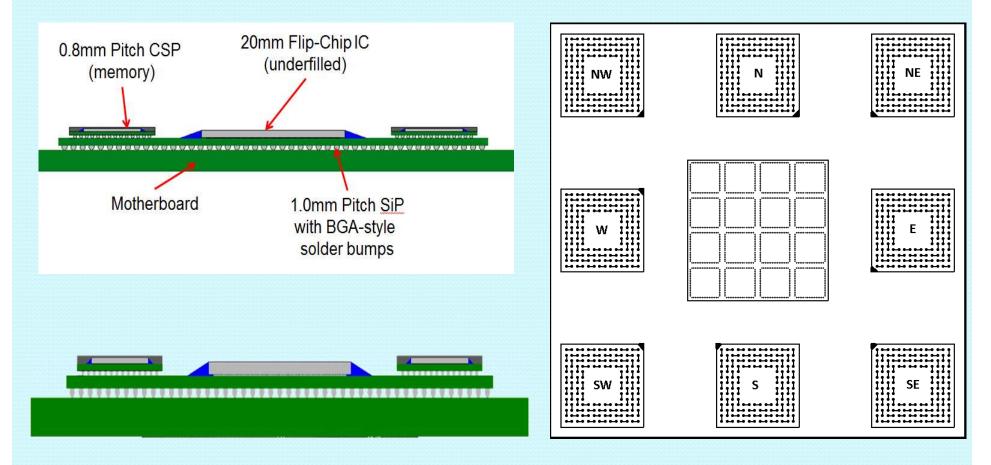

## **SiP TC Evaluation**

- 8 CABGA 160 I/O, 12x12 mm, 0.8 mm pitch

- 1 flip-chip at the center (20x20 mm)

Jet Propulsion Laboratory California Institute of Technology

• SAC305 & SnPb, 3364 balls, 60x60 mm, 1.0-mm pitch

**NEPP ETW- 2020**

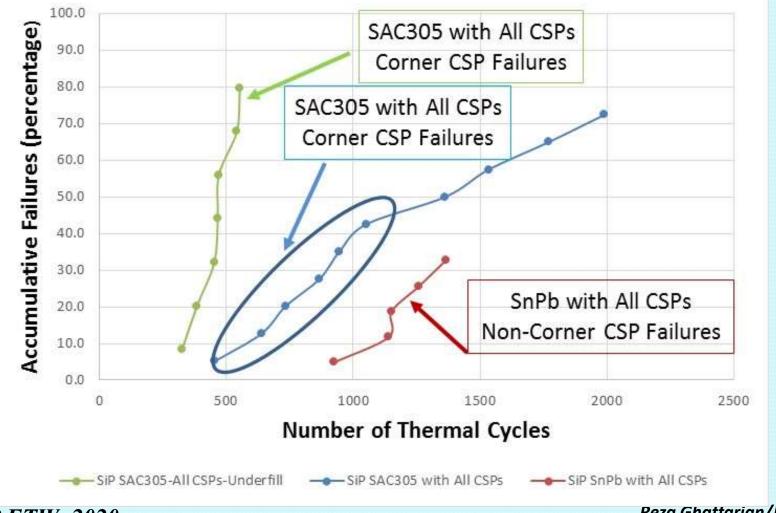

#### Weibull Plots

#### SiP Thermal Cycle Failures (-40/125°C)

**NEPP ETW- 2020**

#### Jet Propulsion Laboratory California Institute of Technology

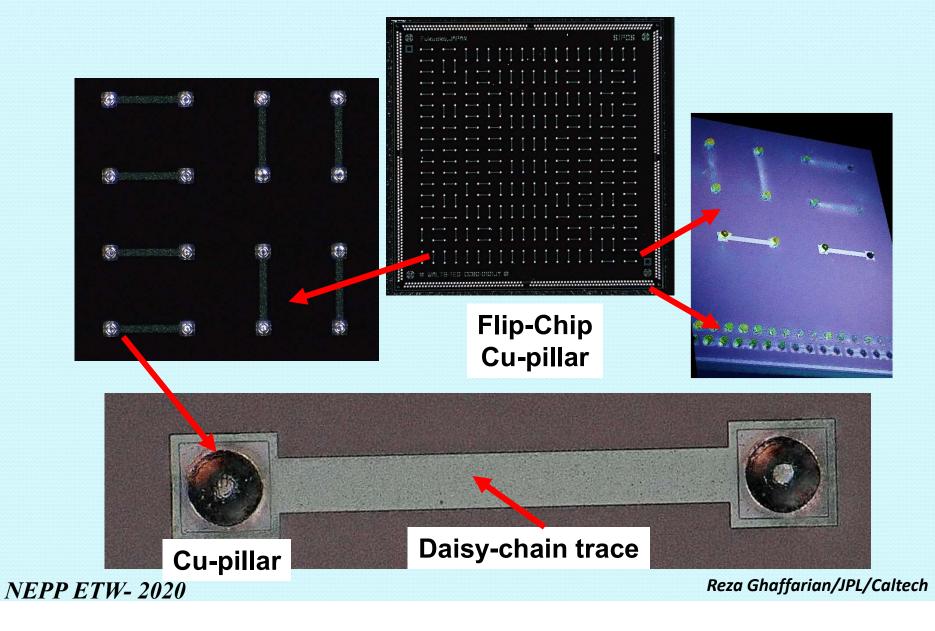

# **TSV Evaluation**

#### **Copper Pillar Daisy-Chain**

#### Jet Propulsion Laboratory California Institute of Technology

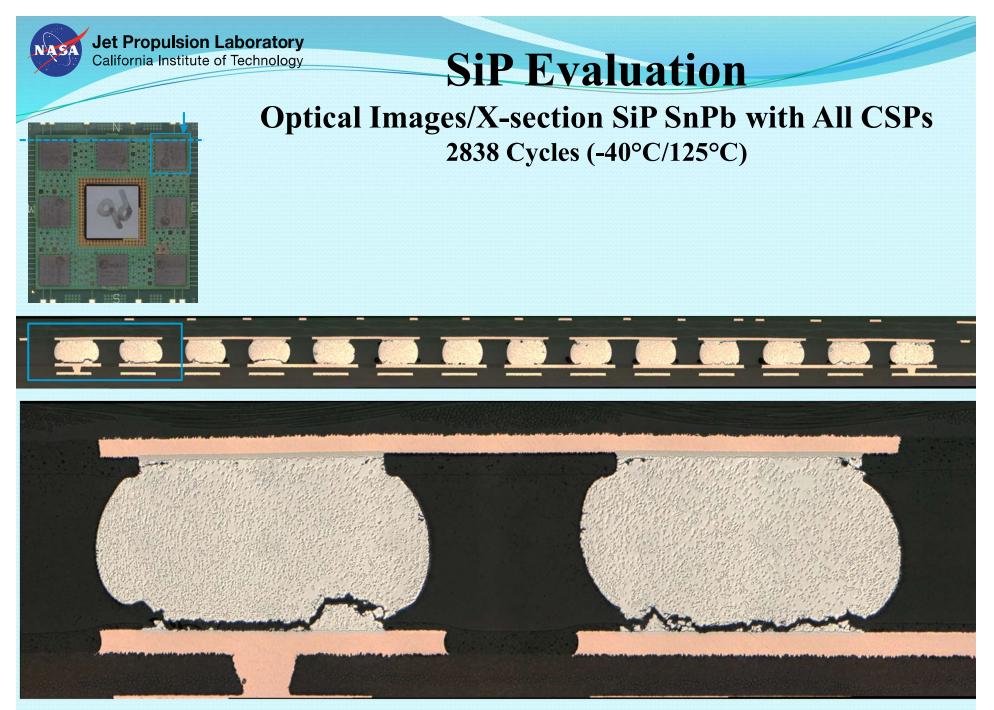

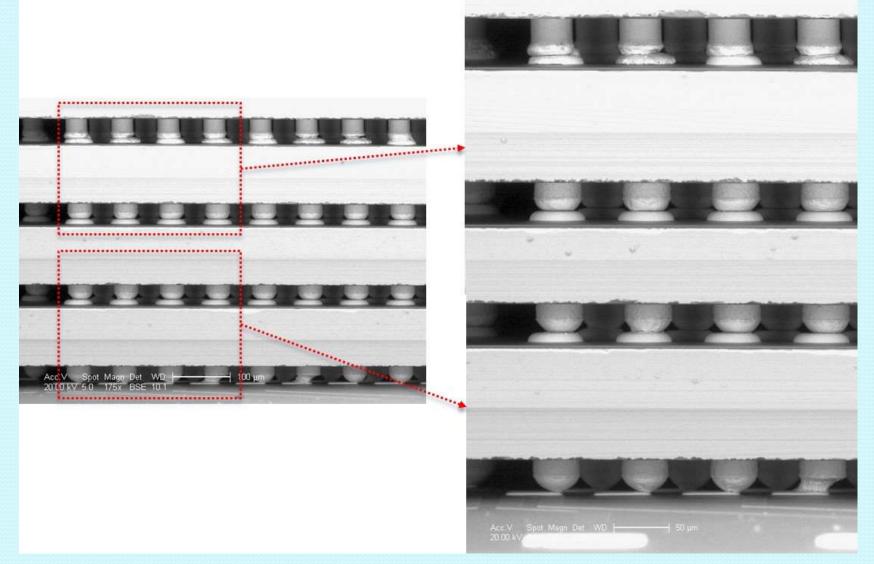

## **TSV Evaluation**

#### **3D Interposer Package Build Challenges**

**NEPP ETW- 2020**

## Summary

#### Reviewed NEPP Tasks on 2.5/3D Packaging

- PoP/3D

- SiP

- TSV-Through Silicon Via Daisy-Chain Evaluation

- Evaluate PoP/3D Reliability under Thermal Cycling

- No failure of 4 PoP assembly configurations

- 200 thermal cycle (-55/125°C)

- Bottom package failed first, failure from solder joint

- No failure of 3D : Single and double-sided assemblies

- 200 thermal cycles (-55/100°C)

- Internally: Potential for Head-on-Pillow (HoP) failure

- Daisy-chain drawback: No internal die

- SiP Reliability under Thermal Cycling

- Warpage challenge for assembly and new finding on underfill effects

- No failures to 200 thermal cycles (-40/125°C) of BGAs onto interposer or onto PCB

- Weibull plots narrowed to show the effect of interposer's BGA underfill

- TSV Daisy-Chain Evaluation

- Designed TSV daisy-chain for package build and assembly onto PCB

- Characterize TSV and showed challenges in build with two interposers

- Further evaluation both for package and PCB

#### • Next

• Optimization of TSV daisy-chain and reliability evaluation

NEPP ETW- 2020

#### The research described in this publication is being conducted at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. Copyright 2020 California Institute of Technology. U.S. Government sponsorship acknowledged.

The author would like to acknowledge the support of the JPL team and industry partners, especially the team from UIC. The author also extends his appreciation to the program managers of the National Aeronautics and Space Administration Electronics Parts and Packaging (NEPP) Program including Dr. P. Majewicz, J. Pellish, Dr. D. Sheldon, and Dr. J. Evans for their support and continuous

Acknowledgment

NEPP ETW- 2020

Reza Ghaffarian/JPL/Caltech