NASA NEPP Workshop - June 18, 2020

# Testing of Complex FPGAs, Memorys and Microprocessors

Jonathan Hochstetler (Host) / Sultan Lilani (Co-host)

Celebrating Over 35 Years of Providing High Quality Semiconductor Services

### Webinar Outline

- 1. What do AC, DC and Functional Testing Mean

- 2. Advanced Microprocessors / FPGA / Memory

- 1. AC/DC and Functional Testing

- 2. Device bus cycle timing implementation in ATE environment

- 3. Development of ATE based software

- 4. Compiled device assembly language loaded to the device

- 5. Testing independent of manufacturer proprietary test methods

- 6. Tools of testing

- 7. How to develop the test vectors and configuration vectors

- 8. DDR /DDR2 /DDR3 / DDR4 SDRAM, SSRAM QDR testing protocols

- 9. NAND Flash testing protocols

- 10. Data Retention and Endurance protocols

- 3. Temperature Testing

### Let Us Talk Basics

### What does AC / DC / Functional Testing Mean

## What is DC Testing?

Bond wires to the lead frame and then to the external device pins

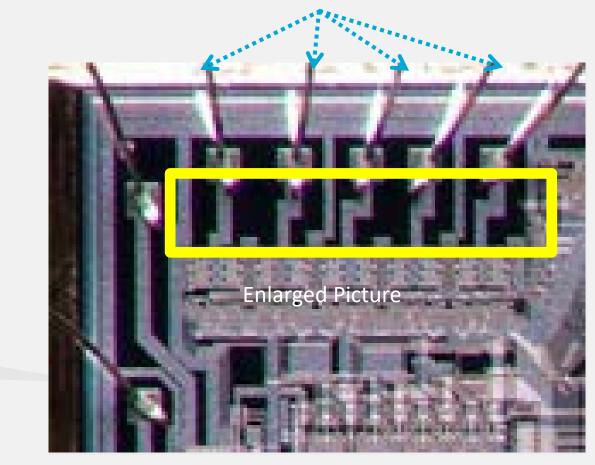

DC testing only covers the circuitry enclosed in the yellow square

- Essentially the first few transistors of each pin of the device.

## What is DC Testing?

The yellow portion is an estimate of the circuitry that might be tested by DC only testing

What can typical DC testing tell you?

- Electrical Over Stress (EOS) or Electro Static Discharge (ESD).

- If a pin is damaged, but not failing (indicated by higher than normal leakage current).

- IDD power supply current failures.

## What is AC Testing?

| Table 3             | 8: AC Electrical Charac<br>T <sub>A</sub> = -40°C to +85°C |            |                                              |                  | 3MHz,                                         | 4.5-5.5V@40                                                        | MHz, V <sub>SS</sub> =       | 0V    |  |  |

|---------------------|------------------------------------------------------------|------------|----------------------------------------------|------------------|-----------------------------------------------|--------------------------------------------------------------------|------------------------------|-------|--|--|

|                     |                                                            | Oscillator |                                              |                  |                                               |                                                                    |                              |       |  |  |

|                     |                                                            | Мс<br>16 М | Hz (x1<br>ode)<br>Hz (x2<br>de) <sup>1</sup> | Ма<br>20 М<br>Мо | Hz (x1<br>ode)<br>Hz (x2<br>ode) <sup>1</sup> | Variable                                                           |                              |       |  |  |

| Symbol              | Parameter                                                  | Min        | Max                                          | Min              | Max                                           | Min                                                                | Max                          | Units |  |  |

| 1/T <sub>CLCL</sub> | x1 Mode Oscillator Fre-<br>quency                          | 0          | 33                                           | 0                | 40                                            | 0                                                                  | 40                           | MHz   |  |  |

| 1/2Talal            | x2 Mode Oscillator Fre-<br>quency                          | 0          | 16                                           | 0                | 20                                            | 0                                                                  | 20                           | MHz   |  |  |

| TLHLL               | ALE Pulse Width                                            | 46         |                                              | 35               |                                               | 2T <sub>CLCL</sub> - 15                                            |                              | ns    |  |  |

| TAVLL               | Address Valid to ALE Low                                   | 5          |                                              |                  |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |  |  |

|                     |                                                            |            |                                              | 10               |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |  |  |

| TLLAX               | Address Hold After ALE<br>Low                              | 5          |                                              |                  |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |  |  |

|                     |                                                            |            |                                              | 10               |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |  |  |

| TLLIV               | ALE Low to Valid Instr In                                  |            | 56                                           |                  |                                               |                                                                    | 4T <sub>CLCL</sub> - 65 (3V) | ns    |  |  |

|                     |                                                            |            |                                              |                  | 55                                            |                                                                    | 4T <sub>CLCL</sub> - 45 (5V) | ns    |  |  |

| TLLPL               | ALE Low to PSEN# Low                                       | 5          |                                              |                  |                                               | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |  |  |

|                     |                                                            |            |                                              | 10               |                                               | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |  |  |

| Трцрн               | PSEN# Pulse Width                                          | 66         |                                              | 60               |                                               | 3T <sub>CLCL</sub> - 25<br>(3V)<br>3T <sub>CLCL</sub> - 15<br>(5V) |                              | ns    |  |  |

| TPLIV               | PSEN# Low to Valid Instr<br>In                             |            | 35                                           |                  |                                               |                                                                    | 3T <sub>CLCL</sub> - 55 (3V) | ns    |  |  |

|                     |                                                            |            |                                              |                  | 25                                            |                                                                    | 3T <sub>CLCL</sub> - 50 (5V) | ns    |  |  |

| TPXIX               | Input Instr Hold After<br>PSEN#                            |            |                                              |                  |                                               | 0                                                                  |                              | ns    |  |  |

| T <sub>PXIZ</sub>   | Input Instr Float After<br>PSEN#                           |            | 25                                           |                  |                                               |                                                                    | T <sub>CLCL</sub> - 5 (3V)   | ns    |  |  |

|                     |                                                            |            |                                              |                  | 10                                            |                                                                    | T <sub>CLCL</sub> - 15 (5V)  | ns    |  |  |

| TPXAV               | PSEN# to Address valid                                     | 22         |                                              | 17               |                                               | TCLCL - 8                                                          |                              | ns    |  |  |

| TAVIV               | Address to Valid Instr In                                  |            | 72                                           |                  |                                               |                                                                    | 5T <sub>CLCL</sub> - 80 (3V) | ns    |  |  |

|                     |                                                            |            |                                              |                  | 65                                            |                                                                    | 5TCLCL - 60 (5V)             | ns    |  |  |

| TPLAZ               | PSEN# Low to Address<br>Float                              |            | 10                                           |                  | 10                                            |                                                                    | 10                           | ns    |  |  |

| T <sub>RLRH</sub>   | RD# Pulse Width                                            | 142        |                                              | 120              |                                               | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |  |  |

| TWLWH               | Write Pulse Width (WE#)                                    | 142        |                                              | 120              |                                               | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |  |  |

| TRLDV               | RD# Low to Valid Data In                                   |            | 62                                           |                  |                                               |                                                                    | 5T <sub>CLCL</sub> - 90 (3V) | ns    |  |  |

### Example AC Parametric Table From Data Sheet:

0.00 0.00

|        |                                                | 33 MHz (x1<br>Mode)<br>16 MHz (x2<br>Mode) <sup>1</sup> |     | 40 MHz (x1<br>Mode)<br>20 MHz (x2<br>Mode) <sup>1</sup> |     | Vari                                                         | Ť                                                            |       |

|--------|------------------------------------------------|---------------------------------------------------------|-----|---------------------------------------------------------|-----|--------------------------------------------------------------|--------------------------------------------------------------|-------|

| Symbol | Parameter                                      | Min                                                     | Max | Min                                                     | Max | Min                                                          | Max                                                          | Units |

|        |                                                |                                                         |     |                                                         | 75  |                                                              | 5T <sub>CLCL</sub> - 50 (5V)                                 | ns    |

| TRHDX  | Data Hold After RD#                            | 0                                                       |     | 0                                                       |     | 0                                                            |                                                              | ns    |

| TRHDZ  | Data Float After RD#                           |                                                         | 36  |                                                         |     |                                                              | 2Talal - 25 (3V)                                             | ns    |

|        |                                                |                                                         |     |                                                         | 38  |                                                              | 2Talal - 12 (5V)                                             | ns    |

| TLLDV  | ALE Low to Valid Data In                       |                                                         | 152 |                                                         |     |                                                              | 8T <sub>CLCL</sub> - 90 (3V)                                 | ns    |

|        | Ì                                              |                                                         |     |                                                         | 150 |                                                              | 8Toucu - 50 (5V)                                             | ns    |

| TAVDV  | Address to Valid Data In                       |                                                         | 183 |                                                         |     |                                                              | 9T <sub>CLCL</sub> - 90 (3V)                                 | ns    |

|        |                                                |                                                         |     |                                                         | 150 |                                                              | 9Talal - 75 (5V)                                             | ns    |

| TLUWL  | ALE Low to RD# or WR#<br>Low                   | 66                                                      | 116 | 60                                                      | 90  | 3T <sub>OLOL</sub> - 25 (3V)<br>3T <sub>OLOL</sub> - 15 (5V) | 3T <sub>CLCL</sub> + 25 (3V)<br>3T <sub>CLCL</sub> + 15 (5V) | ns    |

| TAVWL  | Address to RD# or WR#<br>Low                   | 46                                                      |     |                                                         |     | 4T <sub>OLOL</sub> - 75 (3V)                                 |                                                              | ns    |

|        |                                                |                                                         |     | 70                                                      |     | 4T <sub>CLCL</sub> - 30 (5V)                                 |                                                              | ns    |

| TWHOX  | Data Hold After WR#                            | 3                                                       |     |                                                         |     | T <sub>CLCL</sub> - 27 (3V)                                  |                                                              | ns    |

|        | 1                                              |                                                         |     | 5                                                       |     | T <sub>CLCL</sub> - 20 (5V)                                  |                                                              | ns    |

| TQVWH  | Data Valid to WR# High                         | 142                                                     |     |                                                         |     | 7T <sub>CLCL</sub> - 70 (3V)                                 |                                                              | ns    |

|        |                                                |                                                         |     | 125                                                     |     | 7T <sub>CLCL</sub> - 50 (5V)                                 |                                                              | ns    |

| TQVWX  | Data Valid to WR# High to<br>Low<br>Transition | 10                                                      |     | 5                                                       |     | T <sub>CLCL</sub> - 20                                       |                                                              | ns    |

| TRLAZ  | RD# Low to Address Float                       |                                                         | 0   |                                                         | 0   |                                                              | 0                                                            | ns    |

| TWHLH  | RD# to WR# High to ALE<br>High                 | 5                                                       | 55  |                                                         |     | T <sub>CLCL</sub> - 25 (3V)                                  | T <sub>CLCL</sub> + 25 (3V)                                  | ns    |

|        | 1 1                                            |                                                         |     | 10                                                      | 40  | ToloL - 15 (5V)                                              | Toucu + 15 (5V)                                              | ns    |

1. Calculated values are for x1 Mode only Source: Microchip FlashFlex MCU Datasheet, 02/13

6

## What is AC Testing?

Propagation Delay Example

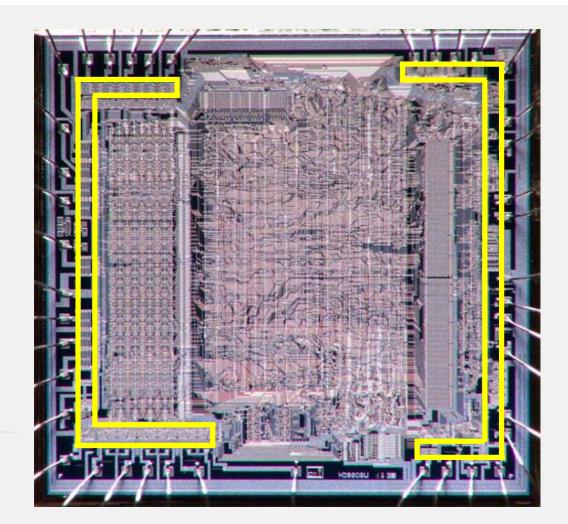

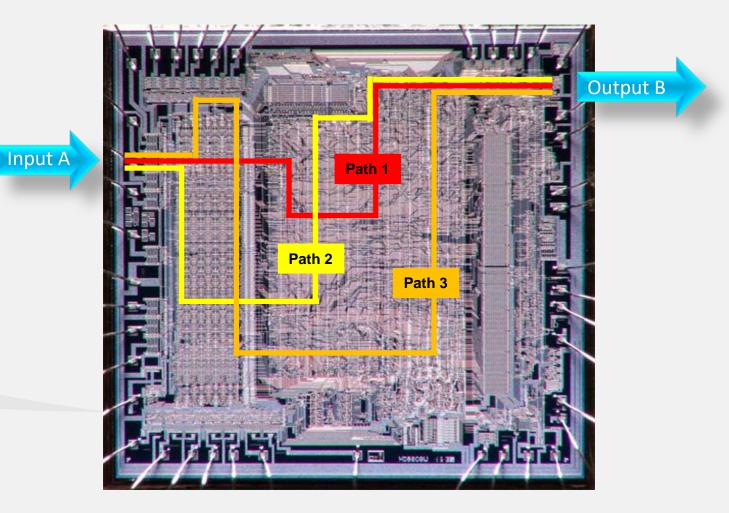

There may be several 100's or 1000's of paths through a device that are represented by a single AC parameter. Each path needs to be evaluated to determine if they all work.

In this case there are 3 paths from Input A to Output B. Path 3 is clearly the longest and is likely the worst case propagation delay path for this AC parameter.

## What is AC Testing?

AC testing will tell you the speed at which things happen in the device like:

• How long does it take to access an address (access time).

3

- How long does it take for one signal occur after another (prop. delay).

- Maximum operating frequency.

- Signal rise and fall times.

But AC testing by itself, while better than just DC testing, still only tests a small percentage of the die at any one time.

## What is Functional Testing?

Functional testing is making sure that all of the functions that a device can perform are exercised.

Ironically it is usually the area of the device that is the least explained in the datasheet.

The development of the functional test area of a complex parts accounts for 50% to 90% of the overall test development effort and cost

## What is Functional Testing?

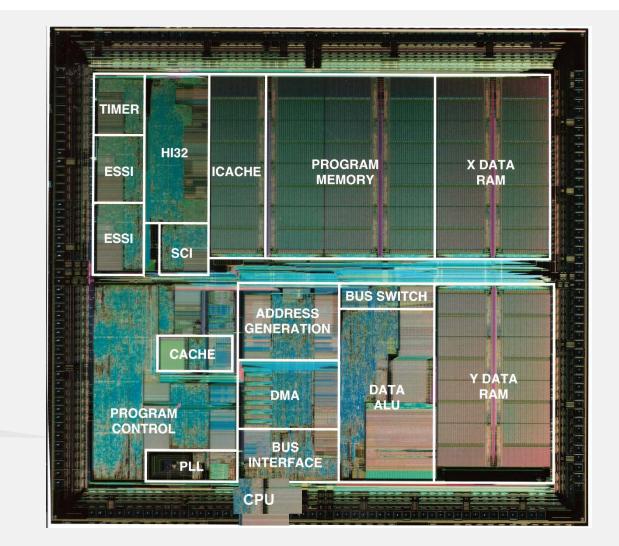

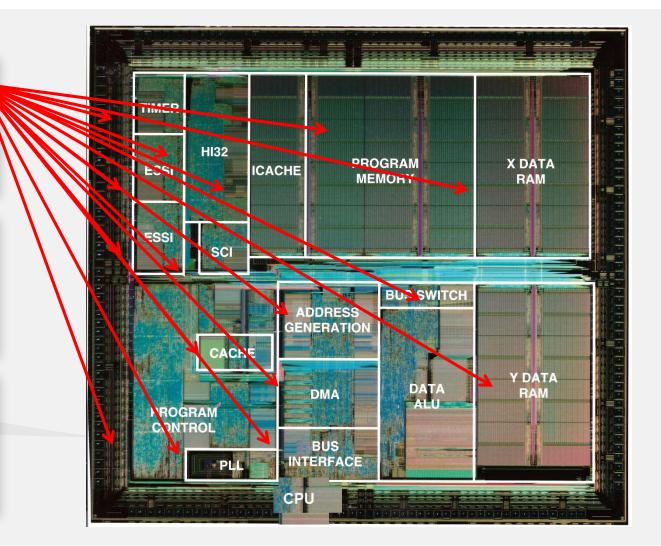

Functional testing requires that each functional block in a device be thoroughly tested.

This is where up to 90% of the test development effort lies when doing a complex part.

Each white named area is a functional block for this device.

2

## What is Functional Testing?

For a full coverage test plan; we need each of the 16 functional blocks in this device.

This can make functional testing very time consuming and very expensive.

What can happen if all functional blocks are not tested? Test escape!

3

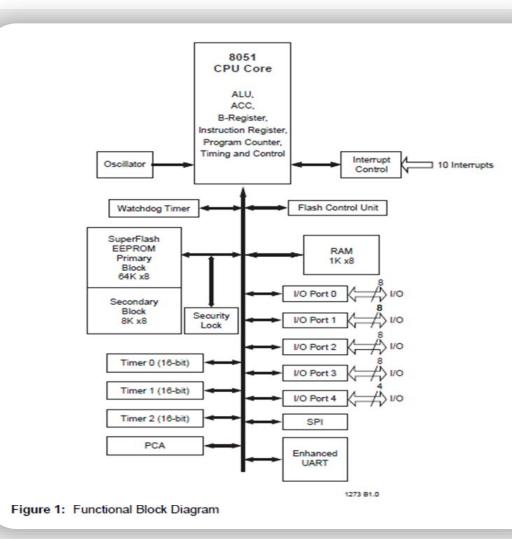

### **Cost to Develop A Relatively Simple 8051 8-bit Microcontroller**

Example Block Diagram and pin-out for a legacy 8051 device.

| (T2) P1.0          | ]1            | 40 | VDD        |

|--------------------|---------------|----|------------|

| (T2 EX) P1.1       | 2             | 39 | P0.0 (AD0) |

| (ECI) P1.2         | 3             | 38 | P0.1 (AD1) |

| (CEX0) P1.3        | 4             | 37 | P0.2 (AD2) |

| (CEX1 / SS#) P1.4  | 5             | 36 | P0.3 (AD3) |

| (CEX2 / MOSI) P1.5 | 6             | 35 | P0.4 (AD4) |

| (CEX3 / MISO) P1.6 | 7 40-pin PDIP | 34 | P0.5 (AD5) |

| (CEX4 / SCK) P1.7  | 8 Top View    | 33 | P0.6 (AD6) |

| RST                | 9             | 32 | P0.7 (AD7) |

| (RXD) P3.0         | 10            | 31 | EA#        |

| (TXD) P3.1         | 11            | 30 | ALE/PROG#  |

| (INT0#) P3.2       | 12            | 29 | PSEN#      |

| (INT1#) P3.3       | 13            | 28 | P2.7 (A15) |

| (T0) P3.4          | 14            | 27 | P2.6 (A14) |

| (T1) P3.5          | 15            | 26 | P2.5 (A13) |

| (WR#) P3.6         | 16            | 25 | P2.4 (A12) |

| (RD#) P3.7         | 17            | 24 | P2.3 (A11) |

| XTAL2              | 18            | 23 | P2.2 (A10) |

| XTAL1              | 19            | 22 | P2.1 (A9)  |

| VSS                | 20            | 21 | P2.0 (A8)  |

|                    |               |    |            |

### **Test Development Cost Example?**

Comprehensive Test Program Development Quotation Example

This is how your test lab should be quoting your project.

| Test Development Cost Example        |             |        |            |  |  |  |  |  |  |

|--------------------------------------|-------------|--------|------------|--|--|--|--|--|--|

|                                      | Engineering | Tester |            |  |  |  |  |  |  |

| Test Development Activities          | Hours       | Hours  | Cost*      |  |  |  |  |  |  |

| Test Specifcation Development        | 20          | 0      | \$ 3,000   |  |  |  |  |  |  |

| Test System Selection/Speed          | 3           | 0      | \$ 450     |  |  |  |  |  |  |

| Load Board Design & Fabrication      | 20          | 5      | \$ 3,750   |  |  |  |  |  |  |

| DC Tests                             | 25          | 20     | \$ 6,750   |  |  |  |  |  |  |

| Functional Test - MIN/Max Voltages   | 10          | 5      | \$ 2,250   |  |  |  |  |  |  |

| Functional Test - Timing Sets        | 15          | 10     | \$ 3,750   |  |  |  |  |  |  |

| Functional Test - CPU Core           | 120         | 80     | \$ 30,000  |  |  |  |  |  |  |

| Functional Test - Interupt Control   | 30          | 20     | \$ 7,500   |  |  |  |  |  |  |

| Functional Test - Watchdog Timer     | 20          | 15     | \$ 5,250   |  |  |  |  |  |  |

| Functional Test - Flash Control Unit | 10          | 7      | \$ 2,550   |  |  |  |  |  |  |

| Functional Test - SuperFlash         | 10          | 7      | \$ 2,550   |  |  |  |  |  |  |

| Functional Test - Ram                | 10          | 7      | \$ 2,550   |  |  |  |  |  |  |

| Functional Test - Security Lock      | 15          | 10     | \$ 3,750   |  |  |  |  |  |  |

| Functional Test - I/O Ports          | 25          | 17     | \$ 6,300   |  |  |  |  |  |  |

| Functional Test - Timers             | 25          | 20     | \$ 6,750   |  |  |  |  |  |  |

| Functional Test - SPI Bus            | 15          | 10     | \$ 3,750   |  |  |  |  |  |  |

| Functional Test - UART               | 40          | 30     | \$ 10,500  |  |  |  |  |  |  |

| AC Tests                             | 60          | 40     | \$ 15,000  |  |  |  |  |  |  |

| Total                                | 473         | 303    | \$ 116,400 |  |  |  |  |  |  |

\* Assumes \$150/hr for Engineering time and tester time

\* Figures for discussion purposes only - not an actual quotation.

### How Can Test Development Costs be Saved?

**ST**

#### Saving Test Development Costs

Since the manufacturer has already thoroughly tested the devices as a part of their original manufacturing flow, the developer is able to limit the counterfeit device testing to match only the actual application conditions.

- ✓ Use actual application speeds.

- ✓ Use actual application programing code (uP and memory).

- ✓ Use actual application designs (FPGA).

- ✓ Test only functional blocks actually used in the application.

- $\checkmark$  Test only the AC parameters that are critical to the application.

- ✓ Leverage test programs already developed for the same or similar parts.

- ✓ Use device emulators.

- ✓ Use golden devices to "learn" device functionality.

### **Testing of Complex Microprocessors, Memories and FPGA**

## **Integra's Microprocessor Testing Experience**

#### Test Engineering Experience

- Integra has developed more than 100 test programs for Processors

- Independent generation techniques without manufacturer support

- 4 engineers with processor development experience

#### Device Experience

- Intel Family 186,286, 386, 486, Pentium

- Free scale/Motorola Family 68000 to 68040, Power PC and P2020

- Other Manufacturers such as PMC RM7965, TI TMS320C Family

#### Examples of Programs Include:

- P2020NXE2HHC

- MPC603RRX266TC

- A8050266-133SY022

- RM7965-835T

- TMS320C6713BGDPA200

- ADSP2181BSZ133QM5326

### **Test Development of Free scale P2020 Microprocessor**

|   |                        | Test Coverage   | Notes                                                                                                                          |

|---|------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|

|   |                        | Continuity      | Verify device connectivity                                                                                                     |

| • | Comprehensive Test     | POR             | Power On Reset and initialize through the eSPI bus                                                                             |

|   | comprehensive rest     |                 | 1st CPU instruction cycle using eLB and instruction formatting. Part configured for 133Mhz Sysclk, 4:1 ratio for 533 CCB       |

|   |                        | 1st Instruction | clock and then 1.5:1 ratio for 800MHz eCORE clock.                                                                             |

|   | Coverage – All Integra | Dual CPU        | Sample math and move instructions for both CPUs using local bus                                                                |

|   | Coverage – An integra  |                 | The Local Bus will be used for all register read & writes so it will be tested during all blocks. Will test all DC parameters, |

|   |                        | eLB             | CLOCK to out, CLOCK to data valid, CLOCK to address valid and CLOCK to LALE assertion                                          |

|   | Concentral Dattering   |                 | Set all registers to send and receive data on both UARTs using transceiver holding register and receiver buffer register. All  |

|   | Generated Patterns     | UART            | DC and max baud rate for AC.                                                                                                   |

|   |                        | eSPI            | Set all registers to send and receive data using FIFO for all chip selects. All DC and Master Data out delay for AC            |

|   |                        | 12C             | Set registers for basic data transfer. All DC except pulse spike. Max clock frequency for AC                                   |

| • | 3 Engineers 1400       |                 | Enable DDR interface configured for DDR3. AC parametric testing (6) parameters listed below. No DC parametric. Will            |

|   |                        |                 | do some data transfers at 800Mhz.                                                                                              |

|   |                        |                 | 2.7.2.2 DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications                                                          |

|   | Engineering Hours -    |                 | MCK[n] cycle time tMCK (min)2.5 ns (max)5 ns                                                                                   |

|   | Lingineering riours    |                 |                                                                                                                                |

|   |                        |                 | ADDR/CMD output setup with respect to MCK tDDKHAS                                                                              |

|   | Tost Drogram           |                 | 800 Mbps data rate (Min) 0.767 ns                                                                                              |

|   | Test Program           |                 |                                                                                                                                |

|   |                        |                 | ADDR/CMD output hold with respect to MCK tDDKHAX                                                                               |

|   |                        |                 | 800 Mbps data rate (Min) 0.767 ns                                                                                              |

|   | Development From       |                 |                                                                                                                                |

|   |                        |                 | MCS[n] output setup with respect to MCK tDDKHCS                                                                                |

|   |                        |                 | 800 Mbps data rate (Min) 0.767 ns                                                                                              |

|   | Scratch                |                 |                                                                                                                                |

|   |                        |                 | MCS[n] output hold with respect to MCK tDDKHCX                                                                                 |

|   |                        |                 | 800 Mbps data rate (Min) 0.767 ns                                                                                              |

| • | Completed in Less      |                 |                                                                                                                                |

|   | completed in Less      |                 | MCK to MDQS Skew tDDKHMH                                                                                                       |

|   |                        |                 | 800 Mbps data rate (min) –0.525 ns (max) 0.525 ns                                                                              |

|   | Then 24 Meeks          | DDR3            |                                                                                                                                |

|   | Than 24 Weeks          | Ethernet        | Verify Ethernet functionality                                                                                                  |

|   |                        | MMU, L2         | Exercise L2 Cache. Assure FPU instructions are tested. Verify MMU mapping from effective addressing to physical                |

|   |                        | Cache and FPU   | addressing                                                                                                                     |

|   |                        |                 |                                                                                                                                |

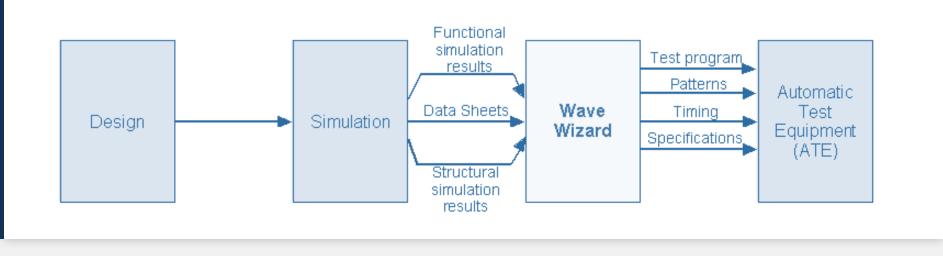

### **Traditional Test Vector Generation Method**

- Device Design Environment

- Modeling Integrated with Design

- Simulation to Generate Test Patterns

- BIST / SCAN Functional

- Simulation Patterns Converted to Tester Patterns

- Final Test Generated

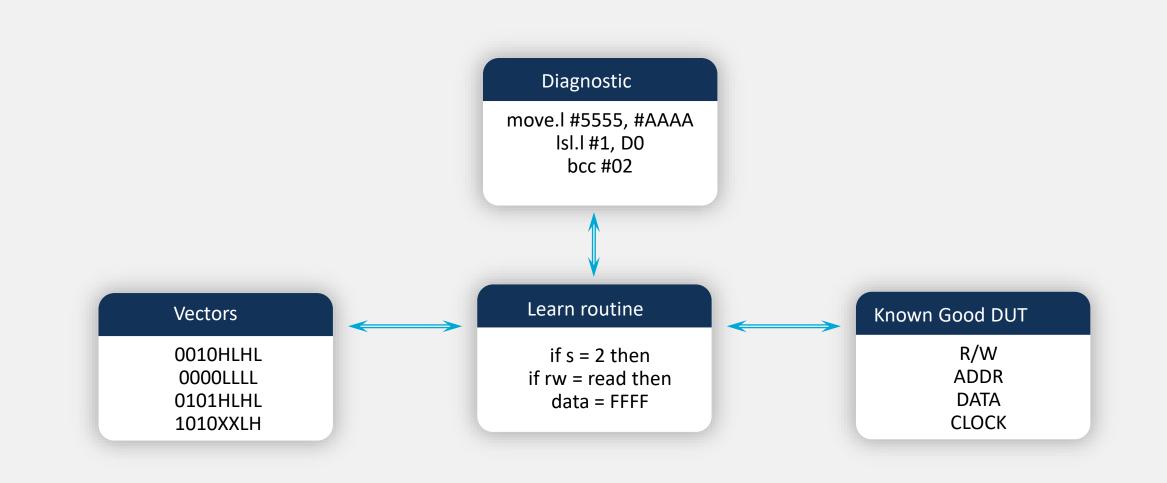

### **How to Develop Microprocessor Vectors**

Must Fully Understand the Device

Testers work on time cycles / implement timing model into tester

Build a Microprocessor Development System

• Device bus cycle timing implemented in tester

- Developed tester s/w monitors device operation and pin status

- Complied device assembly language loaded to the device

- The device is operating functionally just as it would in an application

Use a Known Good Device

- Hardware simulator is the known good die

- Tester load board and tester resources are the hardware

Tester Records the Device Operation

**On Tester**

Build a

Software

Model of the

Device

Interface

• Saved as a test vector file

## **Special Tester Requirements**

| Tester Algorithmically Writes Vectors on the Fly                                                                                                                       | Rewrite Vectors in Memory                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software routine in the tester reviews each vector<br>Next vector is generated according to the device<br>protocol<br>Validity of results must be analyzed by engineer | <ul> <li>Pass fail pin register allows on-the-fly changes</li> <li>Test vector is corrected</li> <li>Executable vector code results</li> </ul>              |

| Tester Register Stores State of Pass/Fail                                                                                                                              | Incremental Process                                                                                                                                         |

| Typically non-user tester registers are required<br>Tester hardware manuals are consulted                                                                              | <ul> <li>S/W loops executable vectors to correct and add<br/>additional vectors</li> <li>At completion corrected/generated vectors are<br/>saved</li> </ul> |

### **Vector by Vector Generation**

- Input to the program is assembled code

- First word of code is converted to binary and applied to input pins

- Control pins are monitored to determine the type of bus cycle (read/write)

- Continue clocking, recording the outputs until the end of that bus cycle

- Read the next word of assembled code and repeat

- Stop when no more input code

- Save memory to file

- Added test methods

- Memory testing

- Algorithmic Pattern Generation

- Checkerboard / Invers checkerboard

- March Patterns

- High Speed BUS testing

- Loop Back methods high speed serial buses

Process

21

### **Test Generation**

## **Recommended Test Methodology**

### Test the Device the Specified Performance Characteristics

- Functional at-speed

- Application speed at a minimum may not need spec speed

- Test frequency is a major tester cost driver

- Comprehensive functional testing

- Test all device functionality

- Fault grading is not possible Only the manufacturer has device modeling capability

- Test key AC parameters

- Key parameters are usually referenced to device clocks Propagation delay Setup and hold times

- Use go-no-go testing to cover most AC parameters Tested over the entire functional pattern

- Selected AC characterization measurements can be made

- DC measurements to the full specified limits

- Attempt to test 25C parameters at extended temperatures

- Limit adjustments may be

required after testing

- Select the appropriate tester

- No one tester can effectively test all technologies

### **FPGA Development Experience**

#### **Over-All**

- Integra engineers have developed over 300 test programs for FPGAs

- Xilinx

- Intel (Altera)

- Microchip (Microsemi)

- 150+ FPGA test programs have been developed

- Design software and testing methodologies are in place for all FPGA families

- Integra has an experienced and trained staff in place

- 5 engineers with FPGA test development experience

- Multiple projects using Xilinx Vivado Design Suite (ISE)

#### **Xilinx: Examples of Programs Include**

- Various Iterations of Virtex 7

- Various Iteration of Virtex 5

- XC4VFX100-11FF1152C

- XQ2VP40-5FF1152N

- XC4VFX20-10FFG672C

- XC6VLX75T-3FF484C

- XC6SLX45-L1CSG324I

## **FPGA Test Methodology**

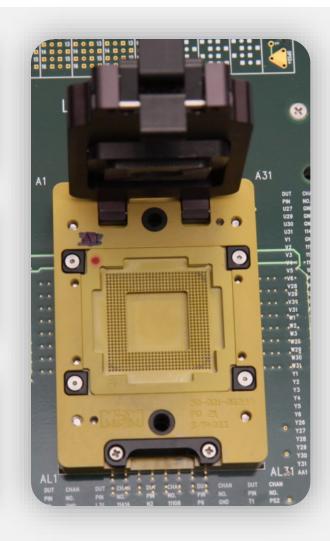

#### Integra Implements Designs into the FPGA to Support Functional and Parametric Testing

- Test develops independent of manufacturer proprietary test methods

- Integra uses in-house tools from the manufacturer

- Create the test vectors and configuration vectors for the 93K tester

- Functional at-speed testing (using design modeling not datasheet)

- Datasheet AC specs are internal FPGA performance characteristics

- AC parameter tests will be generated from Xilinx software simulations

- Designs implementation includes comprehensive DC parameters

- Develop functional vectors verifies design and device functionality

### **FPGA Test Methodology**

- Functional evaluation to actual application design

- Development of test vectors to user application

- Critical timing parameters testable to the application requirements

- Characterization of device performance to application is possible

## **Electrical Test of Today's Complex COTs Memory Devices**

## **Memory Test Complexities**

#### Volatile Memory

- Topological addressing is preferred for all types of RAM memories (proprietary to OEM but covered under NDA)

- Can't do silicon memory array F/A without this info

- OEM tests 100% topologically where Row/Column/Block addressed is accomplished from Physical standpoint for best adjacent cell disturb testing in conjunction with Margin testing

- DRAMS: FPM, EDO, VRAM, SDRAM, QDR, DDR, DDR2, DDR3, DDR4 .....

- TREF(Refresh) parameter always an issue for full Mil-Temp of -55C to 125C, usually ¼ of commercial spec used as TREF halves every 10-12C after 70C. Or user takes yield hit

- For Mil-Aero use , staying away from the 'just released' versions(i.e.. Die technology shrinks, new fab process, leading edge devices) is good policy

- Fab process maturity is key Reliability variable so unless you like looking over the edge of cliff's, best to wait 1-yr for process maturity.

- Request CZ-Data from Commercial Mfg-er, lots of good data nuggets even if only 0-70C, most will do extended Temp CZ of typ -40C to +85C, the more Elite companies like Micron, Samsung, Cypress & TI will do -55C to 125C.

- If enough volume , parallel site testing preferred like 4-site for lower costs and faster turn at test.

- Speed is no issue, we can adjust our speed license on the tester as needed up to 3600Mbps.

- SPANS: Asyme Syme ODD Serial NV/DAM Ultra Low Dower MDAM EDAM DeDAM

- SRAMS: Async, Sync, QDR, Serial, NVRAM, Ultra Low Power, MRAM, FRAM. ReRAM, ......

- 'Cold Start Power-UP': Ask yourself this question, what power up time assumption is used by the system designer? This is One parameters not normally specified in SRAM datasheet

- DRAM does a good job of outlining this sequence But SRAM not so good. 10ms would be assumed but I have seen small % of parts not meet this , becomes yield liability

- ATD (Address Transition Detection) special algorithm needed to target worst case scenario of single address line change that forms the access pulse edges.

- To catch race conditions on too fast process material

- Ground bounce affects: this as much about the load board design and decoupling as the output switching rates. The >FFFF to >0000 output switch can be disaster on poor load board design.

- CMOS Std-by as shown on the opening slide & Weak bit algorithms like specialized Gal-Pat.

- Still see occasional 4T-2R SRAM cell, in which properly testing Data Retention at cold temp is paramount.

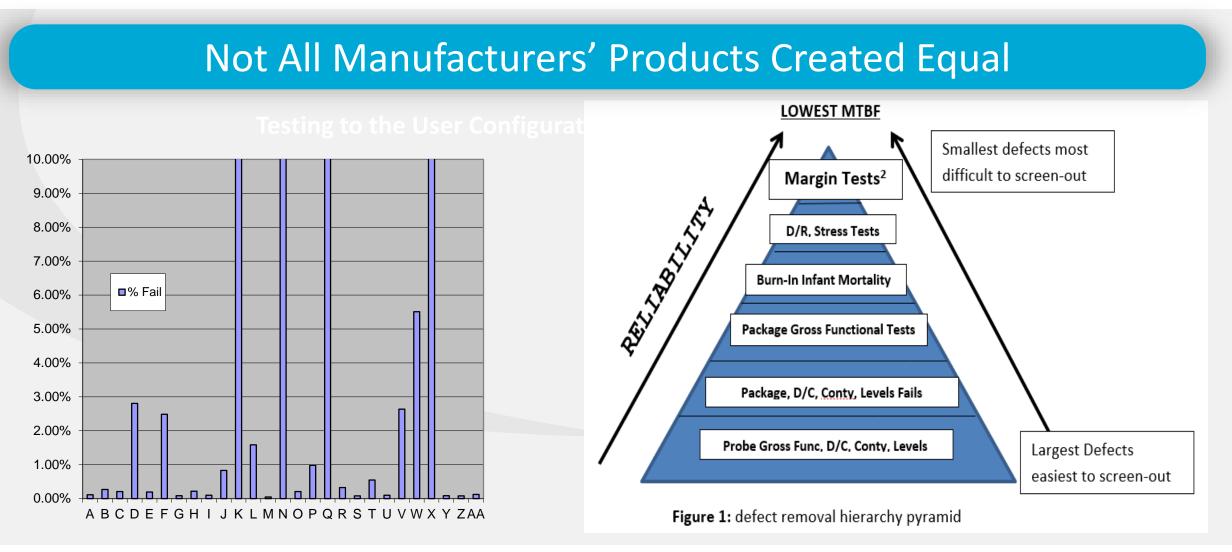

### **Common Reasons for Testing Memory Devices**

Shrinking package sizes means higher densities which translates to increased risk of being affected by even small defects in the manufacturing or assembly processes.

- Activation of unwanted particulate may not be detected without screening at extended temperature.

- Electrical test at application usage condition temperatures can identify potential reliability issues not seen by the OCM at the temperatures used for production testing.

#### What are the signatures of potential reliability concerns?

- Outlier /atypical standby (quiescent) supply current readings.

- Weak bits that exhibit instabilities at extended temperature or during functional tests that are known to highlight vulnerabilities for a particular type of memory device.

- Cold start issues, especially with DRAM and fast SRAM devices.

- Refresh issues with DRAM devices at elevated temperature.

### **Memorys - Device Specific Functional Tests**

#### • SRAM

- Data retention tests.

- Write / Read all 1's, all 0's, checker board and inverse checkerboard patterns.

• Flash

- Pseudo Random pattern and it's inverse

- EEPROM

- Checkerboard & Inverse Checkerboard

- DRAM

- March X

In all cases referenced above, critical timing characteristics are validated by using them as setup parameters for the functional test.

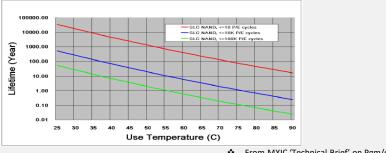

### **NAND Flash Program/Erase Cycling Endurance & Data Retention**

- Cycling Endurance defined as the capability to perform to specification if the number of P/E cycles are within the datasheet specification. Typically between 50K to 100K cycles. Certain number of Bad Blocks are allowable which is the NVB(number of valid blocks) min spec.

- Data Retention(D/R) defined as is the capability of retaining stored data, in unbiased condition over time; typically 10 years.

From MXIC 'Technical Brief' on Pgm/erase cycling and D/R connection

- SLC NAND Flash cell is predominantly the choice of MILAERO users due to more robust threshold voltage margins on the cell state versus MLC.

- Additional design mitigation by the user to achieve Longer D/R would be in the form of wear leveling, data refresh, & stronger ECC.

- Section JEDEC Recommended Standards to consider when designing Qual/Reliability Exercise for Endurance/Data Retention

- JESD47K "Stress-Test-Driven Qualification of Integrated Circuits"

- Section 2012 Secti

- JESD94A "Application Specific Qualification Using Knowledge Based Test Methodology"

- JEP122H "Failure Mechanism & Models for Semiconductors Devices"

#### \* Customer must select Conditions to be used for Endurance/Data Retention normally based on Application usage

# of Pgm/Erase P/E Cycles, fraction of cells cycled to full Spec, Fraction cycled to other percentage(very important for esp large densities), Temperature of Cycling Chamber (25C, 55C or 85C?), VCC level (nom or max?), Data Pattern to be cycled, If cold temp cycling needed and what conditions, Intentional delays, ECC mgmt applied, periodic reads during endurance or every cycle, UBER value if applicable, # of devices to subjected to what stresses, Arrhenius variables for acceleration calc

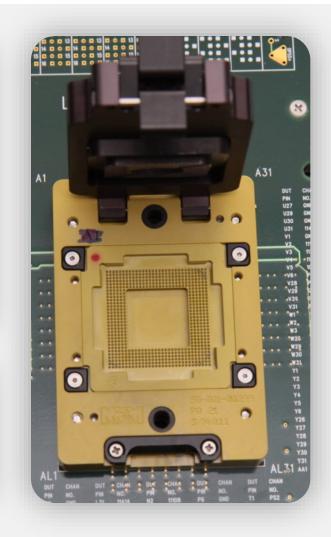

### **Advanced Memory Tester – Smart Scale from Advantest**

| Group 7   |                   | Group 8            |                     | Gro   | up 2     |             |   | Group 6 |   |

|-----------|-------------------|--------------------|---------------------|-------|----------|-------------|---|---------|---|

|           | Utility           |                    | Utility             | HV-I  | DPS #2   | Utility     |   |         | ι |

| 224:      | 220:              | 232:               | 228:                | 116   | : PS1600 | 112: PS1600 |   | 216:    | : |

| 223:      | 219:              | 231:               | 227/427: DPS128-HC  | 115   | : PS1600 | 111: PS1600 |   | 215:    |   |

| 222:      | 218:              | 230/430: DPS128-HV | 226:                | 114   | : PS1600 | 110: PS1600 |   | 214:    |   |

| 221:      | 217:              | 229/429: DPS128-HV | 225/425: DPS128-HC  | 113   | : PS1600 | 109: PS1600 |   | 213:    |   |

|           |                   |                    |                     |       |          |             | ] |         |   |

| 125:      | 129:              | 117: PS1600        | 121: PS1600         | 101   | : PS1600 | 105: PS1600 |   | 201:    |   |

| 126:      | 130:              | 118: PS1600        | 122: PS1600         | 102   | : PS1600 | 106: PS1600 |   | 202:    |   |

| 127:      | 131:              | 119: PS1600        | 123: PS1600         | 103   | : PS1600 | 107: PS1600 |   | 203:    |   |

| 128:      | 132:              | 120: PS1600        | 124: PS1600         | 104   | : PS1600 | 108: PS1600 |   | 204:    |   |

| Jtility   |                   | Utility            |                     | Utili | ty       |             |   | Utility |   |

| Group4    |                   | Group3             |                     | Gro   | up1      |             |   | Group5  |   |

|           |                   |                    | Number of resources |       |          |             | - |         |   |

| PS1600    | PS1600 dig.Pin    |                    | 384                 |       |          |             |   |         |   |

| DPS128 HV | -6V/15V (Max curr | ent 0,2A)          | 64                  |       |          |             |   |         |   |

| DPS128 HC | -2,5V/7V (Max cur | rent 0,5A)         | 64                  |       |          |             |   |         |   |

4

Existing test solutions for DDR3,DDR4 are in place with system architecture upgradable to support higher speeds and higher device pin counts.

Utility 212: 211:

210: 209:

205: 206:

207:

208:

Z640 PC w/ Red Hat Enterprise Linux 5

+ 0.5 V to 22 V (Max current 1A)

HV-DPS #2

SmartTest Versions soc64 7.2.3.5 soc64 7.4.3.4

### **Temperature Testing Considerations**

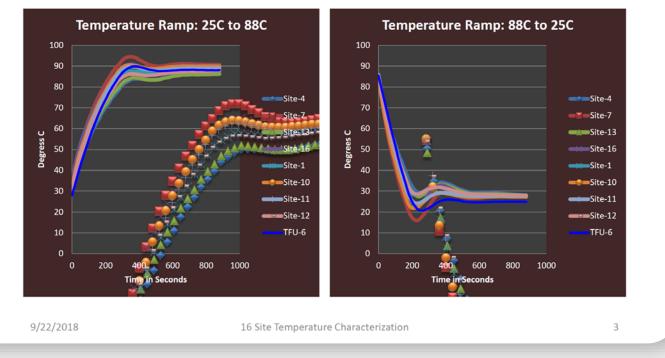

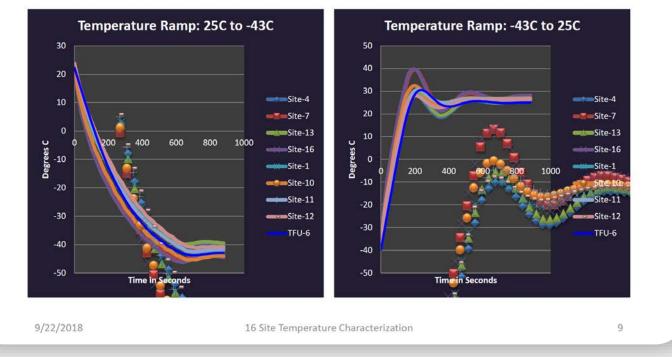

### **Example of Temperature Characterization – 512 NAND Flash - BGA**

### **Characterization Tools & Method**

- Four calibrated and certified RTDs part number # HEL-705-U-1-12-C2

- Four calibrated Keithley 2402B source meters

- Threaded ferrules for holding RTDs in socket lid

- One calibrated Temptronic TP04300A Thermostream

- 8 of 16 sites were measured. The thermostream thermocouple was used in **Site 6**. The measured sites were the four corner and four center sites.

- Temperature was measured from 25C to 88C, 88C to 25C, 25c to -43c, and -43c to 25c; Four sites at a time.

- A program was written to sample the measurements in 20 second increments for a total duration of 15 minutes for each temperature sweep.

- Floor temperature was 22C.

- Data was taken without bias.

### Room to High Temperature Characterization Plots

Ramp Temperature for Corner and Center Sites: 25C to 88C Temperature Ramp for Corner and Center Sites: 88C to 25C

2

### Room to Low Temperature Characterization Plots

Ramp Temperature for Corner and Center Sites: 25C to -43C Temperature Ramp for Corner and Center Sites: -43C to 25C

3

### Summary

- Site temperature distribution was within a 6c window for all sites at all temperatures measured within 15 minute time window with the following observations:

- Corner sites 4 and 13 for the 25C to 85C ramp contributed to wider temp distribution.

- Corner sites 4 and 13 for the 25C to -43C ramp contributed to wider temp distribution.

- In both cases, sites 4 and 13 had not reached final temperature within 15 minute window.

- Temperature ranges for all sites and all cases were within +/- 3C of the temperature measured by the thermostream after 15 minutes.

- > Additional soak times would further narrow the overall site to site tolerance

- Overall, temperature uniformity is good.

- Internal sites reach temperature faster than corner sites.

- Placing thermocouple on an internal site is best location based on data.

- Soak time to guarantee proper test temperatures:

- > 25C to 88C: 12 Minutes Ramp Time (min) plus 5 Minutes Soak Time.

- > 25C to -43C: 14 Minutes Ramp Time (min) plus 5 Minutes Soak Time.

- -43C to 88C: 17 Minutes Ramp Time (min) plus 5 Minutes Soak Time. (Pleliminary)

#### 4

### Recommendations

- Place Thermocouple at any of 4 interior sites for Thermostream control

- In the test program for 25C to -43C, place 19 minute delay after Thermostream starts ramp before test begins.

- > Place a 14 minute wait time in the test program after thermostream start.

- Check to see if thermostream is at temperature and continue is yes.

- Wait 5 additional minutes for soak.

- Begin device test.

- In the test program for -43C to 88C (Preliminary), place a 22 minute delay after Thermostream starts ramp before test begins.

- Place a 17 minute wait time in the test program after thermostream starts.

- > Check to see if thermostream is at temperature and continue is yes.

- Wait 5 additional minutes for soak.

- Begin device test.

- In the test program for any temperature to 25C, place a 12 minute delay after Thermostream starts ramp. Wait 5 additional minutes for soak.

## **Questions?**

#### **Contact info:**

Jonathan.Hochstetler@integra-tech.com (316.630.6828)

Sultan.Lilani@Integra-tech.com (510.830.9216)

Thank you from the Employee Owners of Integra Technologies!!