National Aeronautics and Space Administration

## MIL-PRF-38535 Standard Microcircuits Hermetic and Non-hermetic

June 13, 2022

#### Shri G. Agarwal

NASA – Jet Propulsion Laboratory, California Institute of Technology Shri.g.agarwal@jpl.nasa.gov 818-354-5598

This artist's concept depicts astronauts and human habitats on Mars. NASA's Mars 2020 rover will carry a number of technologies that could make Mars safer and easier to explore for humans. JPL is building and will manage operations of the Mars 2020 rover for the NASA Science Mission Directorate at the agency's headquarters in Washington.

Image Credit: NASA

Presented at NEPP ETW, 13-16June2022 (Electronic Technology Workshop)

- The mission assurance organizations at NASA have supported many space missions/programs, large and small. Today, that spectrum has got wider, ranging from smallsats/cubesats to flagship missions such as the planned Europa mission. As always, the success of each and every mission counts.

- This presentation is about infusion of new technology into the standards for microcircuits, and the work underway to meet the needs of new missions.

## **Partnerships** (NEPAG is about collaboration)

#### JEDEC JC-13 **SAE CE-11/CE-12** (Industry Users, Primes, Subs) (Manufacturers) JC-13 Solid State Devices for SAE Users of Passive **Government Products** SSTC Joint meetings held Components **CE-11** 3 times a year JC-13.1 **Discrete Semiconductors** for Government Products SAE Users of Solid State SSTC Devices JC-13.2 Microelectronics for **CE-12 Government Products CE-12 Management: Co-Chairs: S. Agarwal** JC-13.4 **Radiation Hardness** (NASA) and A. Touw TWENTY TWO LEAD JC-13.5 Hybrids and Multi-chip (Boeing) Modules for Government Products USAF AFLCMC/E285 DI Community SAE Pursuing Excellence Space Subcommittee SSTC COMMUN JC-13.7 New Electronic Device Chair: P. Majewicz (NASA) USAFIICBM SW-CE-11 & Insertion for Government **CE-12** Products Since 2000 <sup>onic</sup> Parts Ase OIGIDEP . USNINAVS **NASA Centers:** Partners from Outside NASA: Domestic JHU/APL. Others ARC JSC The Aerospace Corp, GRC KSC Weekly NEPAG and Biweekly U.S. Air Force, U.S. Navy, GSFC LaRC **GWG** Telecons U.S. Army, MDA, DLA JPL **MSFC** (Domestic) International Monthly Telecons ESA, JAXA, CSA (International and HWG)

#### Space Parts World NEPAG helps to Develop/Maintain Standards for Electronic Parts

The parts users and standards organizations work with suppliers to ensure availability of standard parts for NASA, DoD, and others. For Space microcircuits, DLA, NASA/JPL (S. Agarwal\*) and the U.S. Air Force / Aerospace Corp. (L. Harzstark) form the Qualifying Activity (QA).

\*Also Systems, Standards and Technology Council (SSTC) CE-12 Co-Chair.

## **Microcircuit Standards Development**

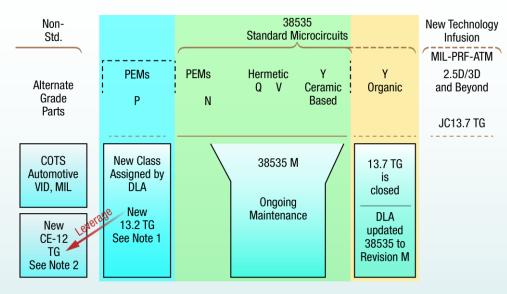

- Note 1: Standard PEMs for Space (QMLP) initiative using SAE AS6294 as baseline. Supported by NASA Parts Bulletins on PEMs.

- Note 2: For alternate grade microcircuits, follow the activity in 13.2 TG to avoid any duplication of effort.

- Note 3: ATM = Advanced Technology Microcircuits. Supported by NASA parts bulletin on KGD.

- Note 4: VID = Vendor Item Drawing. Contact DLA for latest information.

- Note 5: The boundaries separating various classes/grades must be clearly defined - future outreach activity.

- (1) The green area shows existing standards coverage.

- (2) Task Groups: Some excellent progress was reported by task groups (TGs) developing standards.

- (a) Organic Class Y. The draft of MIL-PRF-38535 revision M which includes Organic Class Y was released Feb 28, 2022. This is shown as the yellow area. A NASA/JPL project has baselined Organic Class Y.

- (b) QMLP, Standard for rad hard/rad tolerant plastic encapsulated microcircuit (PEM) devices. The TG has developed the requirements and forwarded them to DLA for incorporation into the microcircuit's specification, MIL-PRF-38535. This would enable NASA and other agencies/users to be able to procure standard PEM (QMLP) parts for use in space applications without having to worry about upscreening, yield losses and potential non-conformances. The flight projects would realize considerable cost savings. Several manufacturers have already planned releases of their QMLP products. NASA is planning to include QMLP in its 8739.11 document. See blue shaded area in the chart above.

## Standard RH/RT PEMs for Space "Taking SAE AS6294 to the Finish Line"

- SAE CE-12 spent considerable effort in developing a PEM flow for space.

- o Developed SAE AS6294, Requirements for Plastic Encapsulated Microcircuits.

- ✤ /1 for space, /2 for terrestrial.

- The SAE AS6294 baselined

- o NASA documents

- ✤ MSFC-STD-3012, GSFC EEE-INST-002, GSFC PEMS-INST-001

- o And, SAE SSB-001

- However, it never became a standard QML flow

- Lately, considerable interest in the use of standard plastic parts in space

- O Mainly being driven by power management applications

- Performance, size, weight advantages; slight cost advantage

- Some applications: Cubesats, smallsats, science instruments

- New emerging market, does not affect the demand for QMLV products

- Was discussed on NEPAG (Domestic and International) and GWG telecons

- We decided to take a fresher look what would it take for the SAE AS6294 to become a standard PEMs flow for Space.

- o Several manufacturers offering products built to a flow similar to AS6294

- o Actions:

- ✤ JC13.2 to vote on a TG (September 2020)

- > T.I. and Boeing to co-lead

- > NEPAG government working group (GWG) to provide support

#### Update (December 18, 2020):

- O JC-13.2 opened a new Task Group, chaired by S. Williams (T.I.) and R. DeLeon (Boeing).

- O NASA published two parts bulletins on PEMs.

- O DLA assigned a new class letter "P" to standard PEMs in Space.

- Goal is for NASA and other agencies/users to be able to procure standard (QMLP) parts for use in space applications without having to worry about upscreening commercial plastic parts.

## What if A New Product Didn't Fit Any of the Existing Classifications? The "Class Y" Initiative

- It was recognized by the community that packaging and device technology advances are happening rapidly.

- In order to enable space flight projects to benefit from the newly developed devices, e.g., Xilinx Virtex-4 and -5 FPGAs (which are ceramic-based flip-chip nonhermetic parts), a new class was needed.

- NASA led a CE-12 initiative, called Class Y, for infusing Xilinx FPGAs and other similar devices into military/space standards.

- Such an effort must be coordinated with the suppliers and users.

- Need to address all aspects of packaging configuration.

- New test methods must be created and the existing standards updated as necessary.

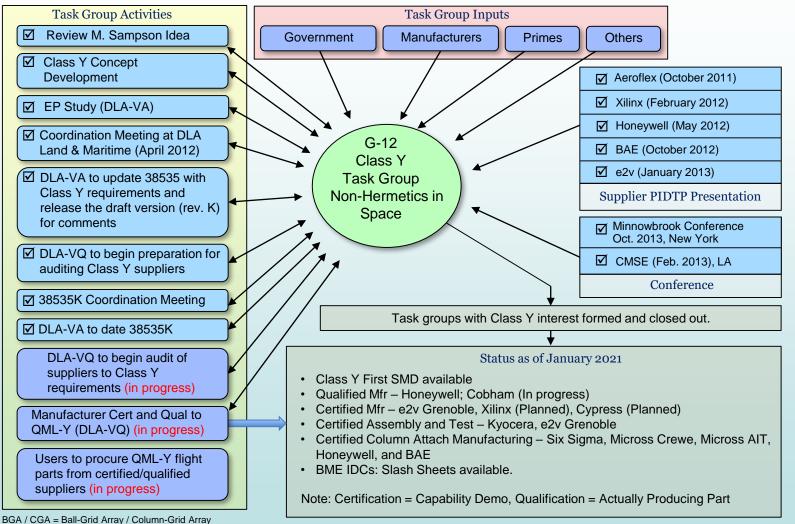

## **Class Y, A New Beginning for New Technology Infusion**

## • ClassY

- It represents advancements in packaging technology, increasing functional density, and increasing operating frequency. These are ceramic based single-die system-on-a-chip (SoCs) with non-hermetic flip-chip construction, in high-pin-count ceramic column grid array (CGA) packages. These products use tiny base electrode metal (BME) capacitors for signal integrity, and vented packages for thermal management. (e.g., Xilinx Virtex-4 FPGAs)

- To address the manufacturability, test, quality, and reliability issues unique to new non-traditional assembly/package technologies intended for space applications

- Introduced a new concept called Package Integrity Demonstration Test Plan (PIDTP) – provided flexibility to manufacturers.

- This initiative resulted in a major overhaul of MIL-PRF-38535, particularly with respect to requirements for flip-chip, underfill, CSAM, column grid arrays, etc. Revision K reflecting these changes was released in December 2013.

- Started JC-13.7 to address infusion of new technology

### Infusion of New Technology into the Standards (Ceramic Based) Class Y Status, January 2021

BME = Base Metal Electrode

PIDTP = Package Integrity Demonstration Test Plan

IDC = Inter Digitized Capacitor

SMD = Standard Microcircuit Drawing

## An Example of SMD Boiler Plate Update

TABLE IIA. Electrical test requirements.

| Line<br>Number | Test requirements                                     | Subgroups (in accordance with MIL-PRF-38535, table III) |                                        |  |  |

|----------------|-------------------------------------------------------|---------------------------------------------------------|----------------------------------------|--|--|

| Number         |                                                       | Device class Q                                          | Device class V                         |  |  |

| 1              | Interim electrical parameters (see 4.2)               | 1,2,3,7,8A,<br>8B,9,10,11 <u>1</u> /                    | 1,2,3,7,8A,<br>8B,9,10,11 <u>1</u> /   |  |  |

| 2              | Static burn-in I and II<br>(method 1015)              | Not required                                            | Required                               |  |  |

| 3              | Same as line 1                                        |                                                         | 1,7 ∆ <u>1</u> / <u>2</u> /            |  |  |

| 4              | Dynamic burn-in<br>(method 1015)                      | Required                                                | Required                               |  |  |

| 5              | Same as line 1                                        | 1,7∆ <u>1</u> / <u>2</u> /                              | 1,7∆ <u>1</u> / <u>2</u> /             |  |  |

| 6              | Final electrical parameters                           | 1,2,3,7,8A,8B,9,<br>10,11 <u>1</u> /                    | 1,2,3,7,8A,8B,9,<br>10,11 <u>1</u> /   |  |  |

| 7              | Group A test requirements <u>3</u> /                  | 1,2,3,4,7,8A,8B,9,10<br>,11 <u>4</u> /                  | 1,2,3,4,7,8A,8B,9,<br>10,11 <u>4</u> / |  |  |

| 8              | Group C end-point electrical parameters <u>3</u> /    | 1,2,3,7,8A,8B,<br>9,10,11 ∆ <u>2</u> /                  | 1,2,3,7,8A,8B,<br>9,10,11              |  |  |

| 9              | Group D end-point electrical parameters <u>5</u> /    | 2,3,8A,8B                                               | 2,3,8A,8B                              |  |  |

| 10             | Group E end-point electrical parameters<br><u>3</u> / | 1,7,9                                                   | 1,7,9                                  |  |  |

| 11             | Column attach <u>6</u> /                              | 1,7,9                                                   | 1,7,9                                  |  |  |

- For Flip-chip column attach

- Add room temperature electricals (subgroups 1, 7, 9) after column attach step 11 above

## **Class Y Qualification Status**

- Honeywell Aerospace Plymouth

- Complete

- o SMD 5962-17B01

- Title: Microcircuit, Ceramic Non-Hermetic, Flip Chip, Digital, CMOS SOI, Gate Array, HX5000, Radiation Hardened, Monolithic Silicon

- Cobham Colorado Springs

- o In progress

- o SMD 5962-17B02

- Tentative Title: Microcircuit, Digital, Radiation Hardened, 90nm Standard Cell, Monolithic Silicon, Class Y, Radiation Hardened, Monolithic Silicon

- Teledyne e2V Grenoble France

- In progress

- o SMD 5962-19205

- High performance processor, PC8548

- Cypress Semiconductor

- o Planned

- 144 Mbit QDR IV SRAM

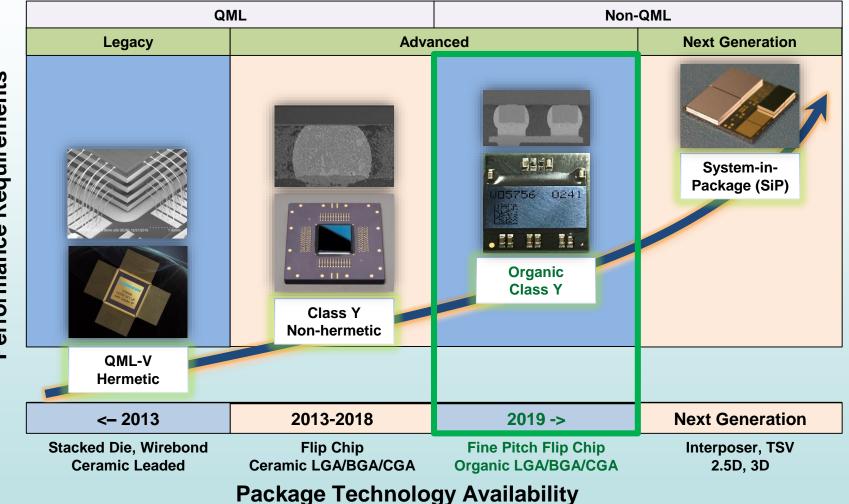

## **ClassY Moving Forward**

- A Follow-on to Ceramic Substrate Class Y

- Interest in organic Class Y, and molded plastic parts had been growing.

- The JC-13.7 created a new task group on organic substrate Class Y (September 2018).

- Related task groups started as well (next slide)

- Defense Logistics Agency (DLA) conducted an EP (Engineering Practice) study

#### Next Generation Package Technology for Space Development Roadmap for Space Applications

Credit: Scott Popelar, Cobham, 2019 MRQW, February 7, 2019

Performance Requirements

## **MIL-PRF-ATM (DLA Proposal)**

**Reference Factors**

<u>Background:</u> MIL-PRF-38535 offered traditional hermetic class Q and V (class level B, S) and non-hermetic class N and Y devices for military, terrestrial, avionics and space applications. Design requirements of modern electronic satellite/warfare systems are growing faster and moving forward with newer advanced technologies. Considering the complexity of new technologies and device packaging (i.e. 2.5D, 3D type devices) techniques, the current MIL-PRF-38535 may not be the best requirements platform to accommodate for manufacturing these complex and advanced new technology devices.

Accordingly, to bring advancement and adoption of new technologies into the QML system, DLA Land and Maritime is proposing to create a new performance specification, MIL-PRF-ATM applying the Package Integrity Demonstration Test Plan (PIDTP) process to the entire microcircuit manufacturing process. This process was developed for class Y flip chip packages and is successfully used in MIL-PRF-38535 PIDTP requirements.

A JC13.7 task group has been formed to develop the requirements for MIL-PRF-ATM.

ATM = Advanced Technology Microcircuits

## **MIL-PRF-ATM**

- ATM Devices include:

- o Flip-chip 2.5D, 3D

- System In Package (SIP)

- Multi Chip Module (MCM)

- ATM Devices class and application environment:

- Class M for military(terrestrial and avionics) application

- Class S for Space application

#### Burn-in, and Life Test Comments from NASA

- 1. The regression tables need a fresher look

- NASA computations show a large variation in the activation energies (Ea). See summary below

- 1a. Regression Table in MIL-STD-883, Test Method 1005

- For Class B, Ea range = 0.971eV to 0.986eV

- For Class S, Ea = 0.292eV to 0.403eV

- o Considerable variation in Ea values

- For currently quoted Ea of 0.7eV

- Class B is less conservative

- Class S is more conservative

- 1b. Regression Table in MIL-STD-883, Test Method 1015

- For Class B, Ea = 0.397eV to 0.409eV

- For Class S, Ea = 0.383eV to 0.403eV

- o Considerable variation in Ea values

- For currently cited Ea of 0.7eV

- Both Class B and Class S are more conservative

- 1c. What is the correct Ea going forward?

- o Different sources list different values. According to one source:

- ✤ 0.3eV is for oxide/dielectric defects, chemical/galvanic/electrolytic corrosion

- 0.7eV covers electromigration, broken bonds, lifted die

- ◆ 1.0eV is for surface contamination induced shifts, lifted bonds (Au-Al interface)

- 2. For accelerated temperature burn-in, and life test

- ✤ Are the parts characterized for safe operation before they are subjected to elevated temperatures?

- Recommend making it a requirement

- 3. JEP 163 Document

- Is there a plan to update this document?

- Credits: (1) S. Agarwal, A. Hanelli, M. Han, D. Gallagher, N. Ovee, S. Khandker, R. Evans of NASA/JPL Cal Tech (2) Subject discussion in 12 Aug, 2020 NASA Electronic Parts Assurance Group (NEPAG) telecon.

#### **Some Notes on Fracture Mechanics in Plastic Packages**

#### PEMs

٠

- Lots of JC13/CE-12 activity to develop Standards for Microcircuits

- \* Heavy discussion on plastic parts in the next 2-3 years (and beyond)

- **Solution** Both ends of the spectrum: overmolded, and organic

- Now is a good time to review the fundamentals of plastic packages the community is making heavy investment in them to cover expanded application spectrum/ infuse new technology

- Temp cycling

- Done per MIL-STD-883, Test Method 1010

- > Condition C: -65C to +150C, used for ceramic parts

- > Condition B: -55C to +125C, being proposed for PEMs for Space

- ➢ Condition A: -55C to +85C

- > How about the ramp rates, dwell times?

- Glass Transition Temperature

- No one seems to talk about it any more, has been a mystery

- Always measured lower than specified (JPL experience from several years ago)

- Packages are getting smaller, thinner

- \* A GaN device that NASA/JPL wants to use, comes in a 8mm x 8mm size package

- Post Assembly

- Are any parts issues (e.g., crack propagation) off limits (IPC problem?)

- CTE mismatches

- Time dependence

- \* (Ceramic) SMD-.5 packages had problems at temp cycling after they were mounted on boards

- Would plastic parts be worse?

- Sring parts, IPC, manufacturer communities together

- Could a QCI type test/set of guidelines be developed at the part level?

- > Look at 38535 and 19500 products

- What tests do the materials suppliers run to demonstrate quality/reliability?

- o Making improvements to standards, performance specifications

- Is the potential impact of stress/pressure build up in plastic packages being adequately addressed?

#### Is it time to address Fracture Mechanics and Microcircuit Standards?

- To identify any gaps and assess their impact

- Plastic encapsulants, dielectric polymers, and underfill materials are subject to delamination and cracking with thermal cycling. Crack propagation during use environment exposure, drives the potential for failure of microelectronic devices and is therefore a necessary focal point in qualification and life testing.

- O Develop methodology for evaluating the time-dependent mechanical failure of semiconductor packages

- Resulting from combined effect of stress, temperature, moisture absorption and crack like defect

#### Applying Fracture Mechanics to PEMs Qualification - Key Points (J. Evans, NASA)

- Fracture is a critical reliability issue for the packaging

- Cracking of enclosure

- Delamination

- Cracking of polymer passivation

- Fracture mechanics can inform our testing

- Most critical stresses occur in assembly: greatest opportunity for defect formation

- Thermomechanical

- Hydromechanical

- Moisture control and handling of packages of critical importance

- Screening by Thermomechanical Loading Imposes Risk

- Defect propagation may occur post assembly in thermomechanical loading

- Risk increases with complex packaging

- New technology infusion is an on-going challenge.

- NASA supports a wide spectrum of space missions/programs. The success of each mission is important.

- NASA is working with the space community to help infuse new technologies into the military standards. ESD aspects should not be ignored. We encourage the world wide space community to get/stay involved in developing/updating standards.

Thank you!

20

# **BACKUP MATERIAL**

## NASA EEE Parts Bulletin, May 15, 2020

October 2019–March 2020 Volume 11, Issue 1,<sup>1</sup> May 15, 2020 Non-Hermetic and Plastic-Encapsulated Microcircuits

The mission assurance organizations at NASA have supported many large and small space missions and programs over the years. Today that spectrum has expanded, ranging from flagship missions such as Mars 2020 with its Perseverance Rover, Europa Clipper, and the proposed Europa Lander, to SmallSats/CubeSats such as the Temporal Experiment for Storms and Tropical Systems—Demonstration (TEMPEST-D) and Mars Cube One (MarCO). Plastic-encapsulated microcircuits (PEMs) have become more attractive since leading-edge alternatives are not available as space-qualified products. PEMs generally have smaller footprints and are lighter than the ceramic packages used in space-qualified products [1]. As the demand and use of non-hermetic and plastic-encapsulated microcircuits for space has increased, the scope of what future missions are capable of has also widened. This changing climate related to EEE parts selection presents new challenges for NASA, which—as always—holds the success of every mission paramount.

#### Growing Use of NASA SmallSats and CubeSats

Due to the need for low-cost communications satellites and new businesses evolving around Earth-observation services, there's been an increased interest in the use of CubeSats and SmallSats. Many NASA centers have been involved in developing and flying CubeSats and SmallSats, working together with multiple universities and industry partners. These undertakings require new product solutions for smaller, lighter, and lower-cost space-craft, which cannot be produced using traditional space-qualified electronic parts.

The reliability and radiation requirements for CubeSats and SmallSats are significantly lower than for larger spacecraft because these smaller satellites operate mainly in low Earth or geosynchronous orbits (LEO or GEO, as opposed to deep space) and for relatively short periods. Radiation-hardened, high-reliability, space-grade parts are often too expensive for such missions and do not match well with their requirements.

There are a few notable exceptions to the usual use of CubeSats, particularly MarCO-A and MarCO-B, which were the first CubeSats to fly to deep space, where they successfully supported the Interior Exploration Using Seismic Investigations, Geodesy, and Heat Transport (InSight) mission by relaying data to Earth from Mars during the entry, descent and landing stage (Figure 1). MarCO successfully demonstrated a "bring-your-own" communications-relay option for use by future Mars missions in the critical few minutes between Martian atmospheric entry and touchdown. Further, by verifying that CubeSats are a viable technology for interplanetary missions, and feasible on a short development timeline, this technology demonstration could lead to many other applications to explore and study our solar system.

Figure 1. MarCO accompanying the InSight Mars lander and relaying data to Earth as it landed on Mars.

<sup>1</sup> The EEE Parts Bulletin was not published in fiscal year 2019 (FY19). The two issues of Volume 10 were published in FY18.

**Relationity Program**

VEPAG

## **NASA EEE Parts Bulletin Special Edition: Non-Hermetic and Plastic-Encapsulated Microcircuits**, Part 2 URS296932, CL#20-6169

The mission assurance organizations at NASA have supported many large and small space missions and programs over the

years. Today, that spectrum has expanded, ranging from flagship missions such as Mars 2020 with its Perseverance Rover, Europa Clipper, and the proposed Europa Lander, to SmallSats/CubeSats such as the Temporal Experiment for Storms and Tropical Systems-Demonstration (TEMPEST-D) and Mars Cube One (MarCO). Plastic-encapsulated microcircuits (PEMs) have become more attractive since leading-edge alternatives are not available as space-qualified products. PEMs generally have smaller footprints and are lighter than the ceramic packages used in space-gualified products [1]. As the demand for and use of non-hermetic and plastic-encapsulated microcircuits for space has increased, the scope of what future missions are capable of has also widened. This changing climate of EEE parts selection presents new challenges for NASA, whichas always-holds the success of every mission paramount. In this second issue devoted to non-hermetic and plasticencapsulated microcircuits, we discuss more manufacturers' PEMs flows, and introduce the AS6294/1 aerospace standard document on "Requirements for Plastic Encapsulated Microcircuits in Space Applications."

#### Aerospace Standard AS6294/1

Due to the need for low-cost communications satellites and for new businesses evolving around Earthobservation services, there's been increased interest in the use of CubeSats and SmallSats for such missions. Many NASA centers have been involved in developing and flving CubeSats and SmallSats, working with multiple universities and industry partners. These undertakings require new product solutions for smaller, lighter, and lower-cost spacecraft that cannot be produced using traditional space-qualified products.

In 2017, a subcommittee of SAE International's Group 12 (G12) was created to standardize a PEMs flow and to address a possible future extension of the Qualified Manufacturer List (QML) system to include PEMs for space. Considerable effort was put into developing a PEMs flow for space applications, documented in SAE Aerospace Standard AS6294/1, issued in November 2017, titled "Requirements for Plastic Encapsulated Microcircuits in Space Applications," The "/1" version was directed at space applications, the "/2" version at

terrestrial applications. SAE AS6294/1 pulled information from many Marshall Space Flight Center (MSFC), Goddard Space Flight Center (GSFC), and SAE standards applicable to NASA-namely, MSFC-STD-3012, GSFC EEE-INST-002, GSEC PEMS-INST-001 and SAE SSB-001-as well as reviews of multiple industry practices.

AS6294/1 defines the requirements for screening, qualification, and lot-acceptance testing for use of PEMs in space flight applications. The level of testing is dependent on the risk approach, the application, and the reliability and radiation requirements of the mission. However, AS6294/1 contains only requirements that meet the highest known reliability for space applications. The document also addresses many concerns associated with PEMs, such as narrower operating temperature ranges and greater susceptibility to infant mortality and moisture absorption than space-grade products have [2]. AS6294/1 starts with device characterization for parts that don't meet space requirements. The characterization step includes the initial investigations needed to understand the details of the technology used in a PEM product [2]. This is crucial when the

<sup>1</sup>This issue is a follow-on to Volume 11, Issue 1, released May 15, 2020: "Non-Hermetic and Plastic Encapsulated Microcircuits."

| valuated the<br>of a PEM in a                                                                                 | Non-<br>Std.                                                       |                                        | 38535<br>Standard Microcircuits |                                 |                       | New Technology<br>Infusion                                                      |                               |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------|---------------------------------|---------------------------------|-----------------------|---------------------------------------------------------------------------------|-------------------------------|

| nding on the<br>n the manu-<br>include con-<br>evaluation,                                                    | Alternate<br>Grade<br>Parts                                        | PEMs<br>6294 Based<br>Space N          | PEMs<br>N                       | Hermetic<br>Q V                 | Y<br>Ceramic<br>Based | Y<br>Organic                                                                    | ATM<br>2.5D/3D<br>etc.<br>ATM |

| as analysis.<br>ortant infor-<br>vorkmanship,<br>ed to a PEM<br>ata gathered<br>ning and lot-<br>cation steps | COTS<br>Automotive<br>VID, MIL<br>New<br>CE-12<br>TG<br>See Note 2 | DLA EP<br>New<br>13.2 TG<br>See Note 1 |                                 | 38535 L<br>Ongoing<br>Maintenan | (                     | 13.7 TG<br>in Progress,<br>Completion<br>Jan. 2021<br>DLA to<br>Update<br>38535 |                               |

Note 1: Standard PEMs for Space initiative. Supported by NEPAG. Note 2: For alternate grade microcircuits, follow the activity in 13.2 TG d to all flight to avoid any duplication of effort. Will be discussed on the next NEPAG nd inspecting telecon (slated for Sep 30 2020). checks the

Figure 1. Options for standard, nonstandard, and new-technology microcircuits. creening test in AS6294/1.

> TG will be heavily leveraged in order to avoid any duplication of effort. See Figure 1 for details on current and future options for nonstandard, standard, and newtechnology microcircuits.

#### Manufacturer Solutions for Non-Hermetic and Plastic-Encapsulated Microcircuits

Historically, satellite programs have used space-grade, hermetically sealed, OML-V (space) and OML-O (military) qualified components for enhanced reliability and radiation hardness. With the emergence of "commercial space," there has been increased interest in using PEMs in space for a variety of reasons. Countering the concerns cited above-narrow operating temperature ranges and susceptibility to infant mortality and moisture absorption [2]-are certain advantages of PEMs over most space-grade hermetically sealed microcircuits: lower cost and weight, more advanced performance, lower power consumption, and smaller overall package size. With this new growing trend in the market, an increasing

number of suppliers now offer a wide range of enhanced plastic product solutions depending on quality, reliability, radiation, and cost. Not all of these product lines follow a consolidated test flow, and all depend on the specific tailoring that each manufacturer makes to them. Hopefully, in the near future, the industry will lean

mon flow that will be produced

develops and manufactures s for healthcare, life sciences, efense, security, and industrial ceramic and plastic, hermetic tested to various flows, O. OML-Y (non-hermetic for more. Table 1 shows Teledyne nd qualification flows and the they use [3].

space applications, sub-OML

e arrays (FPGAs) aimed at n traditional QML components shelf (COTS) components, the radiation or reliability data. For ons and constellations of small tringent cost and schedule PGAs are the optimal solutions. tolerance of QML components flight heritage, which permits

reduced screening requirements, resulting in reduced cost and lead times

Microchip also provides two space plastic flows: HiRel plastic radiation-tolerant (HP) and 8-lead plastic smalloutline (SN). The HP flow is for low-cost and high-volume requirements, typically meeting low-Earth-orbit (LEO) constellations' needs. The SN flow provides a higher screening level, including wafer lot acceptance, serialization, 100% thermal cycling, 100% burn-in, and PDA. These flows apply to both rad-hard-by-design and rad-tolerant products. Products made to these flows (SN, HP) meet gualification levels compliant with automotive requirements (AEC-O100), with the SN flow based on AS6294/1. See Table 2 for more details on the screening and qualification flows for Microchip HP and SN devices [4].

Micross offers an extensive array of COTS componentsboth hermetic and plastic-including a wide selection of power modules and small-signal discretes. They also stock a wide range of upscreened plastic products, including an assortment of integrated PEM (iPEM) memory devices that have been tested to selected highreliability performance levels. In their Retail+ products line, Micross provides customers with industry-leading

| ve used space-grade,                         | Tab             | le 1. Teledyne eZv has various plastic                                           | non-hermetic     | test flows.      |                   |                   |  |

|----------------------------------------------|-----------------|----------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|--|

| and QML-Q (military)<br>nced reliability and |                 | or Component Flows for Space<br>Comparisson-Chart-TE2VSFCC-V1' for more details) |                  |                  |                   |                   |  |

| gence of "commercial                         | n Benefit       | n Benefits "-Nx" NASA level                                                      |                  |                  |                   |                   |  |

| nterest in using PEMs                        |                 |                                                                                  | Level 1          | Level 2          | Level 3           | -EP               |  |

| untering the concerns                        |                 | Specification reference>>                                                        | EEE-INS          | T-002 / PEM-II   | NST-001           | Int. procedure    |  |

| nperature ranges and                         | ssembly         | and test site, one BOM                                                           | 4                | 4                | *                 | *                 |  |

| nd moisture absorp- datalog                  |                 |                                                                                  | 1                | ~                | 4                 |                   |  |

| of PEMs over most                            |                 | Condition/method                                                                 |                  |                  |                   |                   |  |

| microcircuits: lower                         |                 | MIL-STD-883 TM1010 cond. B (-55/125°C)                                           |                  |                  |                   |                   |  |

| performance, lower                           |                 | or C (-65/150°C)                                                                 | 20 cys - cond. E | 20 cys - cond. I | 320 cys - cond. E | 310 cys - cond. C |  |

| verall package size.                         |                 | MIL-STD-883 TM2012                                                               | *                | v                | *                 | -                 |  |

| 1                                            | diate           |                                                                                  | 240 hrs          |                  |                   |                   |  |

| market, an increasing                        | ctricals        | MIL-STD-883 TM1015 cond. D (125°C)                                               |                  | 160 hrs          | 160 hrs           | 160 hrs           |  |

| de range of enhanced                         |                 | MIL-STD-883 TM1015 conds. A, B or C (125°C)                                      |                  |                  |                   |                   |  |

| ending on quality,                           | wed)<br>tricals | Ambient temperature post dynamic                                                 | 5%               | 10%              | 10%               | 5%                |  |

| all of these product                         | cricals         | Per device specification (-55/125°C)<br>Per device specification (25°C)          | *                | ¥                | *                 |                   |  |

| w, and all depend on                         | SA)             | Per device specification (25°C)<br>Condition/method                              |                  |                  |                   |                   |  |

| inufacturer makes to                         | 514)            | TID & SEE                                                                        | Per rad tests    | Per rad tests    | Per rad tests     |                   |  |

|                                              |                 | PEM-INST-001                                                                     | 22               | 22               | Per lau tests     | •                 |  |

| the industry will lean                       |                 | Moisture soak/Reflow simulation                                                  | 32               | 32               | 17                | E 2               |  |

|                                              |                 | MIL-STD-883 TM1005 / D / 125°C                                                   | 1500 hrs / 22    | 1000 hrs / 22    | 500 hrs / 10      |                   |  |

|                                              | e cucling       | MIL-STD-883 TM10057 07 125 C                                                     | 500 cys / 22     | 200 cys / 22     | 100 cys / 10      |                   |  |

|                                              | e cycing        | PEM-INST-001                                                                     | 22               | 200 Cys / 22     | 100 0437 10       |                   |  |

| Sub-group 1b - DPA/FA                        | _               | EEE-INST-002 on 5 parts                                                          | 11               | ~                |                   |                   |  |

| Sub-group 2 - Biased HAST                    |                 | JESD22-A110 96 hrs / 130°C / 85% RH                                              | 10               |                  |                   |                   |  |

| Sub-group 2 - Unbiased I                     |                 | JESD22-A118 / A / 96 hrs / 130°C / 85% RH                                        | 20               | 10               | 7                 |                   |  |

| See Broop 2 - Olibiased i                    |                 | 3                                                                                |                  | 20               | ,                 |                   |  |

|                                              |                 | 3                                                                                |                  |                  |                   |                   |  |

1

Tass errout paset on IC13.2 completes its work a new proposed TG will be formed to support alternategrade microcircuits. The work performed by the JC13.2

leon of Boeing.

nd functional tests, a percent

value is calculated with a

rformed on parts that pass

step includes life-testing

temperatures, temperature

by failure analysis for any

As have met all requirements

ver become a standard OML

mmediately adopted in its

nufacturers, who offer their

that in AS6294/1. With the

the use of standard plastic

ns, the space community

iment and take a renewed

a standard PEMs flow for

iscussed in domestic and

nic Parts Assurance Group

open a new task group was

20 JC13.2 session, in which

task group from industry

WG support. The task group

mantha Williams of Texas

Working Group (GWG)

are cleared for flight.

2

**EPAG**

## NASA EEE Parts Bulletin Special Edition: Known Good Die (KGD)

#### URS299800, CL#21-2280

#### Known Good Die

There are many use cases for which engineers and designers elect to purchase bare die for their applications. They might integrate the die into a multichip module (MCM), or use it directly as a chip-on-board (COB), in order to meet size, cost, and mass constraints. In some special radio frequency (RF) applications a COB solution might be required to minimize the inductance and capacitance of integrated circuits leads. Furthermore, many manufacturers purchase bare die from other providers and integrate it into their packaged parts. The term "known good die" (KGD) is commonly used when referring to these die purchases; however, it is not well defined and might have different meanings depending on the manufacturer or specific use cases. In this bulletin, we describe what KGD might refer to and some of the detailed flows that KGD go through at different manufacturers.

1

#### "QML Die" in MIL-PRF-38535

Under MIL-PRF-38535, "QML die" can have several different meanings. The first is Qualified Manufacturers List (QML) die that is covered by Appendix A in the Standard Microcircuit Drawing (SMD) of the part that is offered in die form. This is commonly referred to as "SMD die" and is assigned a die code of "9" in the QML part number's case outline position. Figure 1 shows an example of such a part (5962-9663), it is important to note that the manufacturers that offer the SMD die are also expected to offer the fully packaged part (per the SMD) on the QML listing.

A 1 BODRE A 1.1 Second File sequence control control control control control control and the to be supplied upon the Southeast Meeting and the Southeast and South Records on the Southeast the majoritement of ML RePC-200000 and the southeast appeared OH data to a sum encention management in majoritements and MCDRs (hydro), second control and southeast and and the southeast and southeast and ML RePC AND and any specified hows. The provided management control and any statement of the southeast and ML RePC AND and any specified hows. The provided management control and appeared of the southeast and ML RePC AND and any specified hows. The provided management control and appeared of the southeast and appeared of the southeast and appeared of the southeast and appeared of the southeast and appeared of the southeast and appeared of the southeast and appeared of the southeast and the southeast and the southeast and the southeast and appeared to the southeast and the southeast and the southeast and the southeast and appeared to the southeast and appeared to the southeast and appeared to the southeast and the southeast an

Figure 1. SMD die example showing the die code.

For QML die products, the minimum screening steps are listed in the SMD (Section A.4.2). Some manufacturers requirements, shown in Figure 2 (from 5962-96663). ALE degregs Tradeo level of the convergence of the neorotance with ML-MM-3000, while a defined in the advanced of a data on a memory of advanced and g the convergence of the ML-MM-3000, while store a the full convergence of the AV vedeo large the convergence of the ML-MM-3000, while store its b 100% where the isolated results (AV vedeo large the convergence of the ML-MM-3000, while store its b 100% where the isolated results (AV vedeo large the convergence of the ML-3000, where its of the ML-3000, where

10% internet insult inspection to the applicable case Q or V exiting address in INL-STD-883, network 2019 or the attenue procedures advect in INL-STD-883, network 2009.

Figure 2, SMD die minimum screeening required.

might elect to do more testing than the minimum

The 100% wafer probe includes functional and parametric testing sufficient to make the packaged die capable of meeting the electrical performance requirements listed in the electrical characteristics table of the SMD, which lists parameters throughout the part's rated temperature range. It is important to note that QML die is not required to go through temperature cycling or burn-in at the die level. However, as specified in MIL-PRE-38535 Section 4.2 all OMI integrated circuits shall meet the requirements of the screens specified in Tables 1A and 1B of the specification whether or not the actual testing has been performed. The manufacturer might elect to eliminate or modify a screen based on supporting data that indicates that for the OML technology, the change is justified. For example, many manufacturers have optimized their wafer probe process and in agreement with the Defense Logistics Agency (DLA) perform it only at 25°C. If such a change is implemented, the manufacturer is still responsible for

ets all of the performance, rements of MIL-PRF-38535. s is performed on packaged quality level. Furthermore, r devices to be delivered as aples from the wafer lot shall accept level of 10(0).

e is one that comes from a y/line/process that has been vered under a QML-38535 ML die sales are not listed in cate of Conformance (CoC) ved fab would exempt the erforming a site audit of the ype of QML die are: National Texas Instruments (TI), or Jiling their wafer/die from ies/facilities/lines/processes

ove, the term "KGD" is not meanings for different ent products. Currently, fine KGD.

PRF-38534 defines KGD as "a ty and reliability level as an

#### F-19500

ed Products List (OPL), die is , JANHC and JANKC, which of the standard. Military-MIL-PRF-19500 JANHC die, lassified as MIL-PRF-19500 manufactured and sourced acility that has been used to QPL. Manufacturers of QPL can be either in-house or ust be audited and qualified ee Figure 3 for an example 9500 die (JANHCAR2N2857). specifies the screening and r JANHC and JANKC die. The equirements are congruent evaluation requirements.

| 6.5.2 Un-encapsulated devices.    | The PINs for un-encapeu   | lated devices | are co | nstruct | ed using | t)e |

|-----------------------------------|---------------------------|---------------|--------|---------|----------|-----|

|                                   |                           | JANHO         | A      | R       | 211      |     |

| JAN certification mark and qua    | sity level (see 1.5.1.2)  |               |        |         |          |     |

| Die identifiers for unercepeula   | ded devices (see 1.5.0) - |               | 1      |         |          |     |

| RHA designator (see 1.5.2) -      | one vien conservations.   |               |        | -8      |          |     |

| First number and first letter sys | mbols (see 1.5.3.1        |               |        |         | _        |     |

| Second number symbols (see        | 1532                      |               |        |         |          |     |

Figure 3. Example specification of a JANHC die.

JANHC and JANKC QPL die are electrically probed for key electrical parameters, and defective die are identified during this process. Wafer screening requirements are specified in Paragraphs G.5.2 through G.5.2.7. Screening consists of 100 percent electrical test, 100 percent visual inspection of die, and then additional screening of sample die assembled into packages. The minimum sample size is 10 die for each JANHC wafer inspection lot and 22 die for each JANKC wafer inspection lot. The OPL sample die will be assembled into the appropriate package by the OPL manufacturer prior to going through the screening process steps 4-7 listed in Appendix G, Table II, of MIL-PRF-19500. These include temperature cycling, mechanical shock or constant acceleration (JANKC die only), electrical test (read/record), hightemperature reverse bias (HTRB) electrical test read/record, burn-in, electrical test read/record, steadystate life (JANKC die only), electrical test read/record, wire-bond evaluation, die-shear evaluation, scanning electron microscope (JANKC die only), and radiationhardness assurance. Appendix G, Paragraph G.5.4 specifies that die shall be stored in dry nitrogen or another inert atmosphere. All MIL-PRF-19500 QPL die are manufactured on a DLA-audited and -certified manufacturer's wafer fabrication processing facility/line. To ensure traceability, the DLA-qualified manufacturer will provide a CoC for the die manufacturer, as required per MIL-PRF-19500, Paragraph 3.7.

MIL-PRF-19500 does not define KGD, nor does it permit non-QPL die to be used in MIL-PRF-19500 qualified products.

#### Manufacturers' Die Offerings

Many manufacturers offer products in die form at various quality levels. For example, the following manufactures offer SMD die per MIL-PRF-38535 as described above: Analog Devices, Cobham, Honeywell, Mercury, Microchip, Micross, Renesas, STMicroelectronics (ST), and TI. Some examples of

manufacturers that sell QPL tified wafer foundries/process whip, Semicoa, Sensitron, and section we'll describe a couple vels offered by some MIL-PRFdemonstrate a few available

pace-qualified products in die e products are offered in two g Model (EM), and Flight Model ared in two different flows, the packaged products are ce Components Coordination neral manufacturing flow for

own in Figure 4. samic Part Average Testing is as of today elemented for most diodes. For bipolar nations and MOSFETs, both Part Average ting and Geographical Part Average Testing are elemented. Electrical water sort (EWS) is done 100% of die at 25°C.

t Wafer Lot Qualification is made by sampling on blaged parts. It is indeed performed on each fer whenever the wafer-to-wafer variations are tranginal vis the part-to-part variations. In radiation text is only performed on wafer lot of for the manufacturing of BHA guaranteed is.

#### oelectronics die flow.

the Engineering Model Quality 1), whether they are QML or e form come from a qualified th a CoC. The EMs are not reening or testing. ST space FM duct's SMD (they are SMD die he FM parts follow the Die lity Specification (TN0873)[1]. sists of a visual die sort that OID Condition A for QML-V die.

Table 1 summarizes the EM

#### ctronics EM and FM die.

such as burn-in or 100%

3

high- and/or low-temperature test at electrical wafer sort (EWS), commonly referred to as KGD. ST's QML-V products are proposed in die form only when it can be agreed with DLA that an EWS at 25°C plus a wafer lot qualification test on 25 pieces at -55°C, +25°C and +125°C is sufficient to make the packaged die capable of meeting the electrical performance requirements of the SMD.

TI offers a wide variety of products in die form. TI defines KGD as "die tested to the same quality and reliability standards as their packaged equivalents" [2]. Figure 5 shows TI's die parts categories.

#### Die Sales

Class Q and Class V Known Good Die - die fabricated, tested, and qualified in compliance with ML-PRF-38535 QML Class Q or Class V and specified in a Standard Microcircuit Drawing (SMD). RNA is available.

Military and Space Grade Tested Die – Tested Die fabricated on a ML-PRF-38535 certified manufacturing line and tested for DC and functional performance only at ambient temperature. Legacy

Known Good Die (KGD) – commercial grade die specified for full performance over a specified temperature range.

Commercial Tested Die (TD) – commercial grade die tested for DC and functione performance only at ambient temperature. Figure 5. Texas Instruments die categories.

An example flow of a OML-V die is shown in Figure 6.

Figure 6. Texas Instruments example QML-V die flow.

TI's datapack available for QML die includes the data for Group C, wafer lot acceptance (Class V only), and Group E (radiation-hardness-assured only). However, the attributes (yield) and variables (read and record) are not available. TI does not offer catalog burned-in die at this time. TI does perform testing at multiprobe–for example, VBOX, GOI, and IDDQ—to ensure quality of the die. Wafer fabrication includes engineering parametric testing (test structures), wafer-level reliability testing (WLR), and outlier controls. During feasibility studies, a candidate for die sale is evaluated for packaged-device electrical-yield performance and operational life without burn-in. If either is deemed unsuitable, the device will not be released in die sale.

## **Texas Instruments (TI)**

NEPAG

#### Commercial/Automotive Flow Space EP Flow One Wafer Wafer Wafer Wafer Wafer Fab EU Fab US Fab CH Fab JP Fab One A/T Site A/T Site A/T Site A/T Site A/T Site Malay Thai Taiwan CH One Material Material Material Material Material Set Set Set Set Set Commercial product builds = multiple FABs, A/T EP product build = one FAB, one sites and may use various material sets A/T site, and one material set

#### **Space EP Baseline** Controlled Flow

Image Courtesy of Texas Instruments

- The above chart provided by TI shows that their commercial/automotive products maybe built at multiple foundries, assembly/test facilities and may use various material sets.

- Contact manufacturer for a current version of this chart.

25

# http://nepp.nasa.gov

# NEPAG

#### ACKNOWLEDGMENTS

The research described in this publication was carried out, in part, at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. Help is gratefully acknowledged from Mohammad Mojjaradi, Jeremy Bonnell, Rowan Swain and Joon Park. Government sponsorship acknowledged.