### 2.5/3D-Level Packaging Technology Materials, Assembly Process, and Reliability Challenges for Space Applications

Eric Jong-ook Suh, Ph.D. Joseph Riendeau, Ph.D.

Jet Propulsion Laboratory, California Institute of Technology

NASA Electronic Parts and Packaging Program (NEPP) 2022 Annual NEPP Electronic Technology Workshop (ETW) June 14, 2022

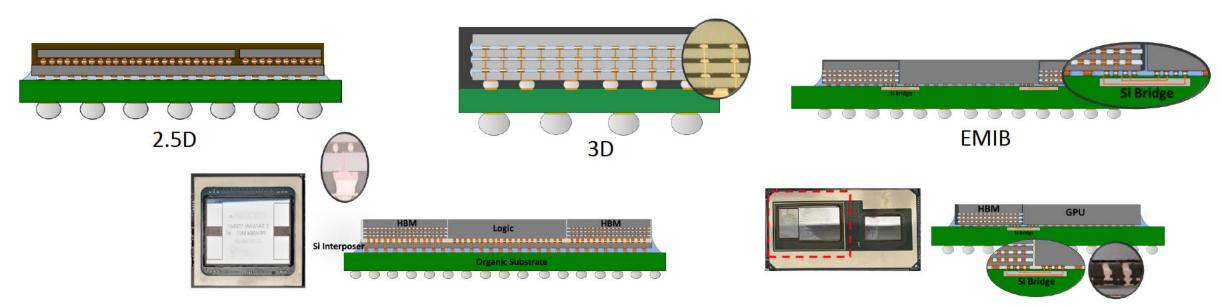

# 2.5/3D / Heterogenous Integration Packaging

- Integrate multiple dies at the package level

- $\circ~$  Integrate pieces of a large die and enhance die yield

- Heterogenous integration

- Disparate semiconductor technologies.

- $\circ$  Integrate IP blocks or functions difficult to build on the same chip

- Avoid redesigning entire chip for advanced node

- Quicker development for SoC

- Interconnection

- Lateral : Line & IO density greater than organic substrate.

- Vertical : TSV

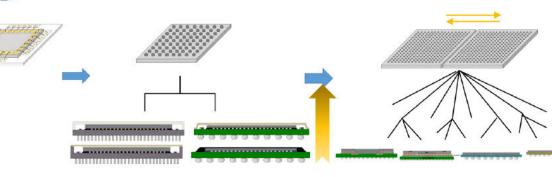

# No Industry Common Packaging Architectures

More technology building blocks (manufacturing technologies and materials) • Packaging technology (CSP, WLP, coreless substrate, embedded component, etc) • Evolution in other technologies that can be leveraged (flat panel display, MEMS, etc)

| Name            | Stands for                                     | Description                                       | Company       |

|-----------------|------------------------------------------------|---------------------------------------------------|---------------|

| CoWoS           | Chip-on-Wafer-on-Substrate                     | Si Interposer                                     | TSMC          |

| EMIB            | Embedded Multi-die Interconnect Bridge         | Si Bridge                                         | Intel         |

| FOCoS           | Fan-Out Chip on Substrate                      | Fan-out                                           | ASE           |

| FO-EB           | Fan-Out Embedded Bridge                        | Fan-out                                           | SPIL          |

| FO-MCM          | Fan-Out Multi-Chip Module                      | Fan-out                                           | SPIL          |

| Foveros         |                                                | Heterogenous 3D dies connected with EMIB          | Intel         |

| Glass Substrate | 4                                              | Line & via built on glass core                    | Absolics (SKC |

| InFO            | InFO (Integrated Fan-Out)                      | Fan-out                                           | TMSC          |

| RDL Interposer  | Redistribution Layer Interposer                | Bare RDL as interposer                            | Samsung       |

| SLIM            | Silicon-Less Integrated Module                 | BEOL layer as substrate                           | Amkor         |

| SolC            | System on Integrated Chip                      | Heterogenous 3D dies connected with Si interposer | TSMC          |

| SWIFT           | Silicon Wafer Integrated Fan-out<br>Technology | Fan-out                                           | Amkor         |

BEOL

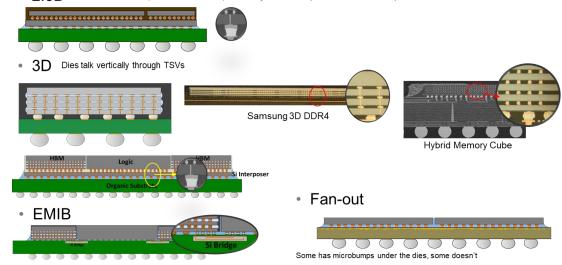

#### • 2.5/3D / heterogenous integration packaging

- Unlike previous generations of packaging technology:

- No industry common architecture.

- Each architecture is offered by only about 1~2 companies

- Same or similar packaging architecture can have different assembly process flow and materials

- New packaging architectures are constantly being introduced.

- Often it is not clear if they are ready for production.

- Existing architectures also evolve or discontinue

- Technology seems to evolve faster over time

- A Mil-spec working group exists.

- No industry common architecture

- $\circ~$  Are there common features or materials?

- What are the ones within our capability to study?

- What are the aspects relevant to mil/space component?

- Difficult to obtain samples. Need to understand SoA industry practice better.

- Partnered with GaTech

| Name            | Stands for                                     | Description                                       | Company        |

|-----------------|------------------------------------------------|---------------------------------------------------|----------------|

| CoWoS           | Chip-on-Wafer-on-Substrate                     | Si Interposer ("2.5D")                            | TSMC           |

| EMIB            | Embedded Multi-die Interconnect Bridge         | Si Bridge                                         | Intel          |

| FOCoS           | Fan-Out Chip on Substrate                      | Fan-out                                           | ASE            |

| FO-EB           | Fan-Out Embedded Bridge                        | Fan-out                                           | SPIL           |

| FO-MCM          | Fan-Out Multi-Chip Module                      | Fan-out                                           | SPIL           |

| Foveros         |                                                | Heterogenous 3D dies connected with EMIB          | Intel          |

| Glass Substrate |                                                | Line & via built on glass core                    | Absolics (SKC) |

| InFO            | InFO (Integrated Fan-Out)                      | Fan-out                                           | TMSC           |

| RDL Interposer  | Redistribution Layer Interposer                | RDL as interposer                                 | Samsung        |

| SLIM            | Silicon-Less Integrated Module                 | BEOL layer as substrate                           | Amkor          |

| SolC            | System on Integrated Chip                      | Heterogenous 3D dies connected with Si interposer | TSMC           |

| SWIFT           | Silicon Wafer Integrated Fan-out<br>Technology | Fan-out                                           | Amkor          |

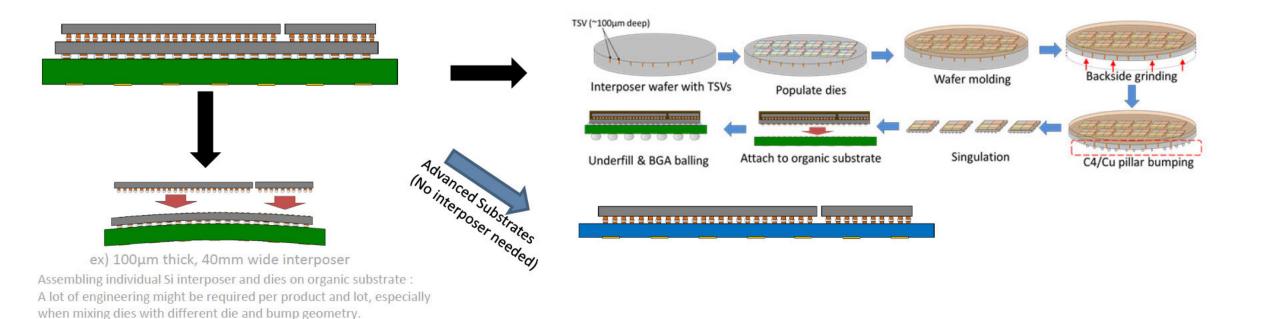

2.5D Inactive silicon interposer with TSVs to provide high line density between dies laterally

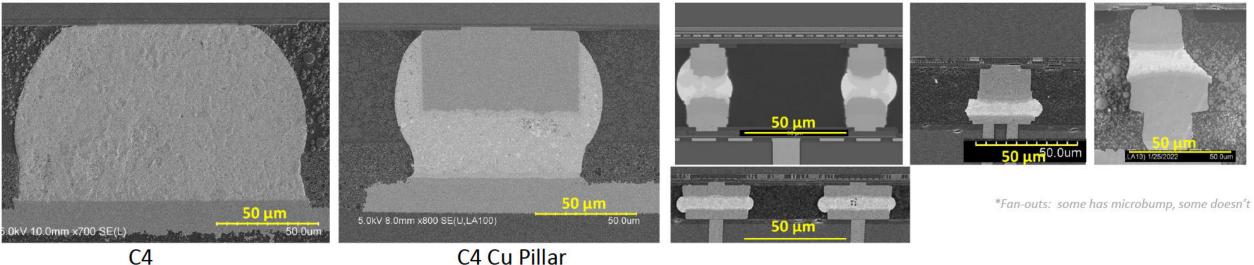

C4 Cu Pillar

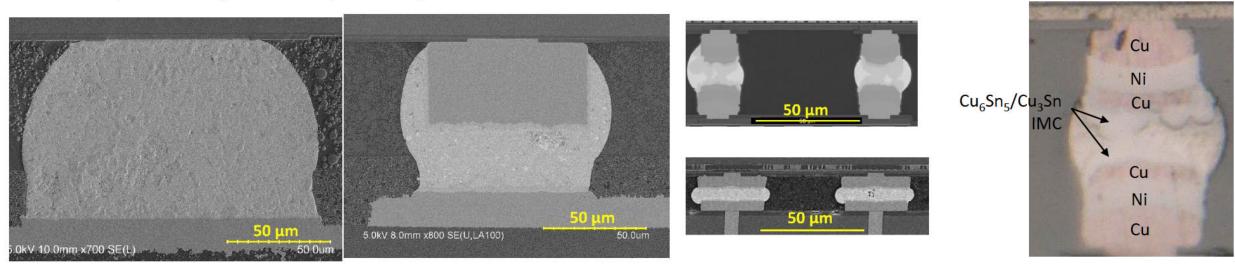

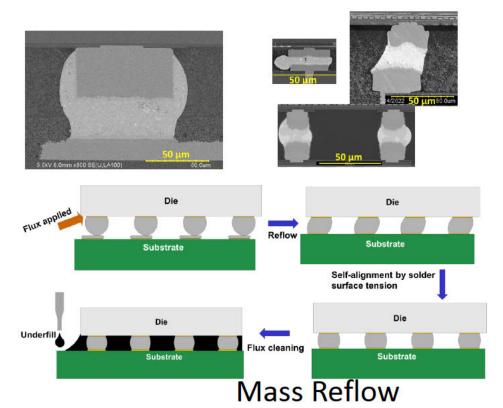

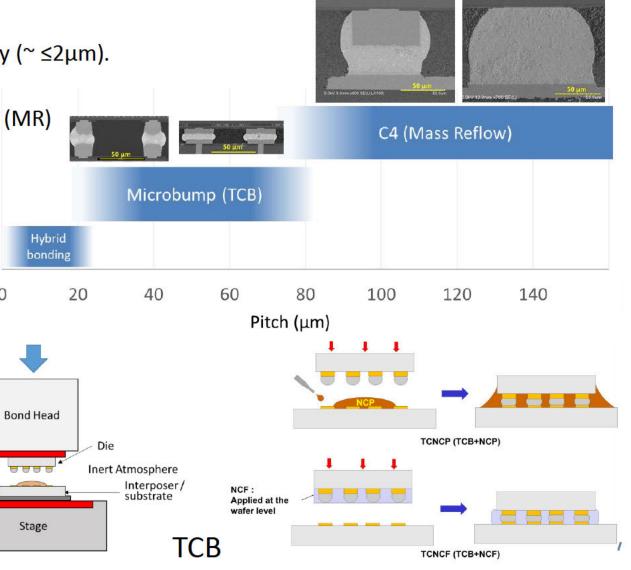

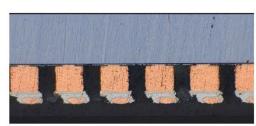

Microbumps are different from existing C4 bumps Metallurgy • Assembly process C4 (Mass Reflow)

GPU

Microbump (TCB)

60

80

Pitch (µm)

100

120

140

40

bonding

20

HBM Si Interposer

- Pb-free : This is now a reality we have to accept.

- Small solder volume

- Effects of Sn consumption during reflow and thermal aging.

- Increased volume fraction intermetallic compound (IMC) in solder joint.

- Not the main focus of current NEPP task

- The field has a long history

- Recent updates in the subject and trends will be reviewed.

- Examples of industry solutions

- Solder composition optimization

- Control of Ag<sub>3</sub>Sn precipitate morphology and amount

- Liquidus temperature less impacted by Sn consumption

- o Column/bump pad metallurgy optimization

- Limit the growth of IMC. Control the growth of less preferred type of IMC.

- Potential overtesting

- Depending on the package design, it is possible to demonstrate accelerated failure by promoting diffusion.

ex) HTS → TC or long dwell at hot temperature during TC

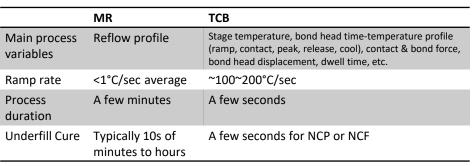

### **Microbump Assembly Process**

- Thermocompression bonding (TCB)

- Temperature & force

- Die can't self align by solder surface tension •

- Down to ~20 $\mu$ m pitch with greater die placement accuracy (~  $\leq 2\mu$ m). •

0

Heater

- Can better accommodate thinned dies. •

- Far greater number of process variables than mass reflow (MR) •

- Process duration is only a few seconds •

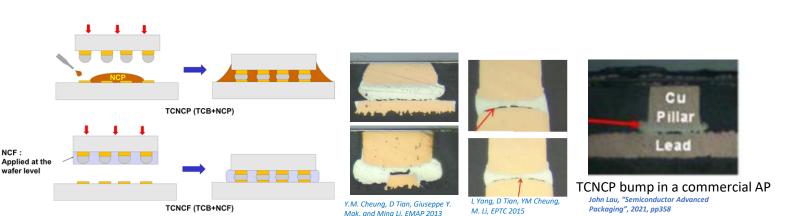

## **Thermocompression Bonding Process**

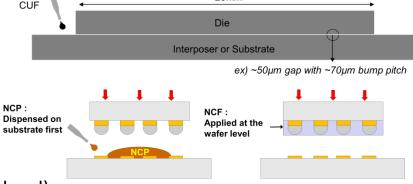

- TCB process & materials

- More sophisticated than traditional mass reflow Ο

- Underfill challenges Ο

- Capillary underfill (CUF)

- Increased voiding issue

- Difficulty begins at ~100µm pitch, increasing as pitch approaches 50µm.

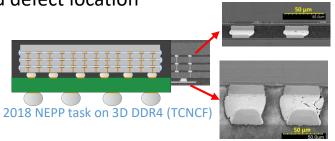

- Non-conductive paste (NCP) : Defects

- Non-conductive film (NCF) : Defects, Die shelf life (B-stage material applied at wafer level)

- Defects during NCP / NCF attach. Ο

- Low-volume manufacturers can have difficulty in optimizing assembly process

- Defects can't be detected by typical NDT

- Defects may pass 38535 screening condition but cause early failure, depending on design and defect location

- NEPP focus

- TCNCP bump reliability and screening. Ο

- Also microbumps with CUF

25mm

Flux cleaning &

NCP :

# NEPP & GaTech Collaboration

- Challenges in defining NEPP task for 2.5/3D level-packaging

- No industry common architecture

- Focus the scope to thermocompression bonded microbumps

- TCB process & materials

- Difficult to obtain sample

- Assembly process and materials are far more sophisticated than previous technologies

Need better visibility on how the samples are built, learn practical issues during manufacturing.

- o Need expert consultation to quickly identify industry common SoA practice

- GaTech Packaging Research Center consortium

- International consortium

- R&D scale SoA prototyping capability with visiting engineers from industry

- Connection to packaging, equipment, and materials companies through international consortium

- GaTech Packaging Research Center's current focus is on glass substrate technology

- o ex) Heterogenous integration on glass substrate, RF, embedded component, photonics, ≤1 or ≤1.5 µm line width/spacing

- o There are companies (ex: SKC) about to release glass substrates to the market.

- GaTech professors : Suresh Sitaraman and Vanessa Smet

# Advanced Substrates and Space Component

- Supply chain issue for mil/space component business

- Actual issue according to industry people

- Low-volume, high mix applications

- Advanced substrates can enable production in-house or at average size packaging companies

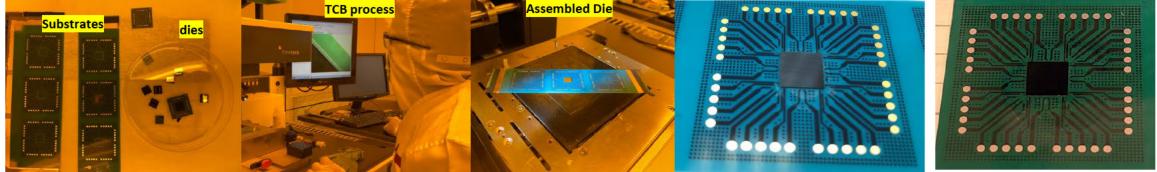

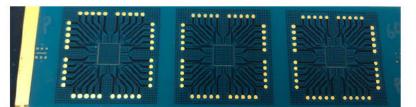

### Current NEPP Task Scope

- Study quality and reliability of 2.5/3D-level packaging, in focus of microbump interconnection and underfill.

- Impact of materials and assembly process

- Learn commercial industry common SoA practice and issues

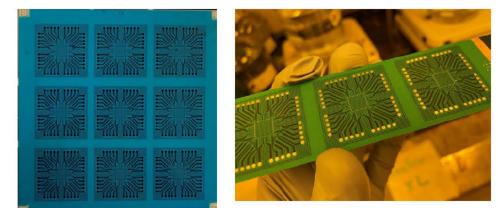

- Design and build test articles

- Interconnections representative of actual 2.5/3D-level packages

- o Learn practical challenges in package assembly

- GaTech to share detailed progress in process optimization during sample manufacturing

- Reliability study

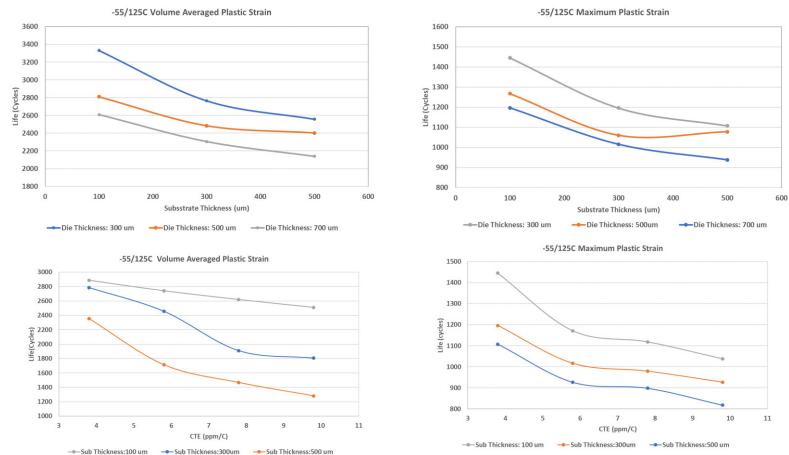

- $\circ$   $\,$  Perform reliability tests and FEA  $\,$

- Study dominant failure mechanism

- Depends on design, material, & process.

- Useful in developing/reviewing PIDTP.

- How things fail eventually, what happens if design or material changes

- Longer term goals

- How should PIDTP be structured?

- Screening? Lot qual?

- Defects passing 38535 screening condition but causing early failure

Underfill crack/delamination

Solder joint fatigue

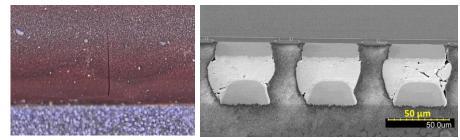

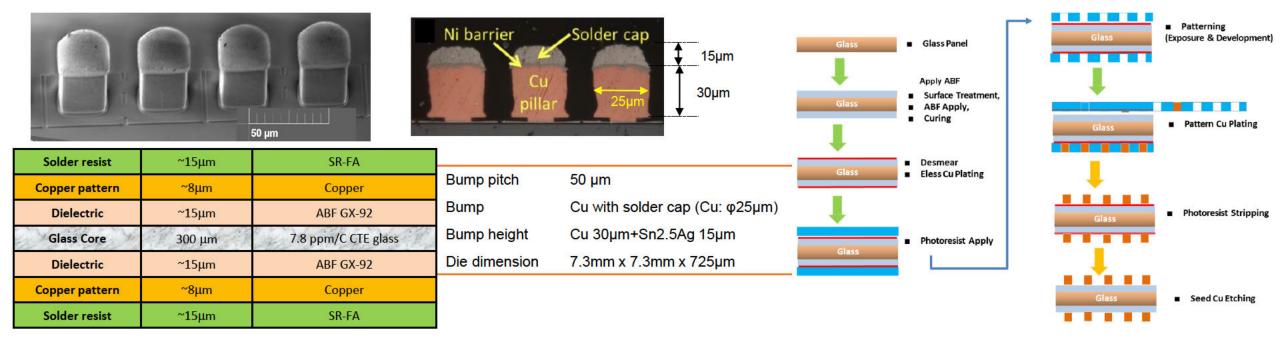

- 50µm pitch Sn2.5Ag bump

- Glass substrate

- Glass core

- ENEPIG finish for the current phase. 50-100nm Pd, 50nm Au

- Fabricated at GaTech

- Industry production substrate in upcoming phases

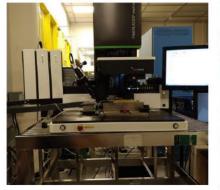

Sub-micron Flip-chip Bonder (Finetech)

Semi-Automatic Flip Chip Bonder (Finetech)

APAMA C2S (K&S)

..........

- Non-linear analysis with solder viscoplastic behavior and hysteresis.

- Assembly process cycles and IMC growth are also factored in.

- Effects on design parameters on temperature cycling life were modeled.

- -55/125°C temperature cycling

- Humidity temperature bias or autoclave

- THB : 130°C/85%RH or 85°C/85%RH

- Autoclave : 121°C, 2atm

- Failure analysis

- Projected duration of test & failure analysis is 3.5 months.

- The current NEPP task focuses:

- Reliability of microbump interconnection and underfill in 2.5/3D-level packaging.

- Advanced substrate technologies are a viable option for low-volume, high mix application.

- The initial sets of samples are manufactured.

- Reliability tests and failure analysis will follow.

Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the United States government or the Jet Propulsion Laboratory, California Institute of Technology.