# **GlobalFoundries**

# **GF Foundry 101** June 16, 2022 Jeremy Nuldavin

Outline

- **1. Background**

- 2. Foundry Overview

- **3. Customer Focus**

- 4. Foundry Focus

- 5. Summary & Questions

# Background

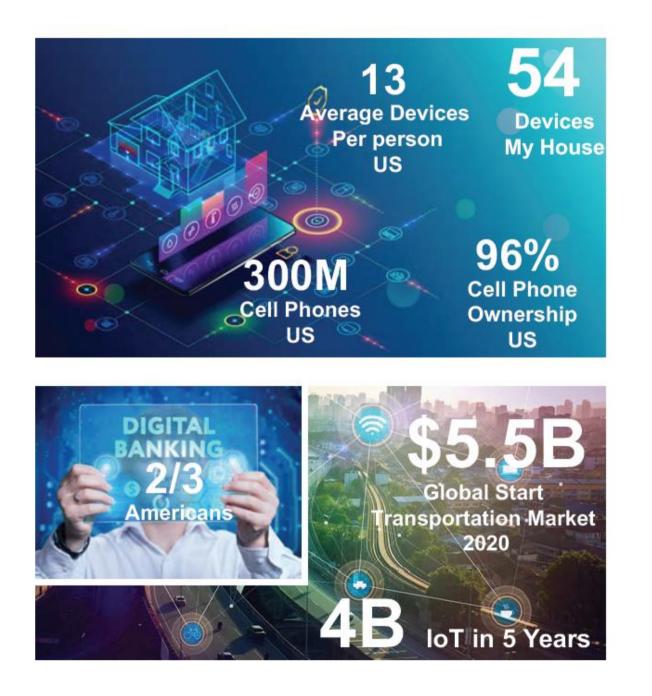

# We live in a world that is **connected**

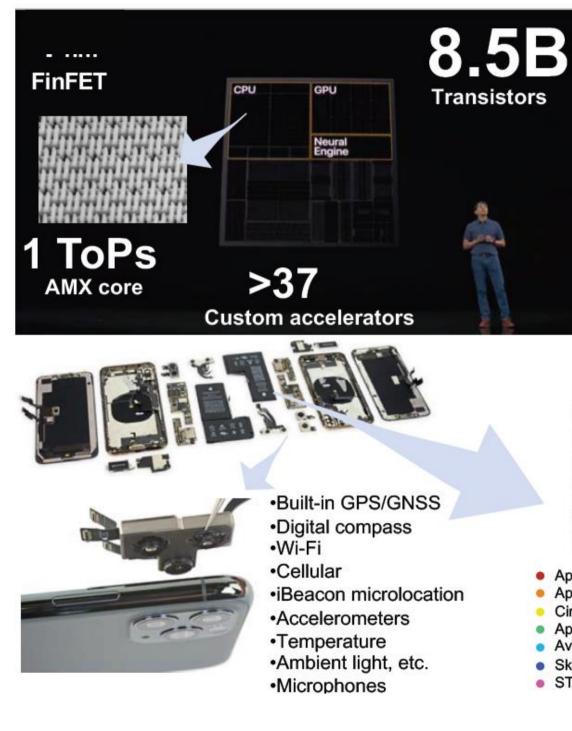

# The technology we rely upon is **complex**

- Apple APL1W85 A13 Bionic SoC + SK Hynix LPDDR4X

- Apple APL1092 343S00355 PMIC

- Cirrus Logic 338S00509 audio codec

- Apple USI module—U1 ultra-wideband

- Avago 8100 Mid/High band PAMiD

- Skyworks 78221-17 low-band PAMiD

- STMicrolectronics STB601A0N power management IC

- Apple/USI 339S00648 WiFi/Bluetooth SoC

- Intel X927YD2Q modem

- Intel 5765 P10 A15 08B13 H1925 transceiver

- Skyworks 78223-17 PAM

- 81013 Qorvo Envelope Tracking

- Skyworks 13797-19 DRx

- Intel 6840 P10 409 H1924 baseband PMIC

GlobalFoundries © 2021 All Rights Reserved 3

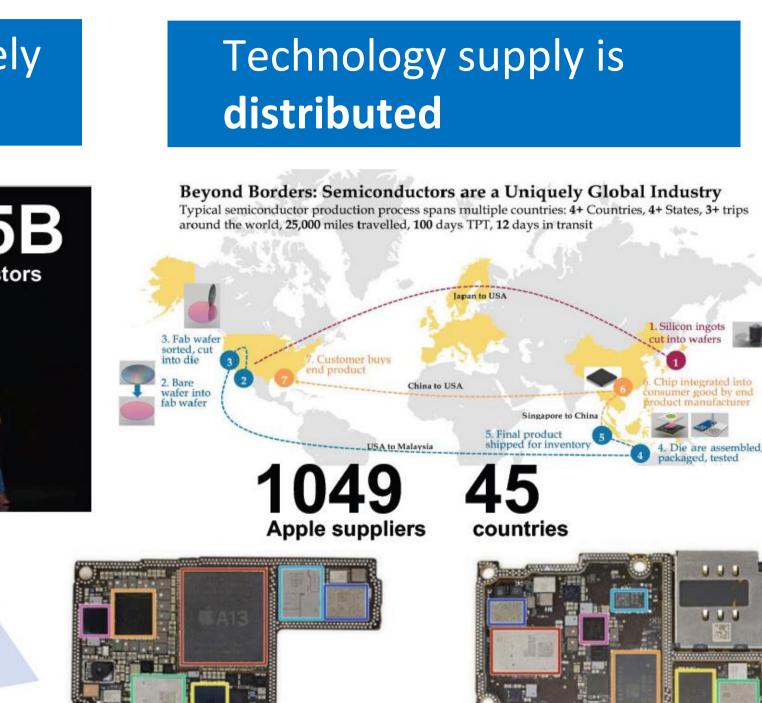

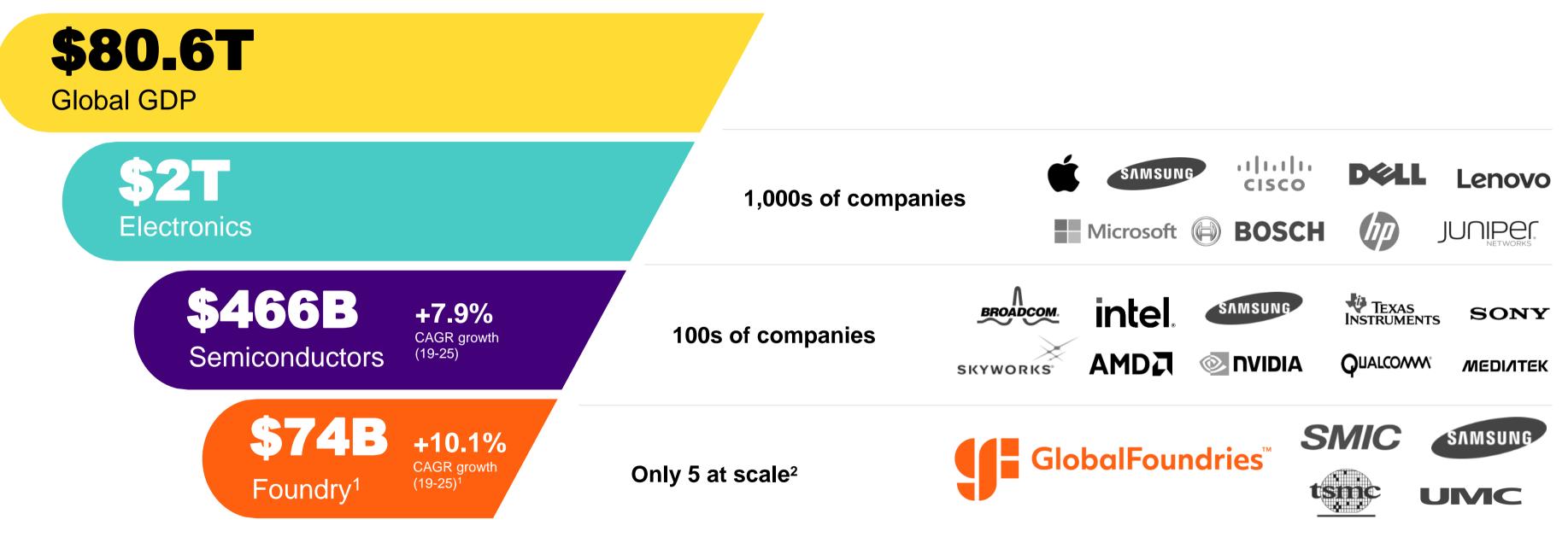

# Foundries are essential to global GDP

Market Size (2020)

Source: Derived from Gartner data. Gartner Forecast, Semiconductor Foundry Revenue Supply and Demand Worldwide 2Q21 Update, July 2021 Notes:

(1) Excluding memory.

(2) Excludes smaller foundry players, defined as those with less than \$2Bn of foundry revenue

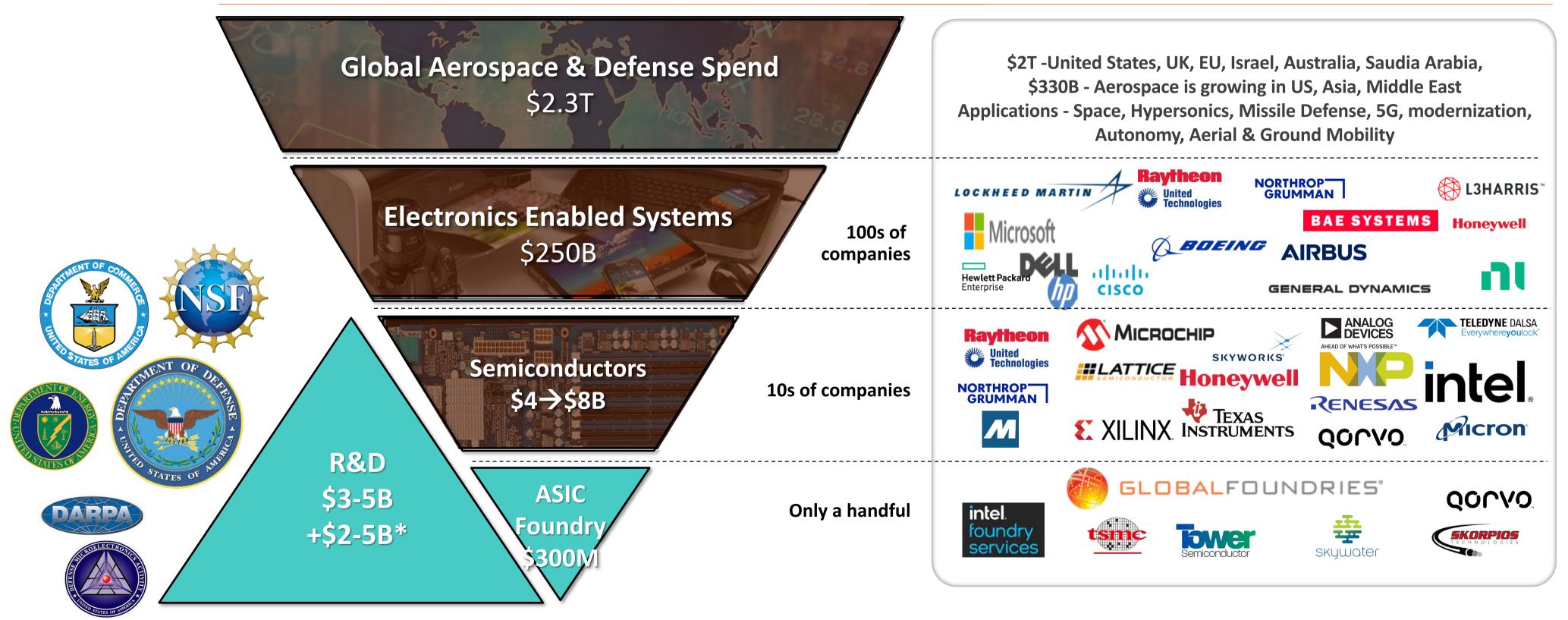

# A handful of silicon foundries underpin the A&D semiconductor and electronics industry

Market size (2022)

Source : Based on GF Internal Analysis

## **Representative participants**

# **Our View of US Needs**

## **Commercial Foundation**

- Advanced Technology is needed across all production nodes for dual use

- GlobalFoundries is ideally suited to build an onshore capability and **capacity** to increase market share

- Commercial volume is necessary to sustain the IP, foundry, and packaging ecosystem and requires market incentives

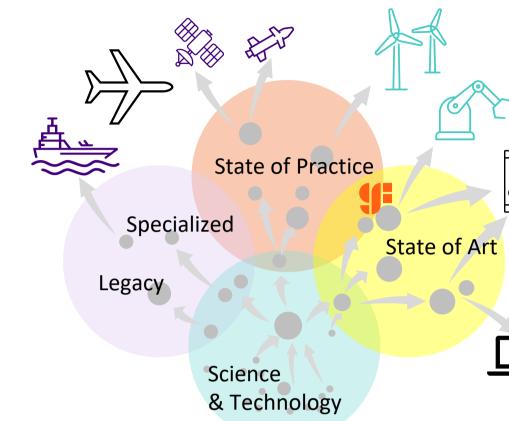

# Technology to Capability

- To address national interests R&D must enable production in the US for critical needs

- R&D must leverage US foundry backbone of production to capabilities for critical markets and national security

- Without the laws and incentives to capture R&D in the US our adversaries will be the first to benefit

## **Un-Level Playing Field**

- Cost of building, equipment, labor, and development are being **subsidized** heavily by Asia and Europe

- USG has a chance to change where R&D is ramped to production

- The USG must have agile and potent tools to incentivize domestic R&D capture and transition to production in with strong market preferences

Outline

- 1. Background

- **2. Foundry Overview**

- **3. Customer Focus**

- 4. Foundry Focus

- 5. Summary & Questions

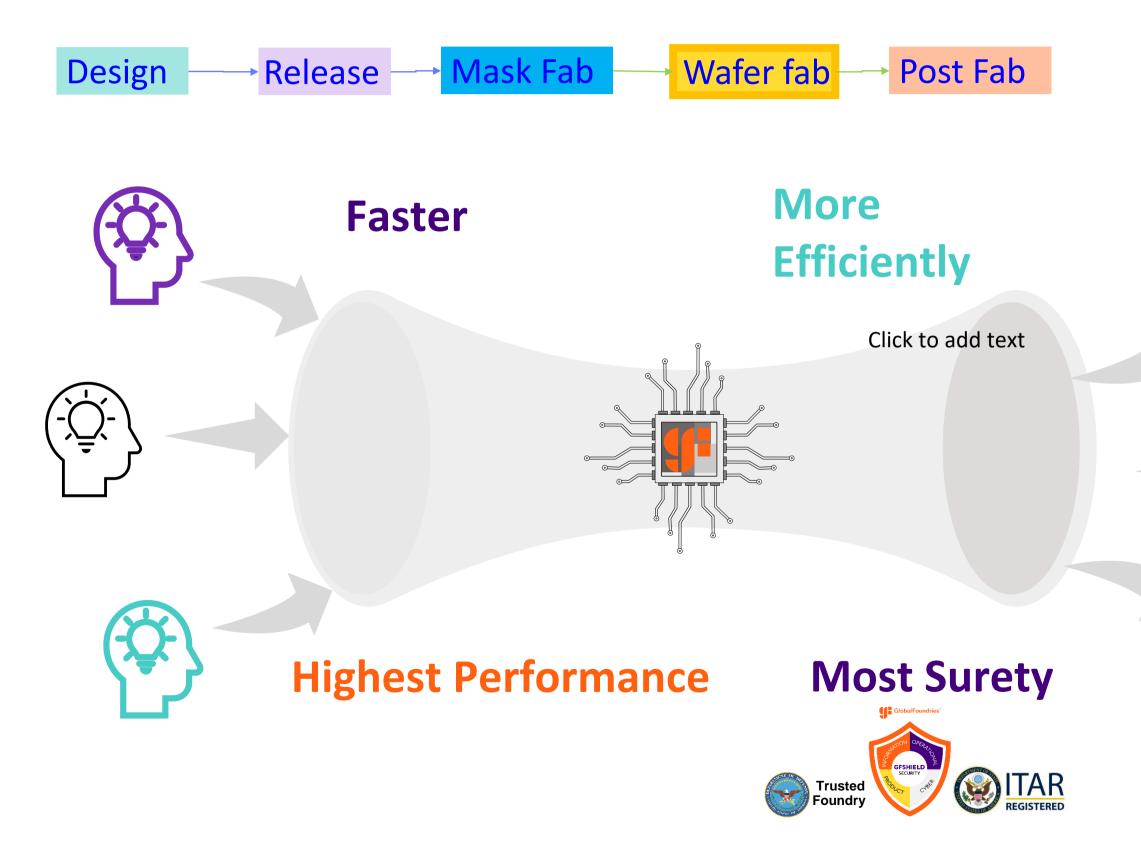

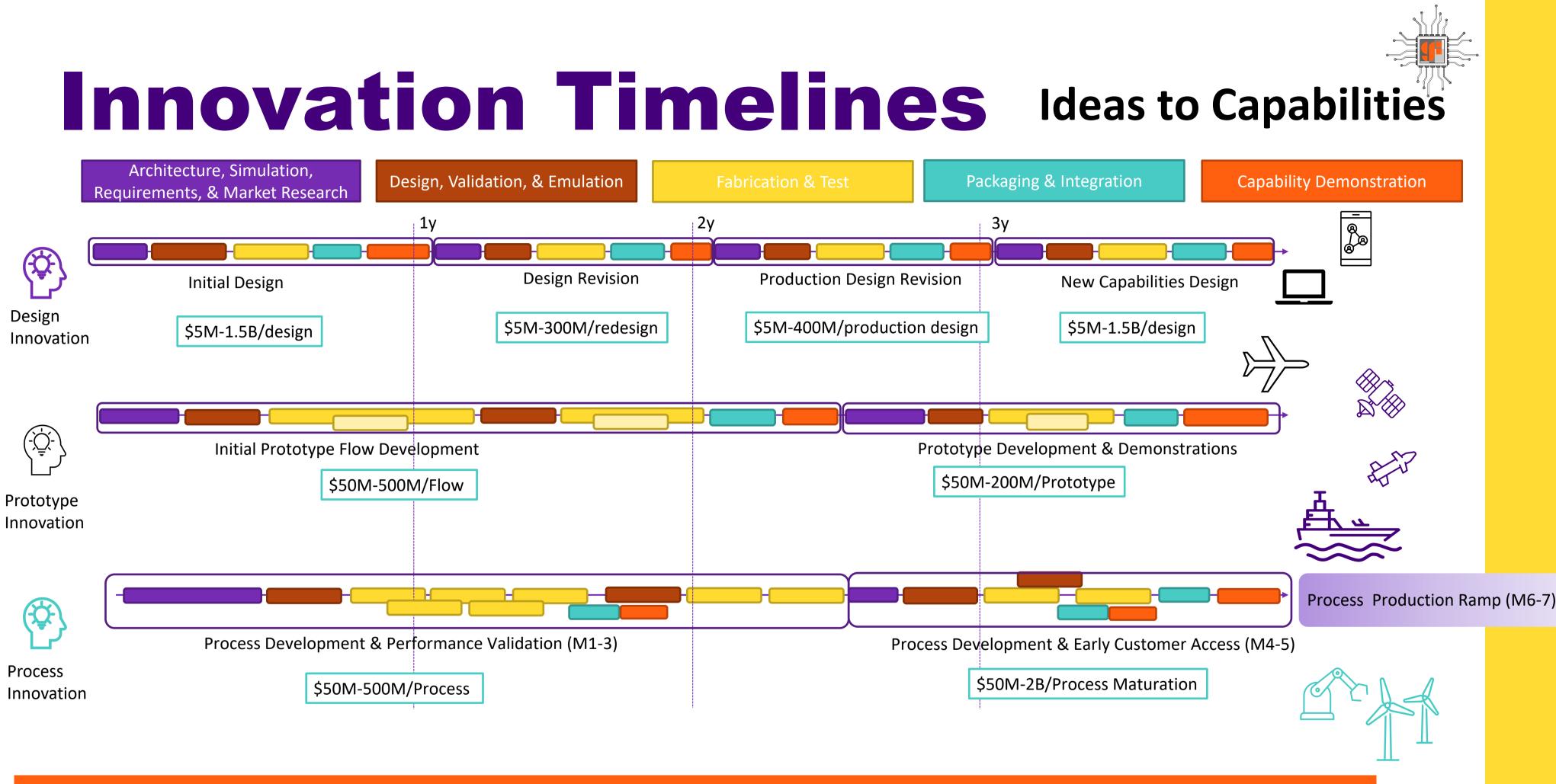

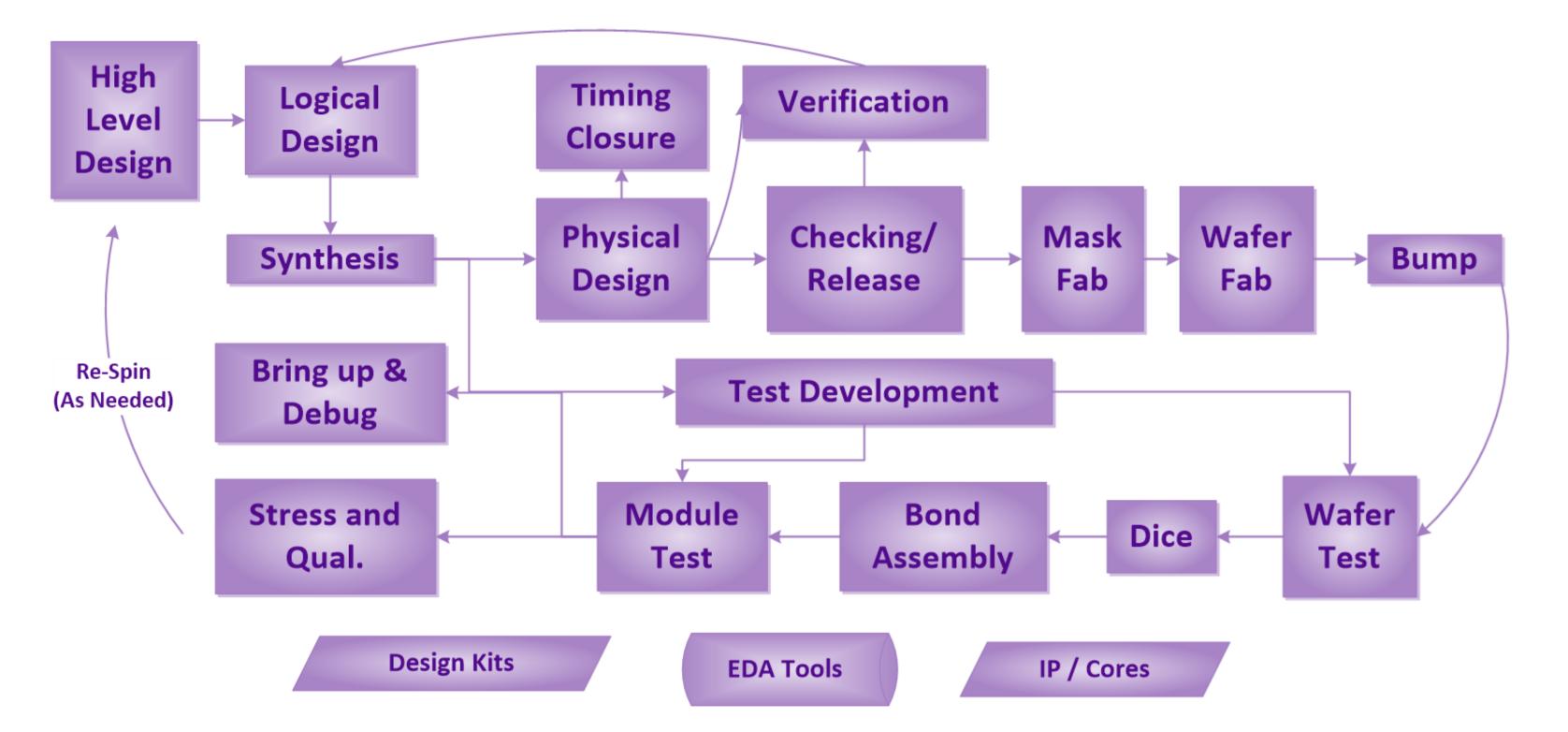

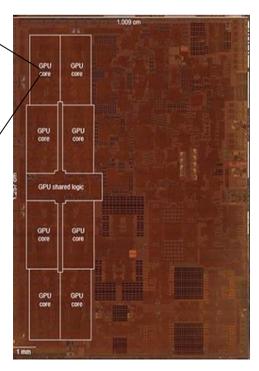

# Ideas to Capabilities

Foundry is the critical core and enabler for rapid innovation

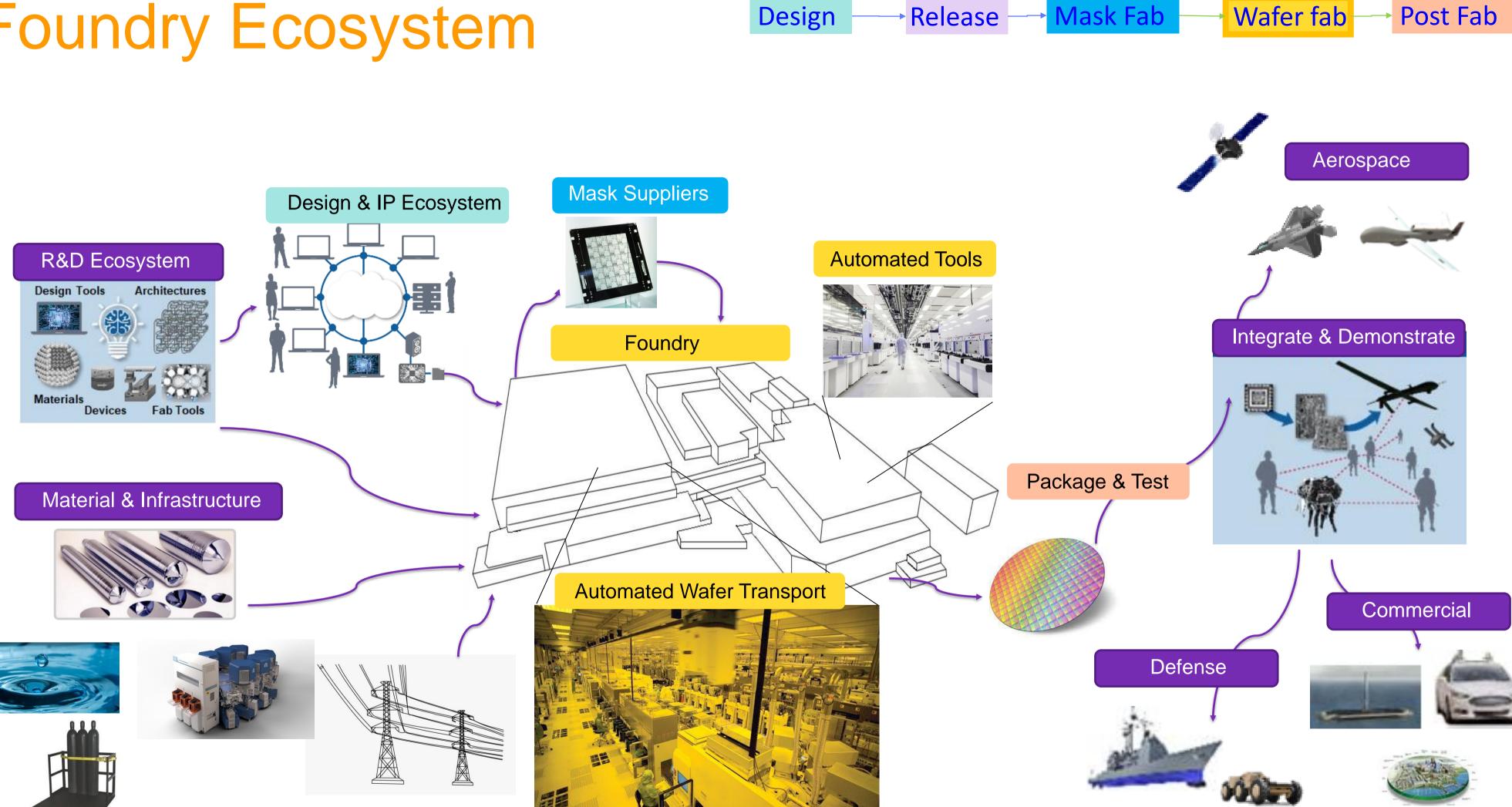

# Foundry Ecosystem

Sourced from across the internet

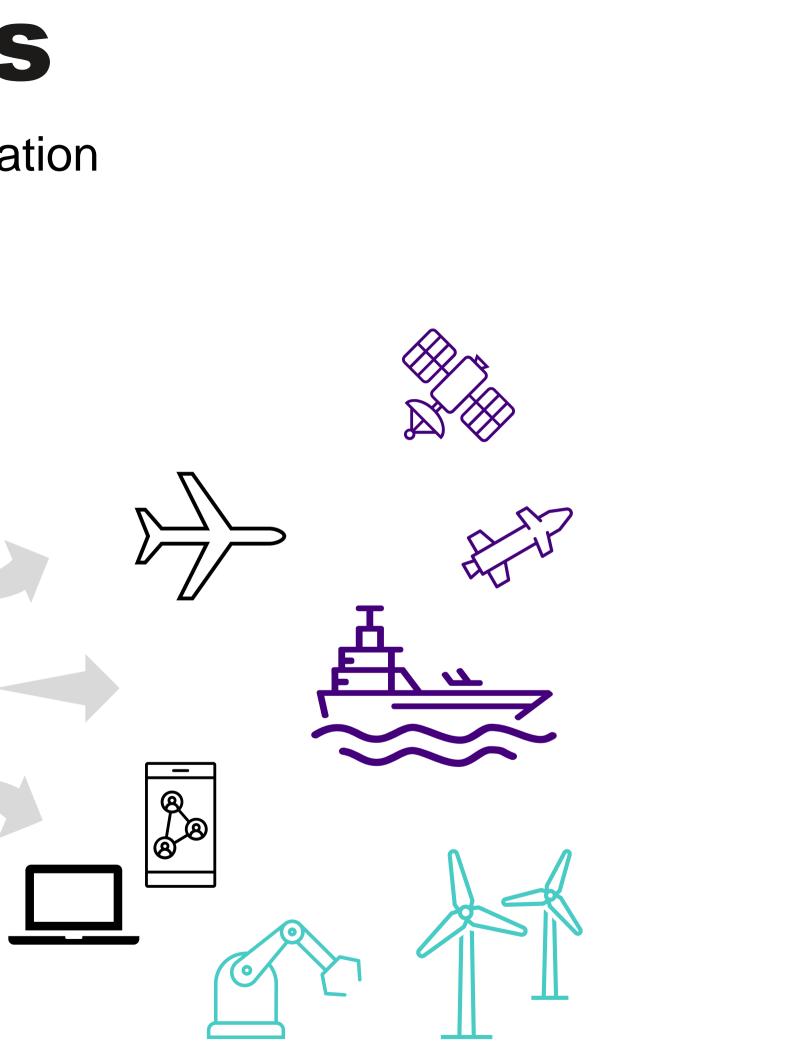

# **Foundries Deliver Capabilities**

## **Offer to Customer**

- Variety of Advanced Technology

- Device & Chip **Performance and** reliability data and IP Ecosystem

- Rules for Design and construction of Chips (PDK)

- **Time until 1<sup>st</sup> Product** in hand when designs received

- Cost and Speed of Production

- **Support** for design in our technology

## **Designs to Masks**

- **Receive and validate** customer designs

- **Confirm it meets Design Rules** for manufacturing

- **Refine shapes** to match our tooling (OPC)

- Make the Masks (chrome lines on glass) or send validated data to mask house

## Masks to Wafers

- **Receive Maskset** from mask house

- Identify materials and process steps

- Do Processing Steps as outlined in the PDK (litho, etch, clean...)

- **Do Inspection** Steps to ensure yield and performance

- Finish wafer processing and test to validate yield and performance

- Slice wafers into Die, and package for sale / mounting to circuit boards **GlobalFoundries** © 2021 All Rights Reserved

# GlobalFoundries<sup>™</sup>

# Delivering a new era of more

# more innovation

# more impact

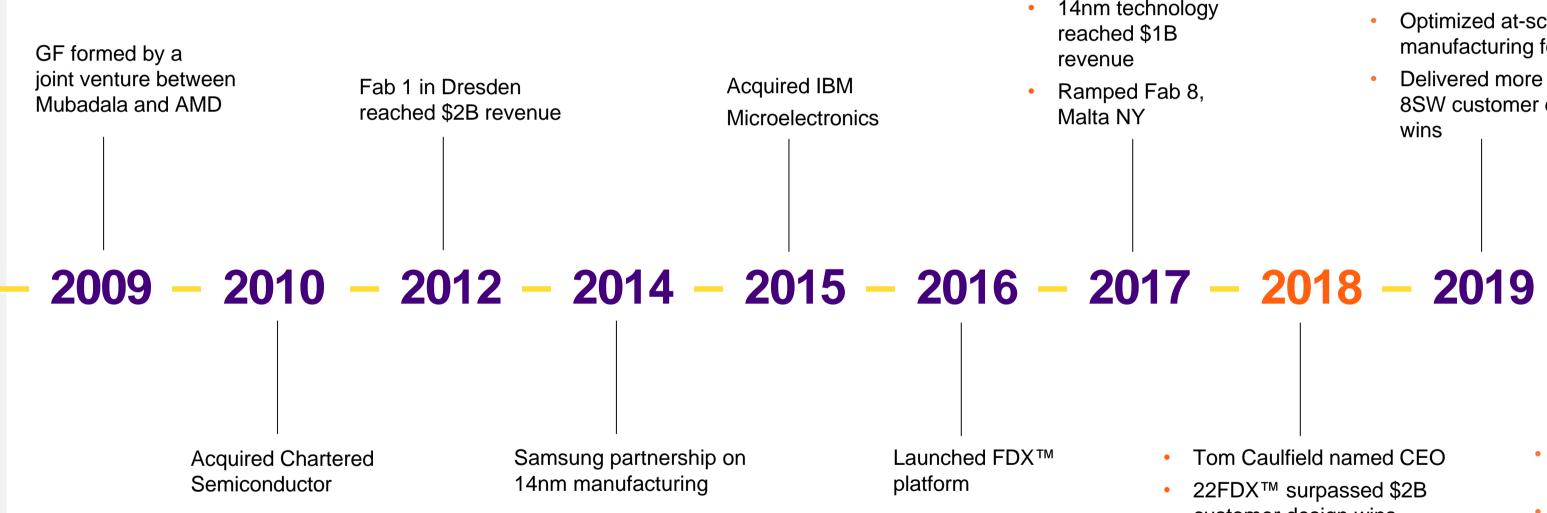

# The making of a global semiconductor manufacturer

- 14nm technology reached \$1B revenue

- Ramped Fab 8, Malta NY

- Carved out and sold ASIC business

- Optimized at-scale global manufacturing footprint

- Delivered more than \$1B 8SW customer design wins

- Moved HQ to New York

- Broke ground on new fab in Singapore

- Announced maior auto collaborations

- Fab 8 expansion announced

- GF IPO

2021 2020

- Tom Caulfield named CEO

- 22FDX<sup>™</sup> surpassed \$2B customer design wins

- Strategic reposition to feature-rich solutions

- Shipped record number of wafers

- Zero operational disruptions

- GF Shield launched

# **Global Manufacturing Footprint**

Notes:

\*In Process

(1) Kwpa is defined as at-four-walls thousand wafers per annum.

#### Singapore Fab 7 / GIGA+

Wafer size: 300 & 200mm Capacity: 720 & 720 kwpa Technology: BCD/BCDLite<sup>®</sup>, HV, NVM, DDI, RF SOI, LP SiGe

~4.000 employees

....

....

....

....

... ......

.. .........

...

....

\*\*\*\*\*\*\*\*

\*\*\*\*

.....

....

. .

...

....

... ...

. .

... .... ....

.....

#### Singapore Fab 7h- New Fab 2023

Wafer size: 300mm Capacity: 450 kwpa Technology: BCD/BCDLite<sup>®</sup>, NVM, DDI, RF SOI

#### ~ 800 employees

#### **Dresden, Germany** Fab 1

Wafer size: 300mm Capacity: 850 kwpa Technology: FDX™, NVM, HV, BCDLite<sup>®</sup>

~3,000 employees

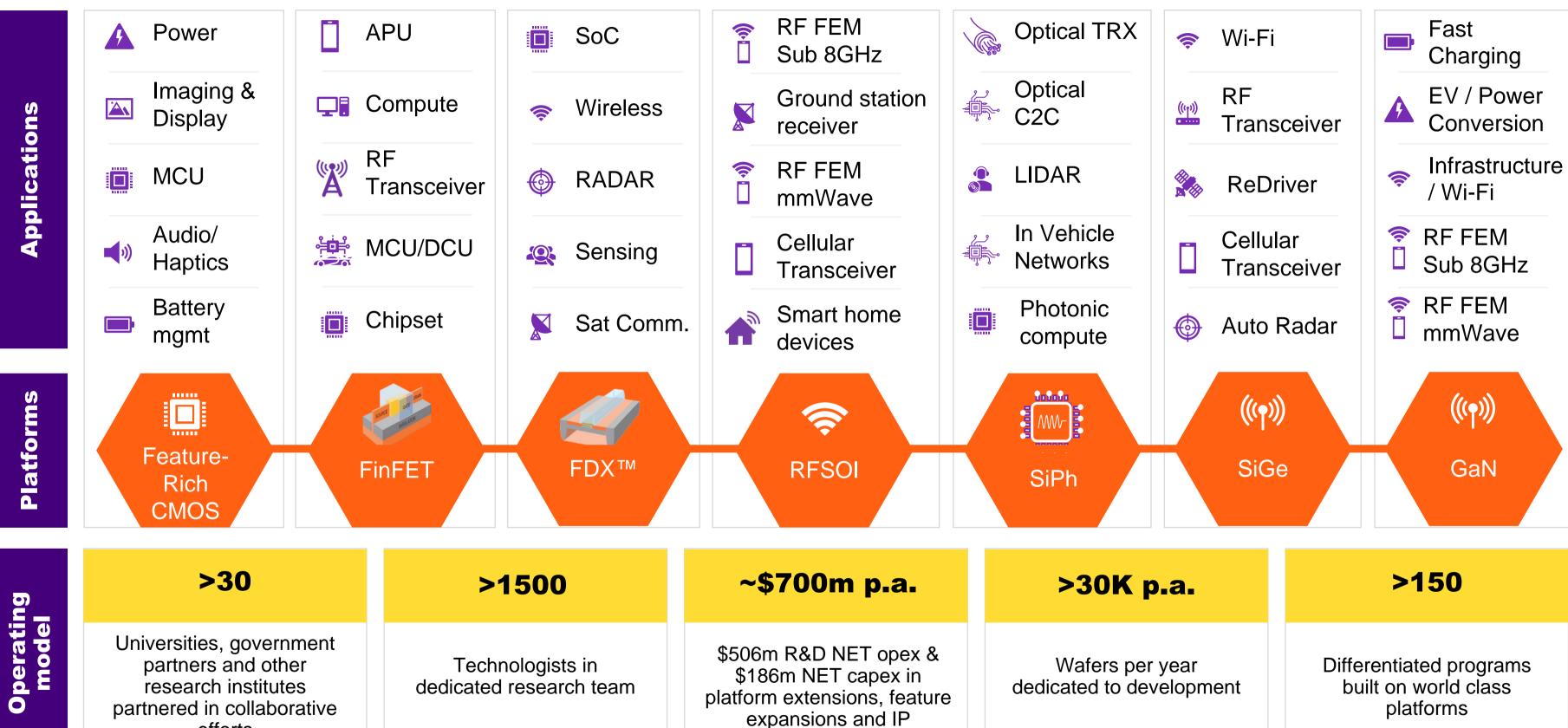

# How we innovate: market-centric approach to technology solutions

| Market<br>requirements |                                    | Technology<br>requirements |

|------------------------|------------------------------------|----------------------------|

|                        | Smart Mobile<br>Devices            | Device performance         |

|                        | Personal                           | Power efficiency           |

|                        | Computing                          | Low latency                |

|                        | Communications<br>Infrastructure & | RF connectivity            |

|                        | Datacenter                         | Security elements          |

|                        | Home and<br>Industrial IoT         | Reliability                |

| 9 <u>;</u> 9           |                                    | Application-enabling IP    |

|                        | Automotive                         | Extreme environments       |

# GF Technology solutions

## **Platform**

Transistor targets, ULP Operating voltage

## **Features**

RF & mmWave Embedded memory Automotive grade BCD, HV

## **IP / Enablement**

Foundation IP Complex / application IP PDK

# **Differentiated technology platforms**

#### **Feature-Rich** CMOS

Complementary Metal-Oxide Semiconductor

**Mixed-Technologies** for Power Management, High-Voltage, **Embedded Memory**

>3 billion high-end audio amp units (BCDLite) shipped

>150K DDIC wafers shipped

**FinFET** Fin Field-Effect Transistor

**FDX**<sup>TM</sup> **Fully-Depleted** SOI

**Enabling New High-**Performance, Low-**Power Applications**

Supports two of top three 5G mmWave FEM design companies

| - |  |

|---|--|

|   |  |

|   |  |

|   |  |

| 0 |  |

**RF SOI** RF Silicon-on-Insulator

Low Power/Low Noise/Low Latency/High **Frequencies**

1st fully qualified highvolume RF SOI Foundry solution on 300mm wafers

**High Performance**, **Power Efficient** "Systems-on-a-Chip"

Scarce capacity – GF

one of three foundries

and adding unique

features

SiGe Silicon Germanium

SiPh Silicon Photonics

**Power Amplifier and Very High Frequency Applications**

**Higher Data Rates with Greater Power** Efficiency

Highest fmax SiGe BiCMOS foundry process in volume production at 400GHz with roadmap to 1THz

5-10x better power efficiency than long range electrical interconnect

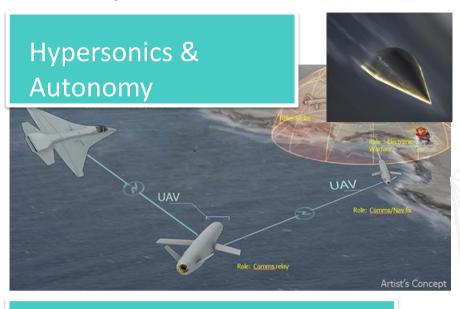

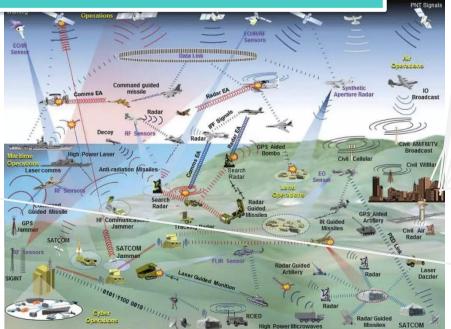

# **Strategic Market Analysis Flow (DoD)** System Needs

## Inputs

#### Robust Comms & Edge AI

### Networked EW & SigInt

Enabling Capabilities

Harsh Environment/ Space & Rad-Hard

#### RADAR and DE

Wideband Comm/ Sigint/EW

**Multi-spectral** Imagers/AI

Edge AI/ FD-PED

#### **Global PNT**

High-perf. Compute + Quantum

Trusted Fab & Packaging

**R&D** Capture and Prototyping

## Targeted **GF** Platforms Development

## 22-12FDx

45nm RF/CLO/SO

12LP+

GaN on Si +CMOS

Ge & BSI Platform

Rad-Hard Platform

eNVM Platform

Cryo/Quantum Platform

3D dense stacking for AI & Imagers

Post-fab Packaging

**HPSC RH SoC**

Edge AI SoC

**GPS SoC**

RH/eNVM SoC (NASA\DoD\NSWC)

Phased Array Platform (DARPA)

**Cryo Compute**

Smart Imaging Platform

# **GF offers a "Foundation of Trust" to build sustainable partnerships**

## **Beneficial geopolitical landscape**

During times of increasing international trade conflicts, GF benefits from the resilience of global scale of operations in stable low-risk geographies (United States, Germany and Singapore)

## Pedigree of secure at-scale manufacturing

- 1.

- ISO 15408 Certification to manufacture Common Criteria Secure Products 2.

- ISO 27001 Certification for Information Security Management 3

**Intellectual Property (IP) protection**

With an industry-leading track record protecting GF IP and customers' IP

## In a world of escalating threats and risks in the technology sector, our "Foundation of Trust" offers a strong competitive edge

Only pure-play foundry in The United States Department of Defense Trusted Foundry Program

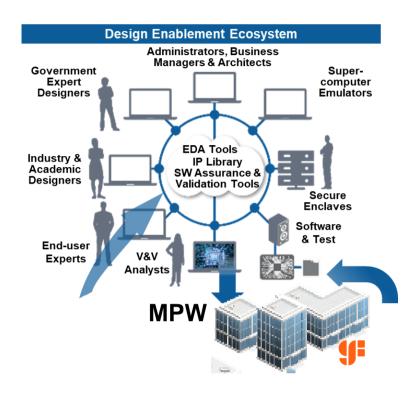

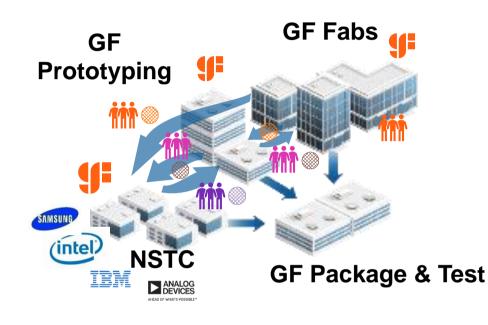

## **Design Innovation**

- Design environment with IP, EDA, Compute, PDK, emulation

- MPW guaranteed access and enablement

- Early access to developing platforms

## **Prototype Innovation**

- Partial-flow wafers for external additions

- Split-flows to allow insertion of steps into production process

- Packaging enablement for 2.5-3D integration

## **Process Innovation**

- Early access and embedded workforce to shape dual-use commercial platforms

- Process options built upon the production baseline for prototyping differentiation

- Alignment of USG R&D roadmaps with market needs and transition

## Only Process innovation delivers new production capabilities requires significant investments

#### **IMTR Roadmap Update**

efforts

# **IMTR: Integrated Market-Technology Roadmap**

platforms

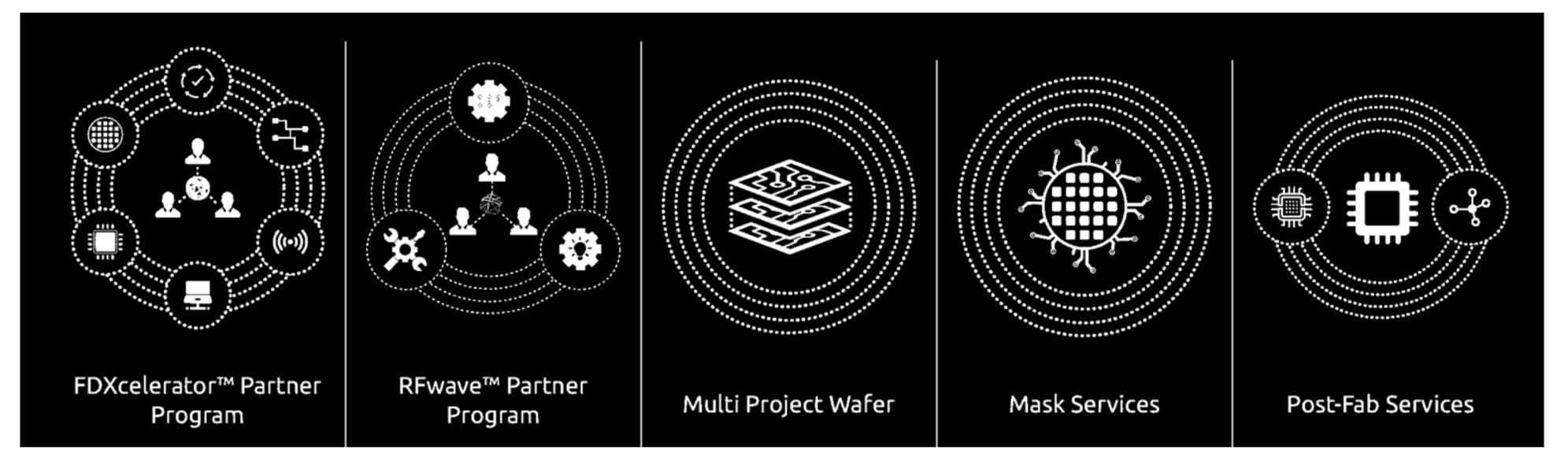

# **Active enablement and Access programs**

- Partnerships to promote and facilitate FDX adoption and R&D

- 50 service partners

- Broad IP portfolio tuned to FDX

- MPW service to lower cost and risk of production

- Partnerships to promote RF design and enablement

- >50 service partners

- Specialized RF validated IP portfolio

- MPW offerings

- MPW for early access, entrepreneurs, DIB, and academic partners

- DMEA TAPO MPW shuttles

- Commercial MPW

shuttle

- Academic Partner shuttles

- Mask prep and production onshore and offshore

- Mask prep services to 12nm

- Mask Production

Partnership onshore

- Global Mask flow for commercial

- Post-fab services and partnerships with OSATs

- OSAT partnerships

- Specialized packaging and test

- RF test for volume

- DMEA Trusted packaging partnerships

Outline

- 1. Background

- 2. Foundry Overview

- **3. Customer Focus**

- 4. Foundry Focus

- 5. Summary & Questions

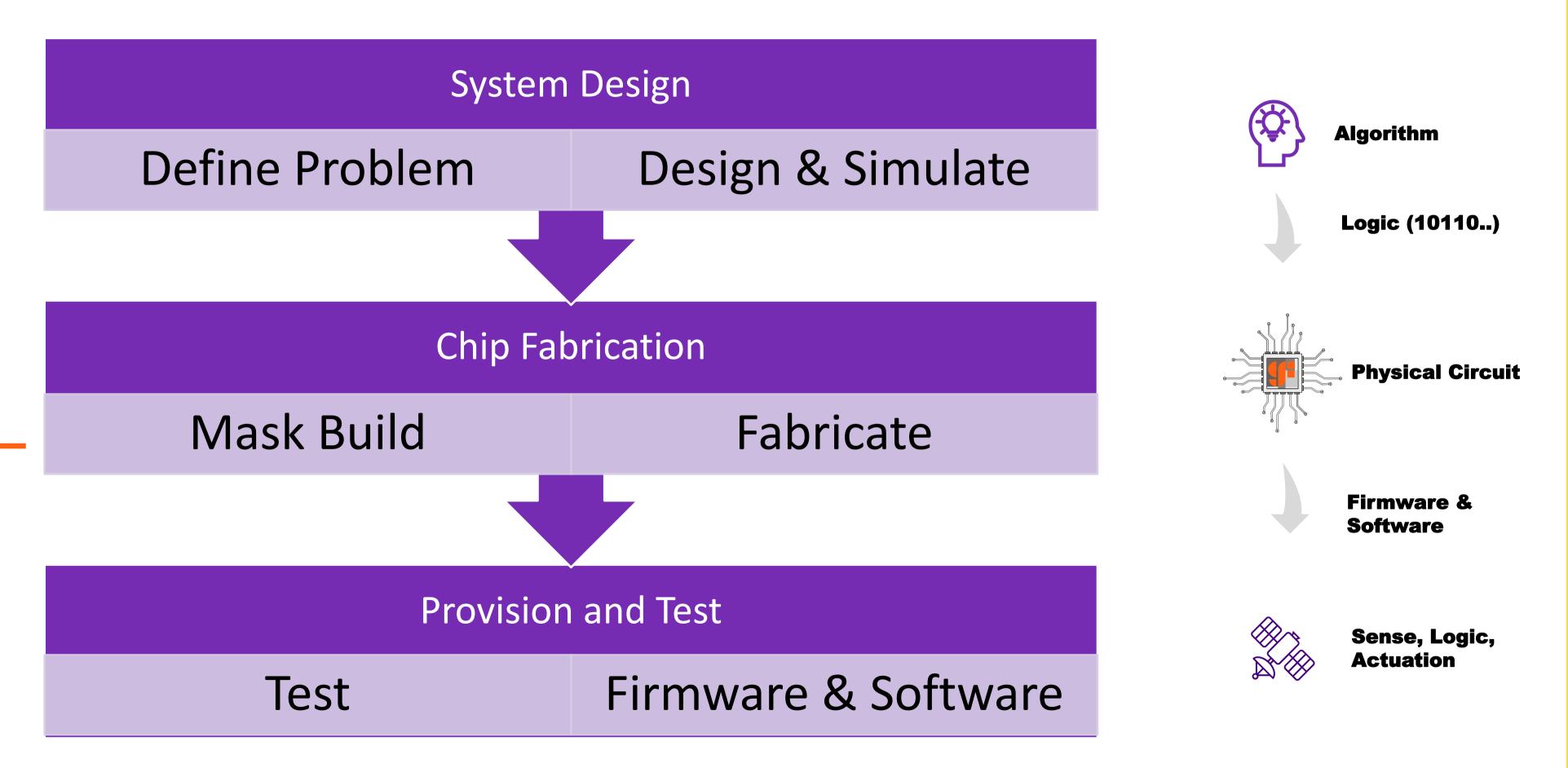

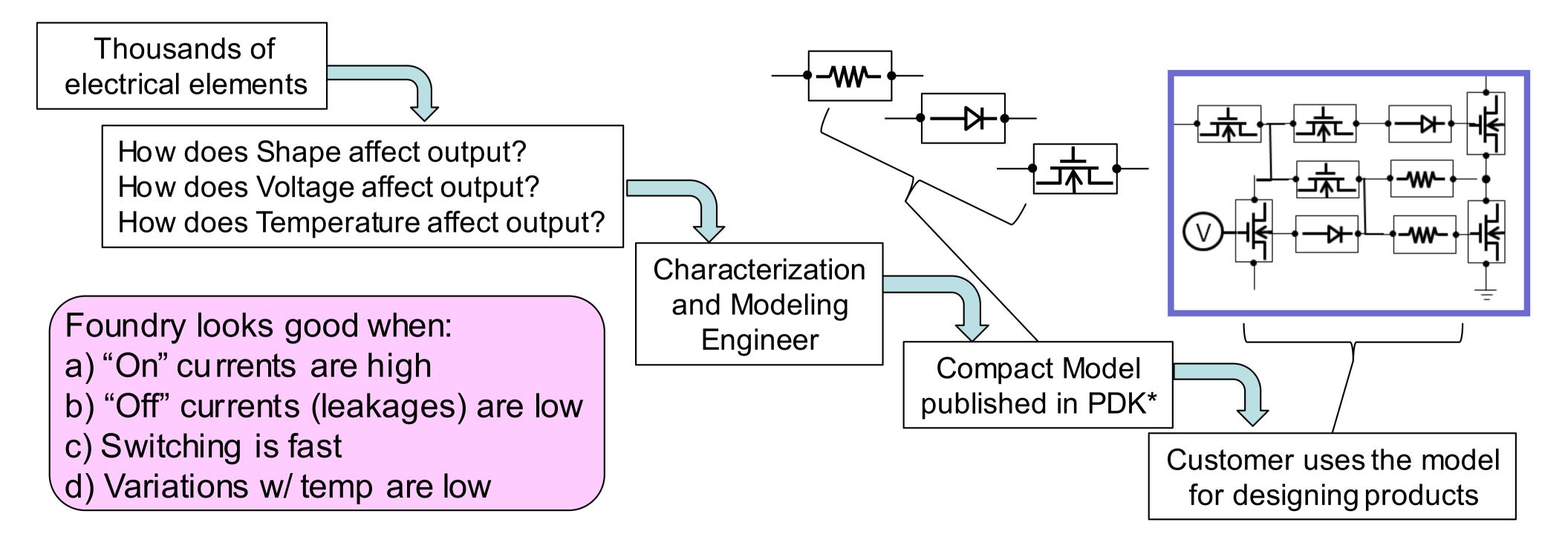

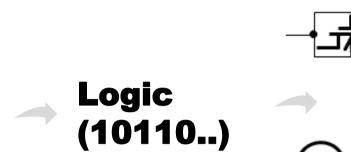

# **Design Innovation: Ideas to Logic**

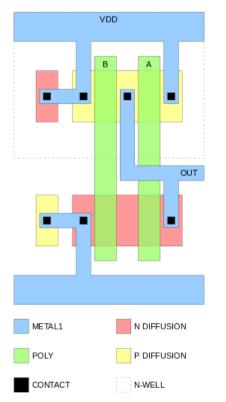

# Logic 101

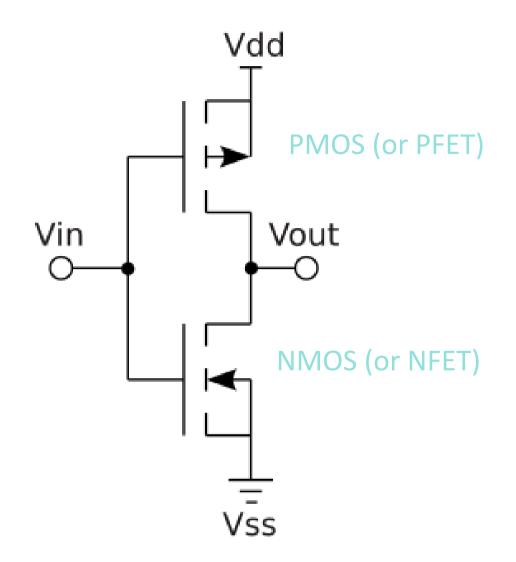

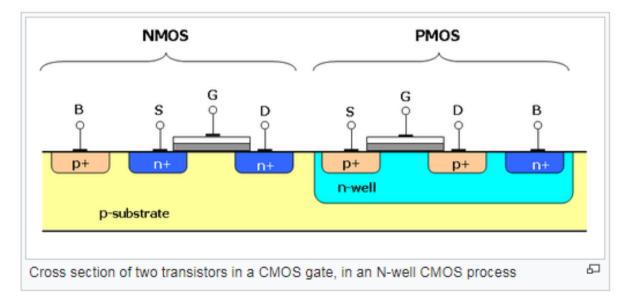

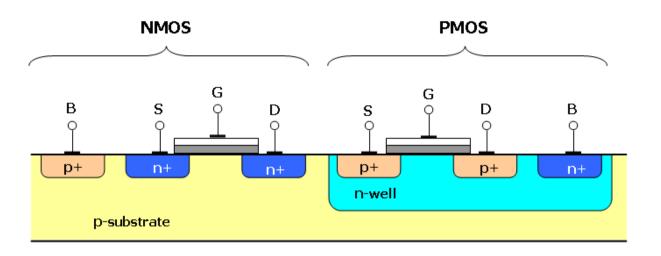

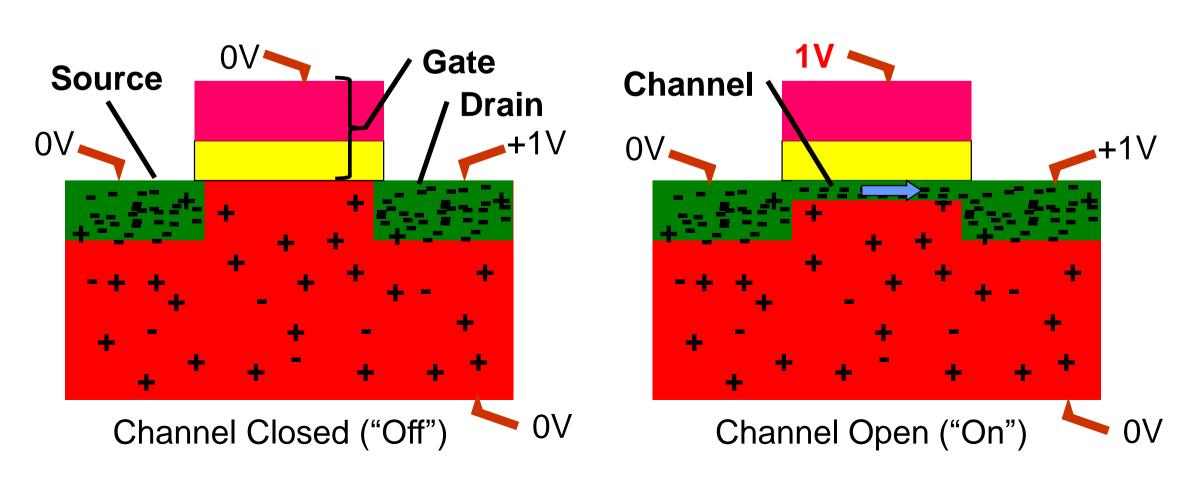

# What is a **Transistor?**

A device used to create logic and analog circuits Logic circuits operate on 1's and 0's 1 is a logic "high", or VDD (power supply voltage) 0 is a logic "low", or GND (power supply ground) Inverter example:

**Inverter Truth Table**

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

https://en.wikipedia.org/wiki/MOSFET

#### Schematic for an Inverter

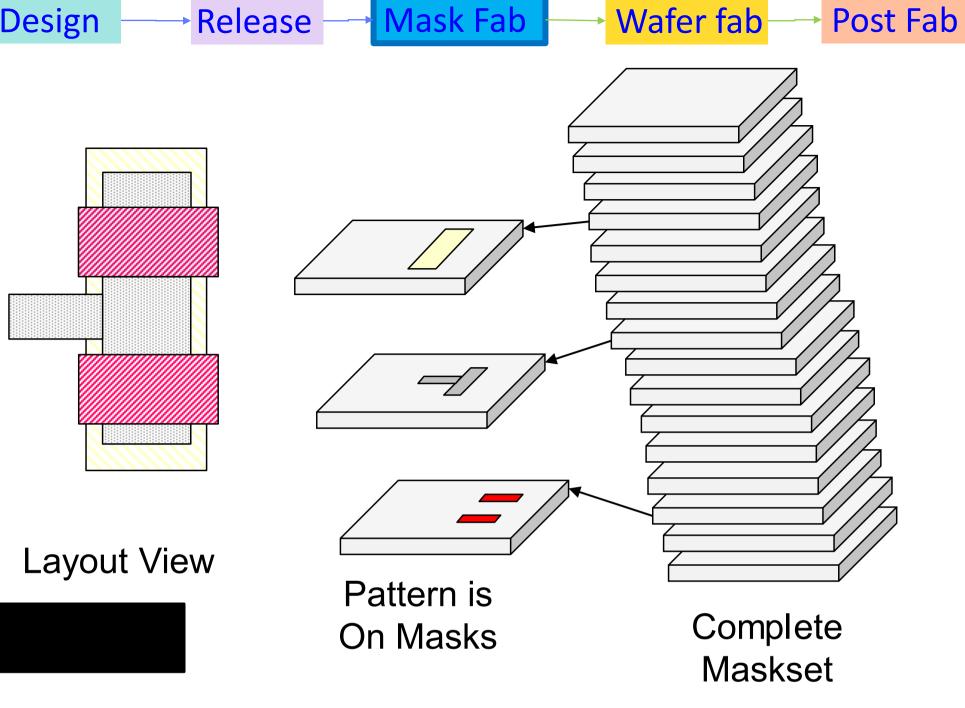

Mask Fab

## Device Cross Section (no wiring shown)

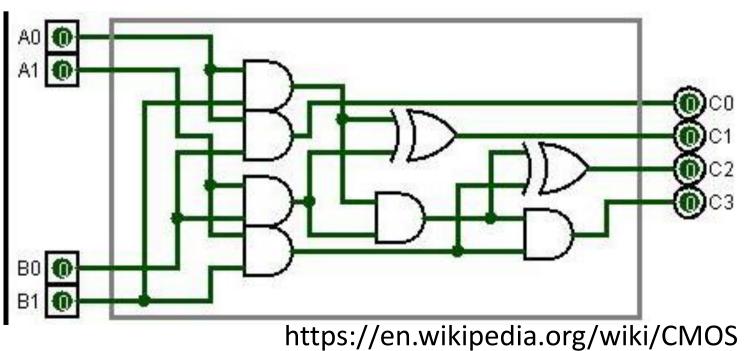

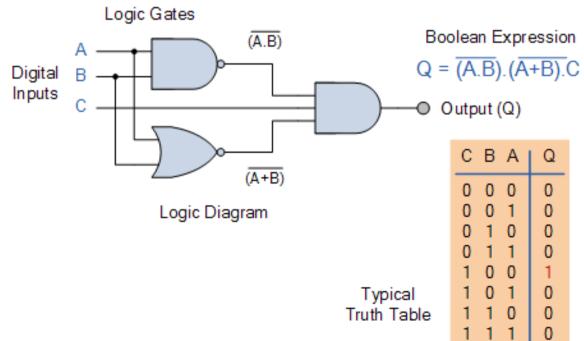

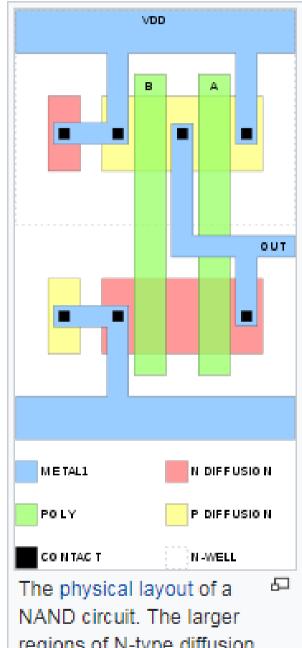

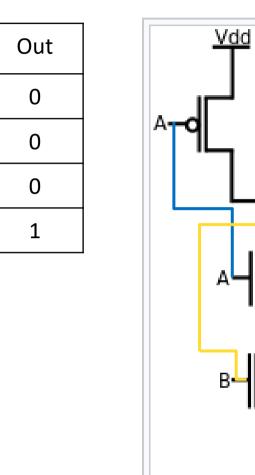

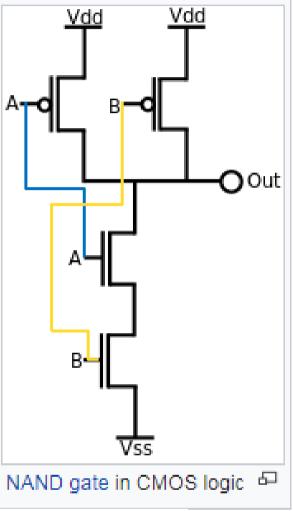

# Logic Devices

### NAND Truth Table

|    | А | В |

|----|---|---|

|    | 0 | 0 |

|    | 0 | 1 |

|    | 1 | 0 |

| 26 | 1 | 1 |

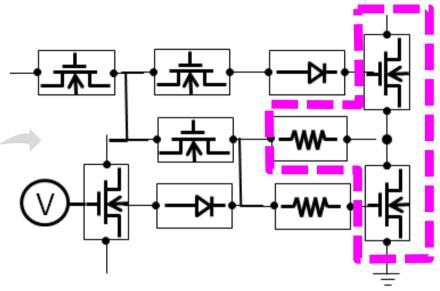

## **Combine Logic Elements to Arbitrary Circuit**

## 2 Bit Multiply

# **Arbitrary Logic Function**

Mask Fab

#### **Schematic**

Post Fab

regions of N-type diffusion and P-type diffusion are part of the transistors. The two smaller regions on the left are taps to prevent latchup.

Release

Wafer fab

# IC Design 101

# **Enable Design**<br/>**for Fabrication**

# Enable Design (PDK example)

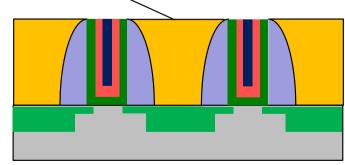

# **Cross-Section**

Here is what we'd see \_ in a 'Design Manual'

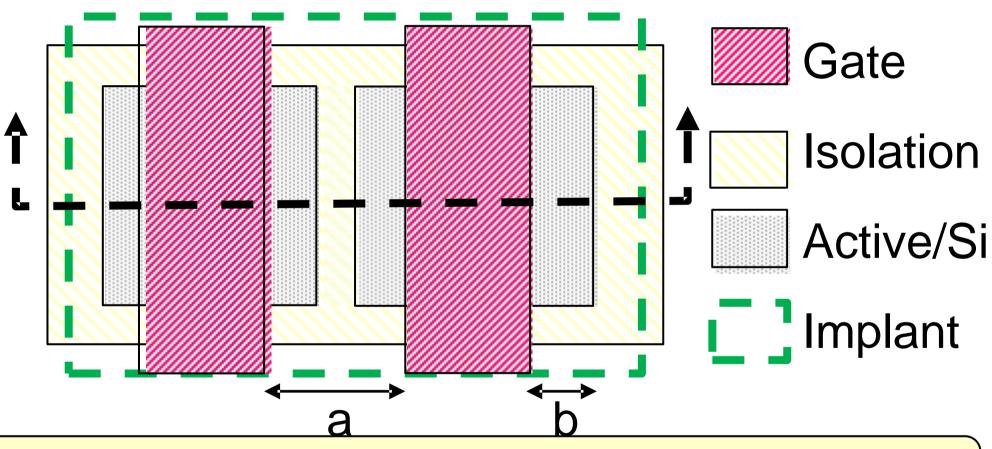

# Top-Down / Layout

y, Ground Rule #468: "2 Gates must be han xx nm."

y, Ground Rule #812: "Distance from ust be no larger than yy nm."

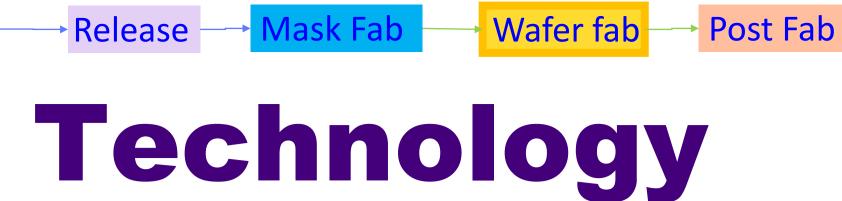

# **Typical IC Development** Activities

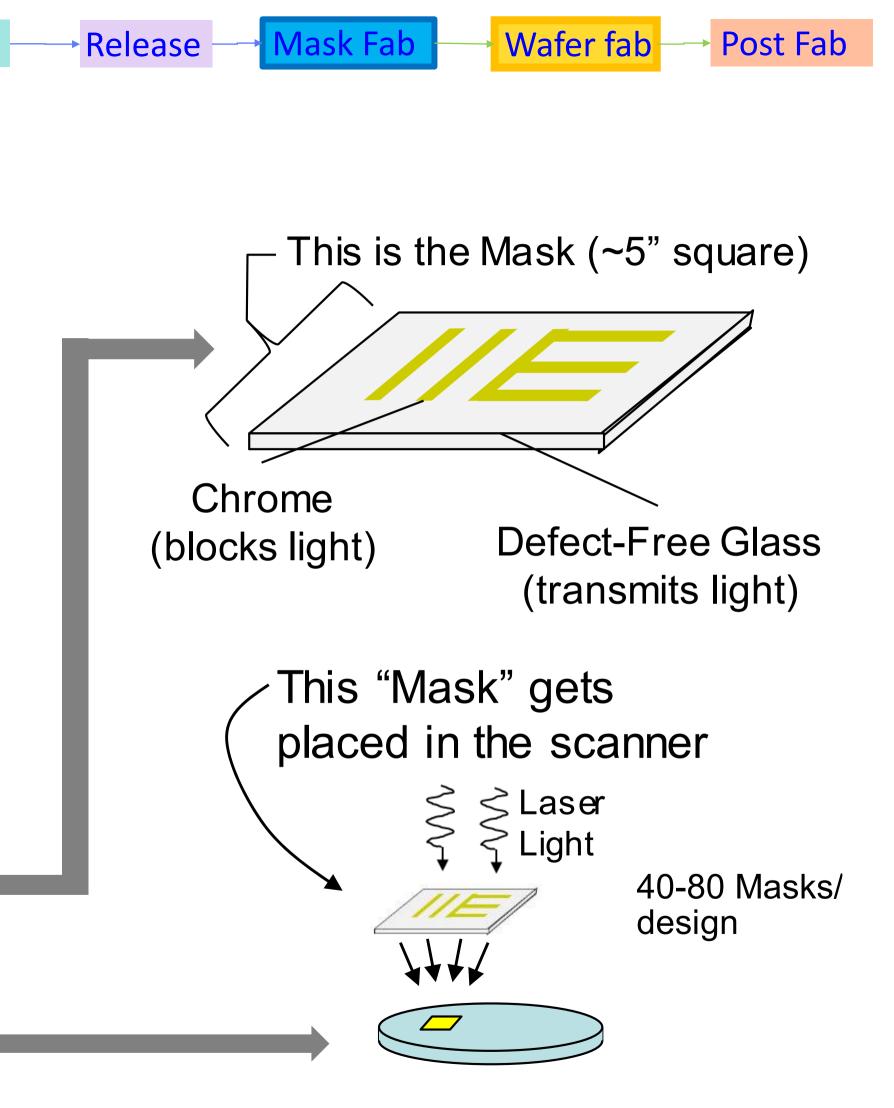

Release

Mask Fab

Wafer fab

Post Fab

Outline

- 1. Background

- 2. Foundry Overview

- **3. Customer Focus**

- 4. Foundry Focus

- 5. Summary & Questions

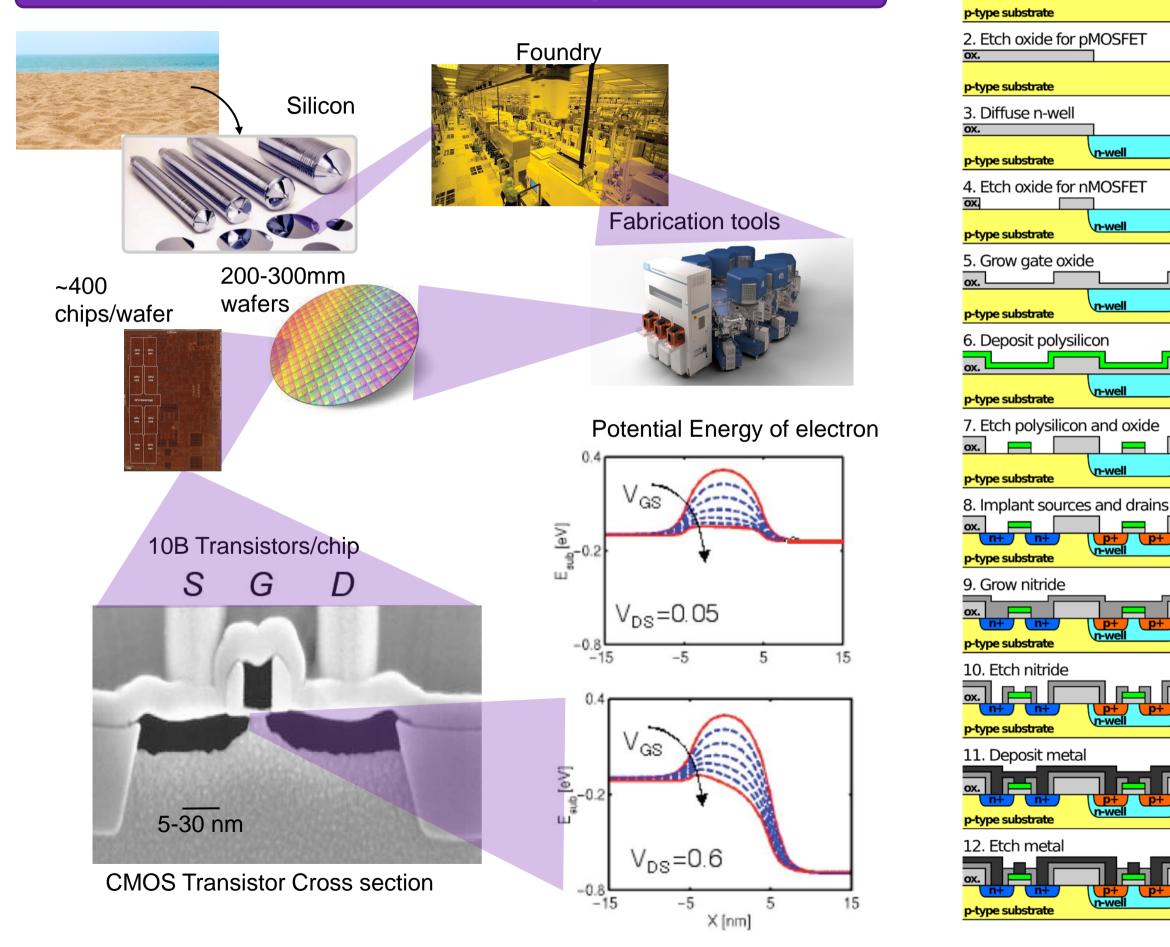

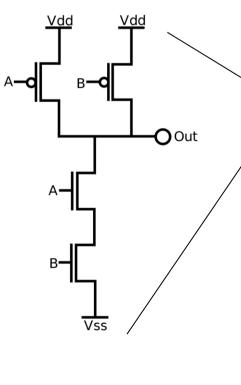

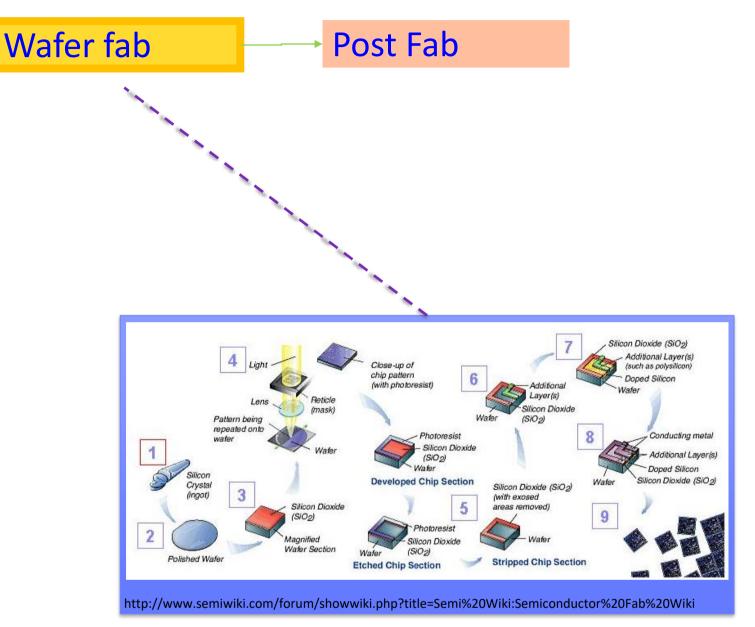

# **Building Chip Levels**

## Lifecycle – Sand to Electron Logic Overview

Sourced from across the internet

## Transistor to Processor Overview

#### Layout and Schematic of NAND Device

**Product Chips**

1. Grow field oxide

# **Mask and Wafer Fab Described**

#### Checking

• Verifies that physical shapes for each level comply with design rules

#### Kerf Merge

- Addition of design agnostic structures for manufacturing alignment and control

- Such standard Kerf structures are placed in the "interstitial" space between customer die.

#### Data Prep

Compensations applied to physical shapes, to counter exposure & wafer fab processing causal effects, to result in on wafer structures that match the design

### Masks are fabricated individually

• Depending upon the design and technology, 21 to 73 mask levels are uniquely fabricated for each customer program (such mask sets are built once and re-used in manufacturing for that program)

#### Fracturing

• Breaks the physical design shapes into primitive shapes the mask write tools can handle

#### Mask Write

- Light beam exposure tools write the shapes on a photoresist layer

- Etching is performed to create the shapes in chrome on glass

#### Inspection

• Each mask is optically inspected to verify the written shapes match the incoming data and are defect free

### Wafer Fabrication

- Industry standard semiconductor tools, with processes and recipes, are utilized to build each customer program

- Each "mask set" is specific to a customer's program

#### Kerf Test

Standard Interstitial kerf structures are tested at Metal 1, and again at Last Metal, to determine if each wafer is within manufacturing specifications

# What is a Mask?

End Customer: "I want a chip which can do xxx"

Designer : "OK, I'll connect the 100,000,000 devices in this manner."

Foundry (GF): "You must not violate these rules (how close to put devices, etc.)" Designer: "Confirmed. Here is my layout."

Foundry: "Thank you. We will build these masks, then run the Si."

> We "Tapeout" the digitized info to a Mask House

Design

Fab Planning Starts wafers

# Design to Mask

Algorithm

Designer's View

$\sim$

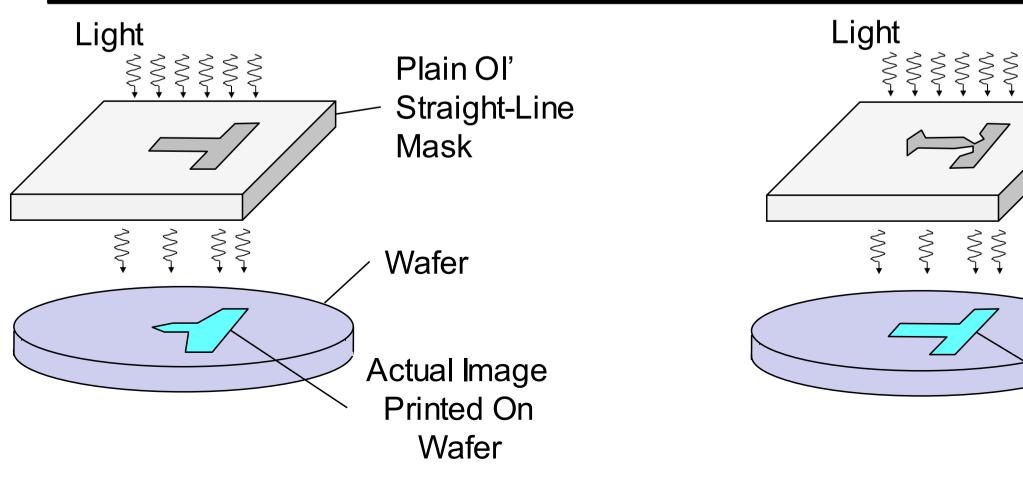

## **Optical Proximity Correction (OPC)**

Wafer

OPC'd

Mask

Actual Image Printed On Wafer

# Fabrication as Transformation

Design

## Design What Tools Do we use?

**Off-Line Metrology**

**AMAT Deposition**

**TEL Furnace**

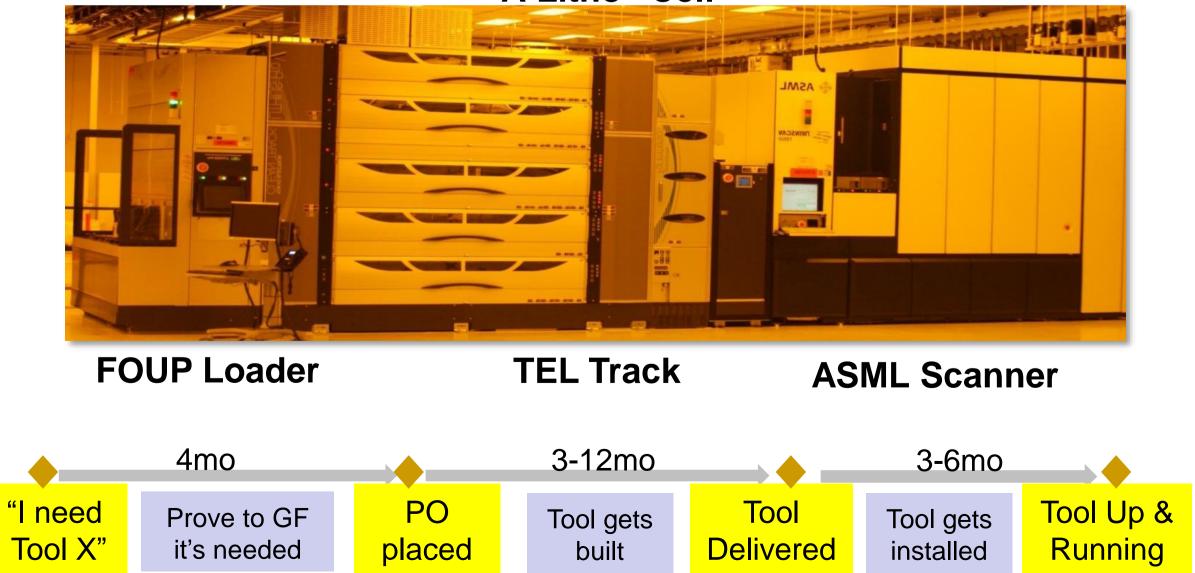

A Litho "Cell"

Mask Fab

Release

#### **Kokusai Deposition**

**AMAT Implanter**

**Ebara Polisher GlobalFoundries** © 2022 All Rights Reserved 37

Design

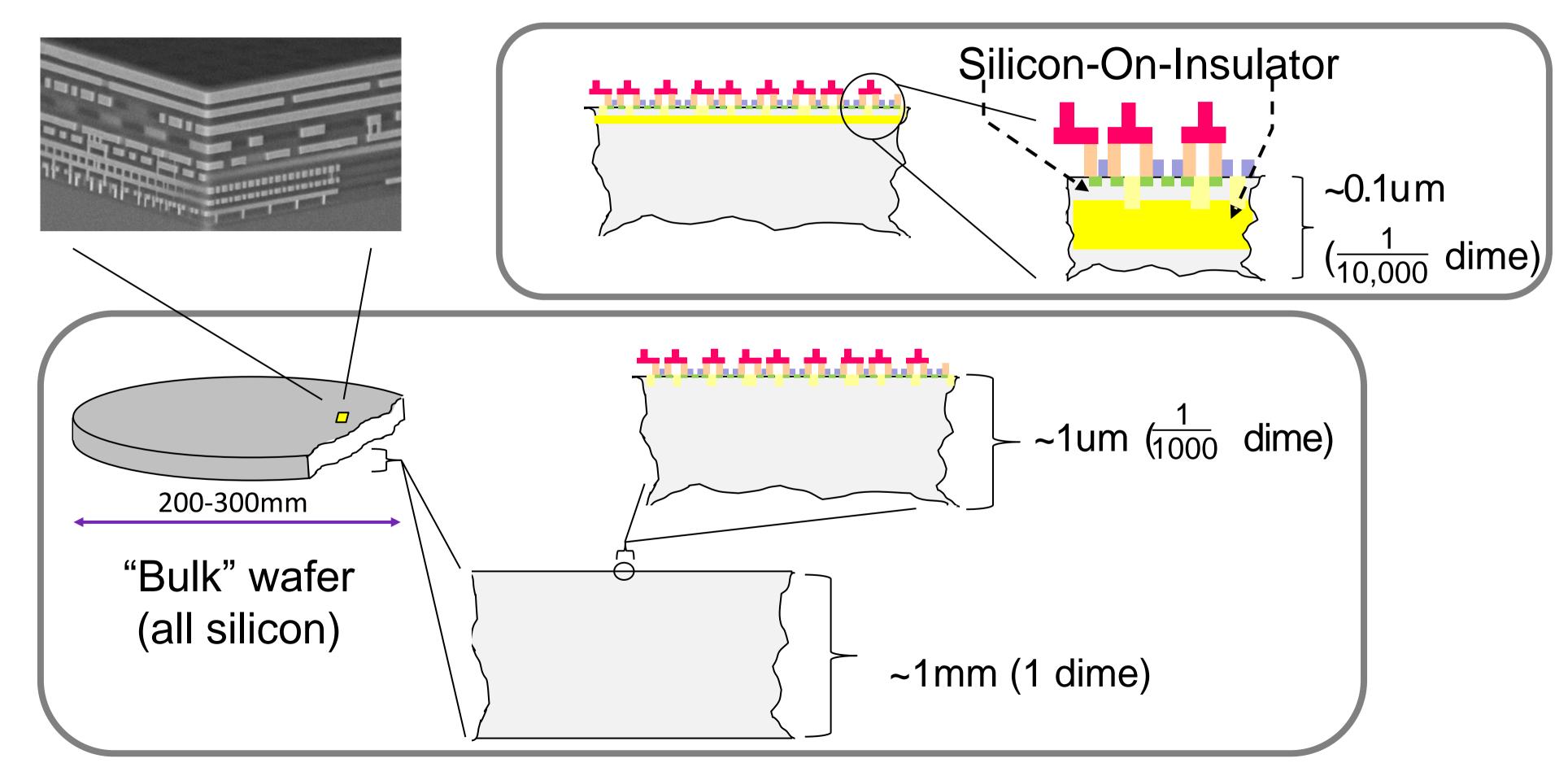

# Wafers and Technology sizes

Release -

Mask Fab

Wafer fab

## Who Does the work?

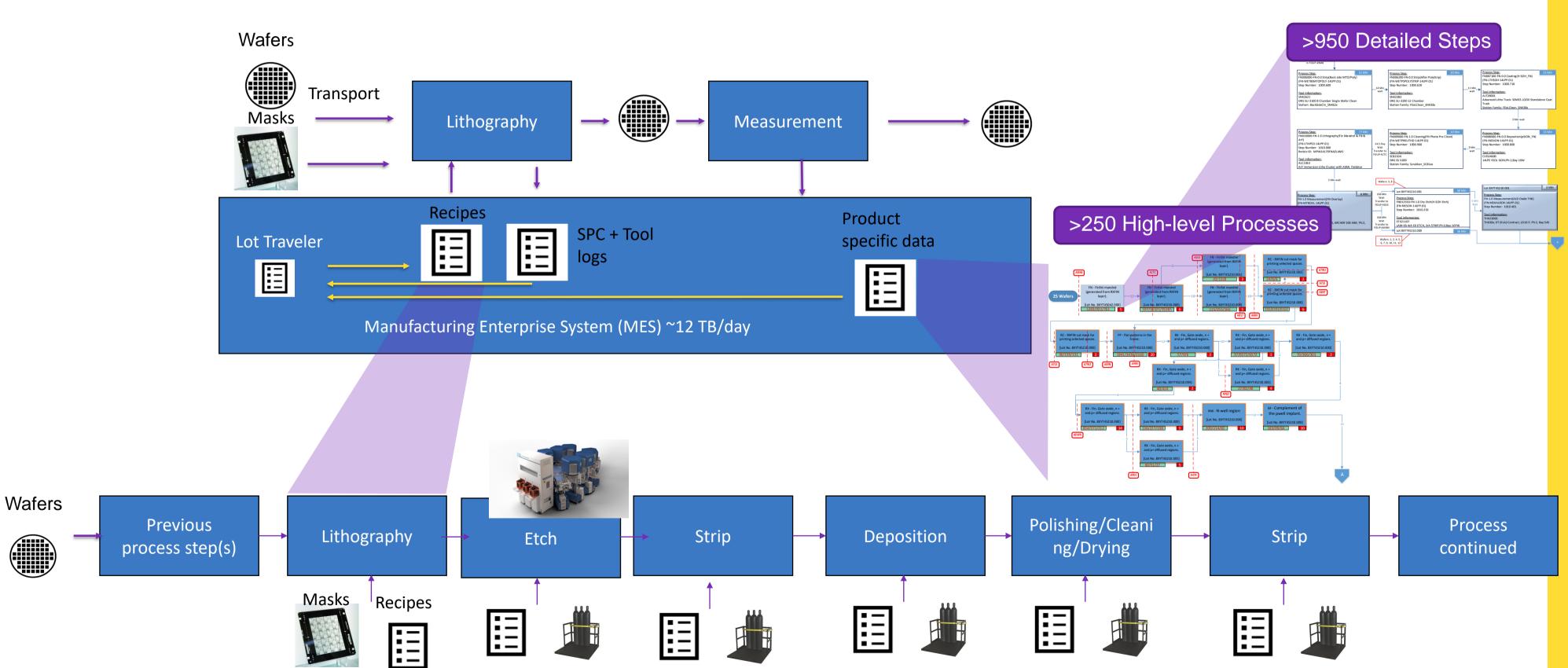

- Facilities: Keeping water / gases / chemicals / airflow clean & consistent

- Industrial Engineering: Planning materials movement through the fab (bottleneck) tools, how many wafers to start, new tools for capacity, ...)

- Equipment Engineering: Keeping the tools up / matched to brothers

- Process Engineering: Develop / maintain recipes (gas flows, temps, ...)

- Integration: Determine the series of 1000+ steps to go from start to finish

- <u>Test:</u> Test plans run on probers to extract electrical data and publish for use

- Device Engineering: Analyze the electrical data: are chips operating correctly?

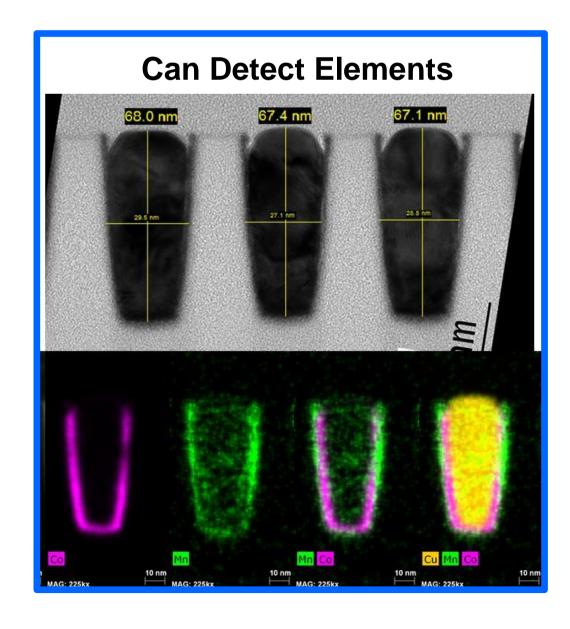

- <u>Characterization:</u> Electrical & Physical analysis (TEM, SEM, ...)

- Metrology: Measure thicknesses, dimensions

- Contamination-Free Mfg (CFM): Defect detection / classification

- Yield: Combine results of Metro, CFM, Test, Char'n to increase # good die

- Packaging: Encapsulate the chip, and enable connections to circuit board

- <u>Ground Rules / Design Manuals, PDK:</u> Establish a "Rule Book" that our customers must follow as they design their chip, so that we can repeatably build what they ask Manufacturing Tech / Automation / IT: Data acquisition / manipulation / storage tools

- (billions of data points taken daily from tools, testers)

Release Mask Fab

Post Fab

## Who Does the work: Lots & Routes

#### Integration Engineer

"I organize the series of 1000+ steps to enable all of the devices to be built in a single route."

#### Route-Build Engineer

"I check the route to assure tool-recipe agreement, and eliminate tool-to-tool contamination possibilities"

#### Operations Engineer

"I look across all lots in the fab, identify pinch-points, and maximize throughput."

|                  | <u>2</u>     |               |  |  |

|------------------|--------------|---------------|--|--|

| 6                | <del>)</del> |               |  |  |

| d                |              |               |  |  |

| la la            |              |               |  |  |

| ð                |              |               |  |  |

| 22 FD Route      |              |               |  |  |

| 0                |              | $\supset    $ |  |  |

| 28n              | m Route      |               |  |  |

|                  |              |               |  |  |

| 1100.1           |              |               |  |  |

| 1101.1<br>1102.1 |              |               |  |  |

| 1102.1           |              |               |  |  |

| 1103.1           |              |               |  |  |

| 1105.1           |              |               |  |  |

| 1106.4           |              | k.01          |  |  |

| 1109.1           |              |               |  |  |

| 1111.2           |              | p1            |  |  |

| 1113.1           |              |               |  |  |

| 1115.1           |              |               |  |  |

| 2100.0           |              |               |  |  |

| 2100.1           |              |               |  |  |

| 2101.1           |              |               |  |  |

| 2102.1           |              |               |  |  |

| 2103.1           |              |               |  |  |

| 2104.2<br>2105.1 |              |               |  |  |

| 2105.1           |              | k.01          |  |  |

| 2100.4           |              |               |  |  |

| 2103.1           |              | þ1            |  |  |

| 2113.1           |              |               |  |  |

| 2115.1           |              |               |  |  |

| 3100.0           |              |               |  |  |

| 3100.1           |              |               |  |  |

| 3101.1           |              |               |  |  |

| 3102.1           |              |               |  |  |

| 3103.1           |              |               |  |  |

| 3104.2           |              |               |  |  |

| 3105.1           |              | k01           |  |  |

| 3106.4<br>3109.1 |              |               |  |  |

| 3109.1           |              | b1 U          |  |  |

| 3113.1           |              |               |  |  |

| 3115.1           |              |               |  |  |

|                  |              |               |  |  |

| 1                |              | )             |  |  |

### <u>Metrology Engineer</u>

"I measure thicknesses and physical properties, enabling control charts."

#### <u>Contamination-Free Engineer</u>

"I detect & identify particles on the wafers to highlight tool / process issues."

#### Industria I Engineer

"I look at the tools & recipes listed on each route, and the predicted # wafers for next 2 years, and determine if we need to adjust / buy more tools."

# Who Does the work: Facilities

Facilities Engineer "I provide clean and consistent water, gases, and chemicals to the tool."

#### Equipment Engineer

"Given confidence in consistent raw materials, I assure the valves, flow controllers, sensors are working, so we get the exact flow we want at the temp we want."

Unit Process Engineer "Given confidence in flow rates, I develop a recipe which calls gases, flows, and temps so that we deposit / etch exactly what we want – no more, no less."

Automation Engineer "Every wafer, every recipe, I assure the software monitors for errors / hiccups and reports all processing details."

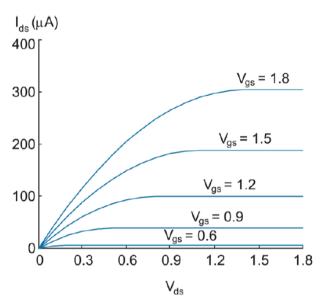

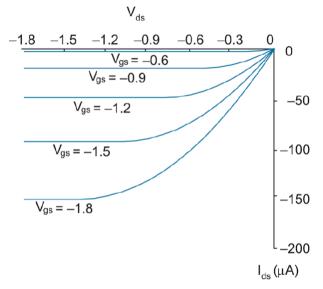

# Who Does the work: Technology

# <u>Test Engineer</u>

V<sub>g</sub>=1.0

V<sub>g</sub>=0.6

V<sub>g</sub>=0.2

0.5

Drain Voltage V<sub>d</sub>

"I stress the individual devices and the full chips beyond normal conditions, to enable estimation of lifetime."

"I probe individual devices and full circuits, and provide the data in useful format for analysis by others"

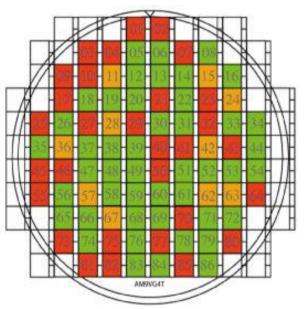

#### Yield Engineer

"I look at outputs from full circuits and memory arrays, and correlate to metrology / contamination results, to determine how to increase the % working chips."

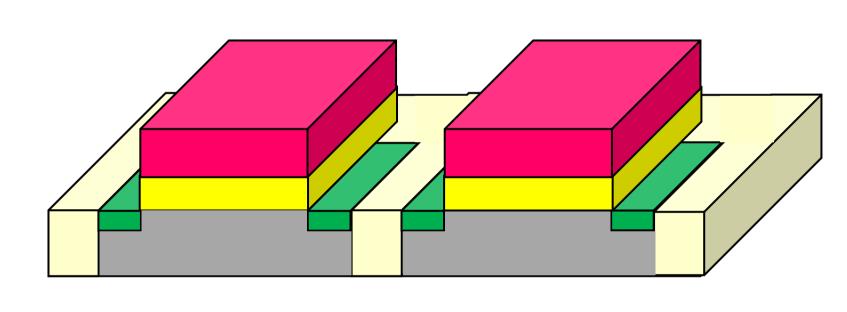

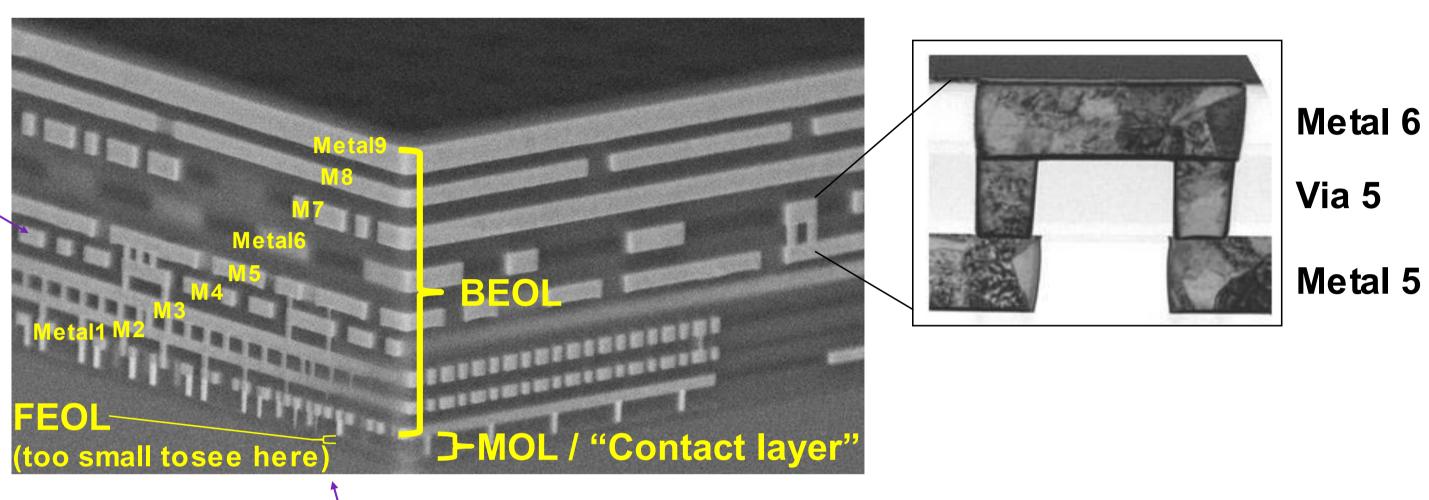

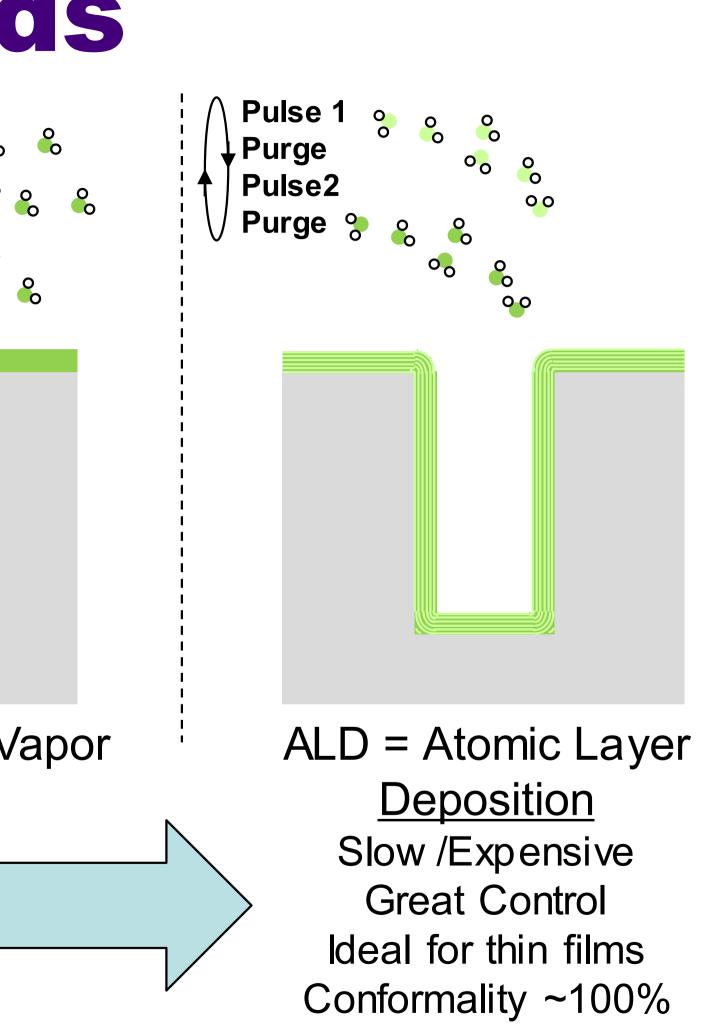

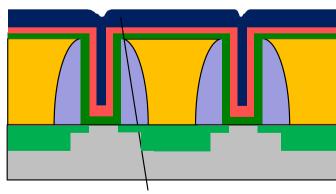

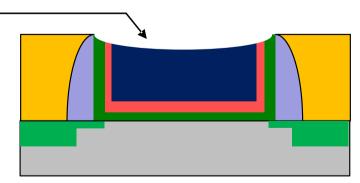

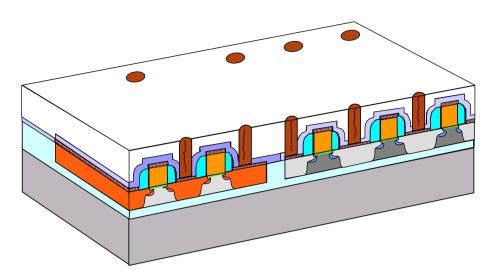

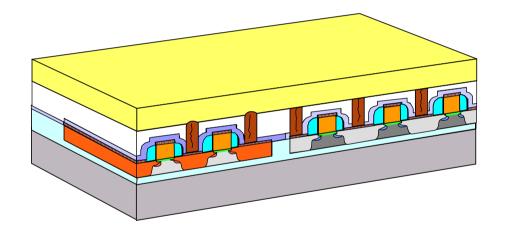

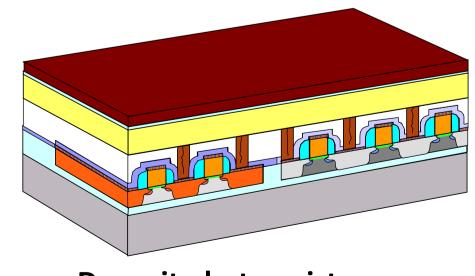

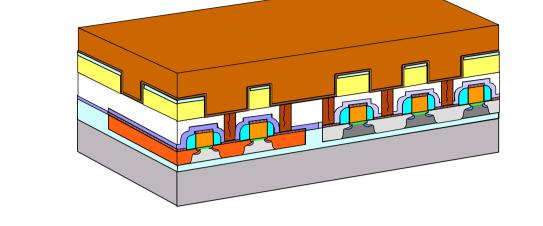

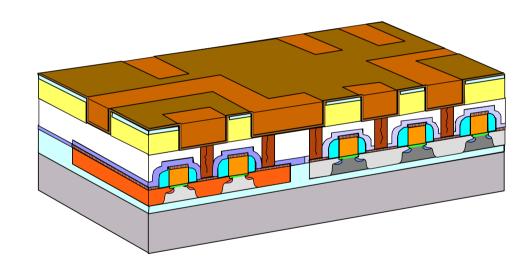

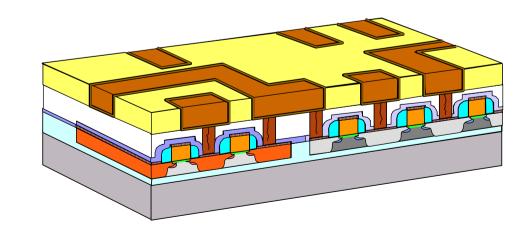

# **Chip Levels**

### **Back end levels (BEOL)**

- Build up of insulating layers, metal • interconnect wiring, and vias defining passive structures

- Routes power and ground •

- Connects front end structures to define • chip functionality

- Interfaces with external connections •

Release

Mask Fab

Post Fab

Wafer fab

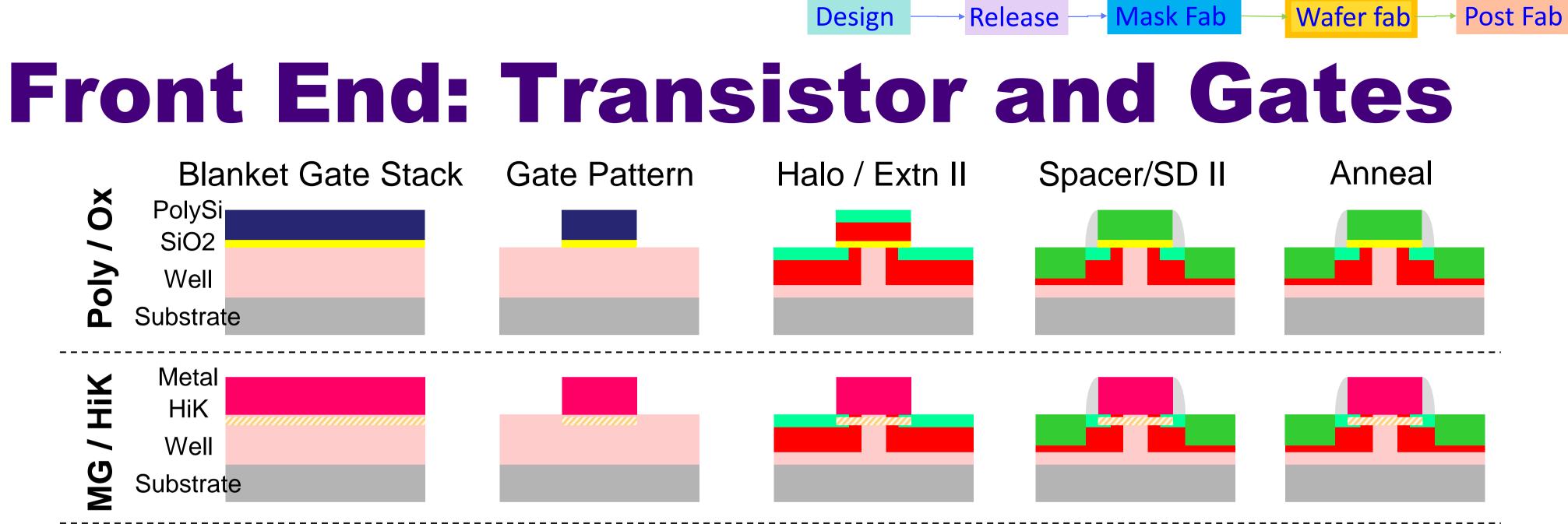

#### **Front end levels (FOEL)**

- Build up of insulating layers, and polysilicon, diffusion, & implants, defining primitive active circuit Devices: •

- Transistors

- Diodes

- Capacitors

- Resistors

- Memory storage elements

- Creates primitive building blocks for subsequent connection with back end levels to create functionality

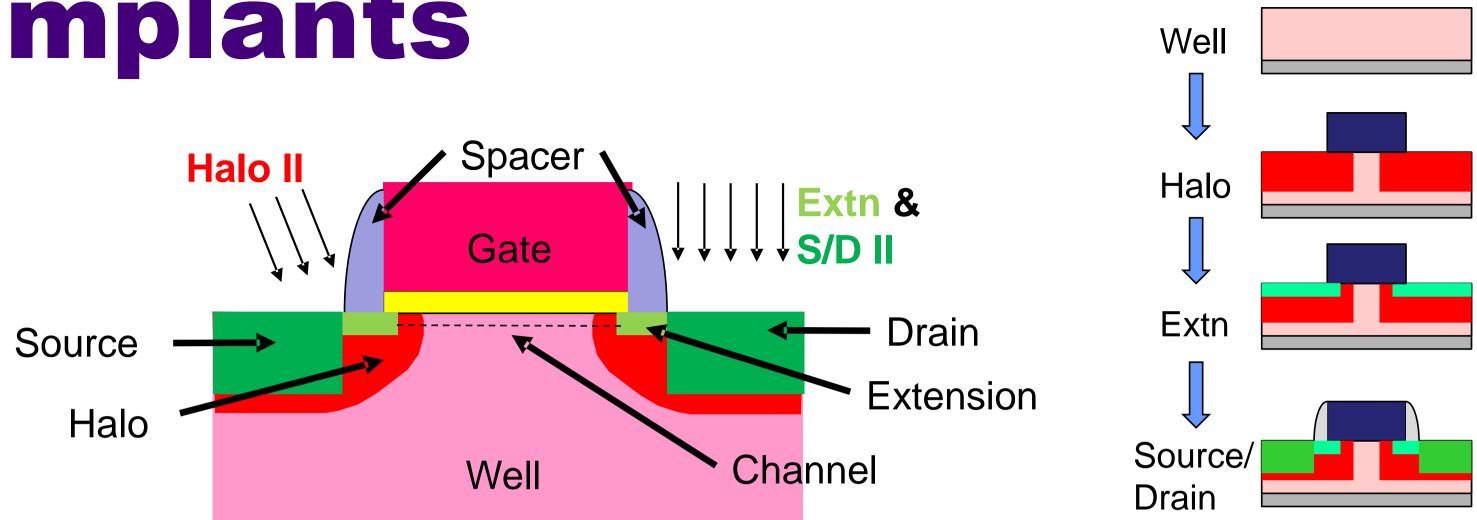

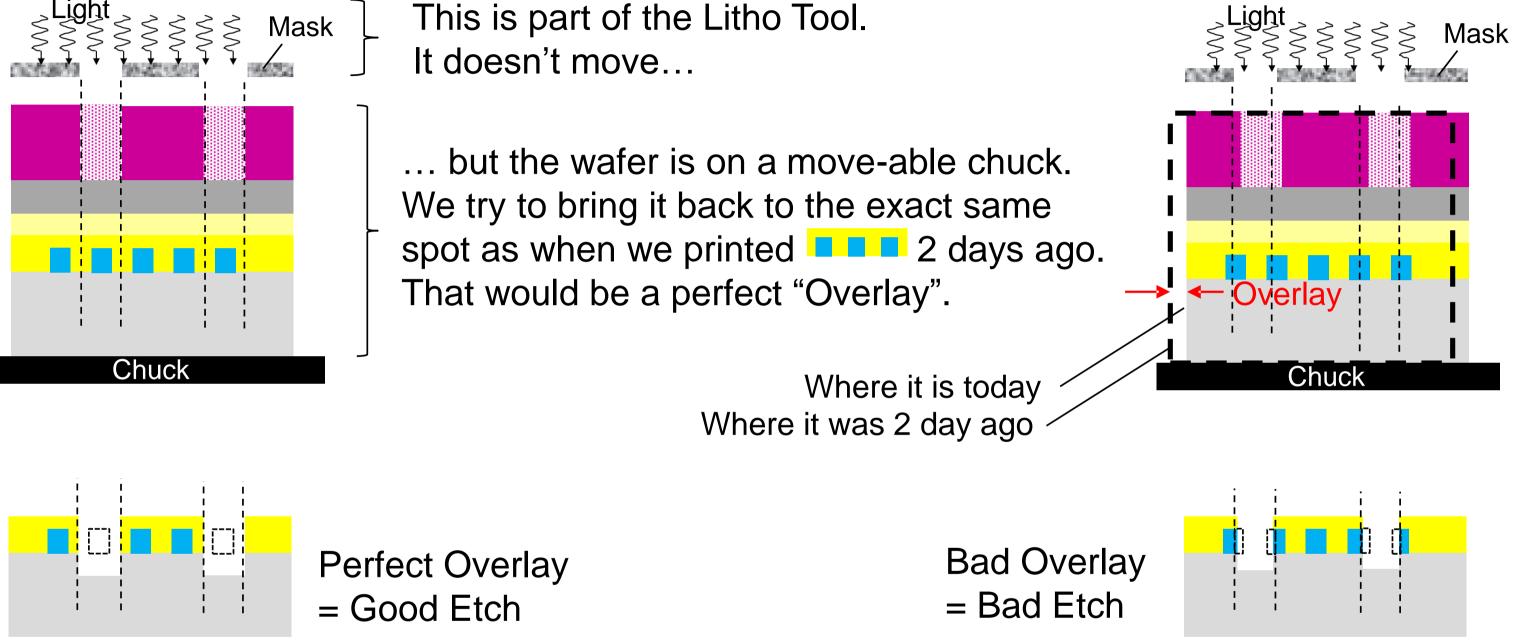

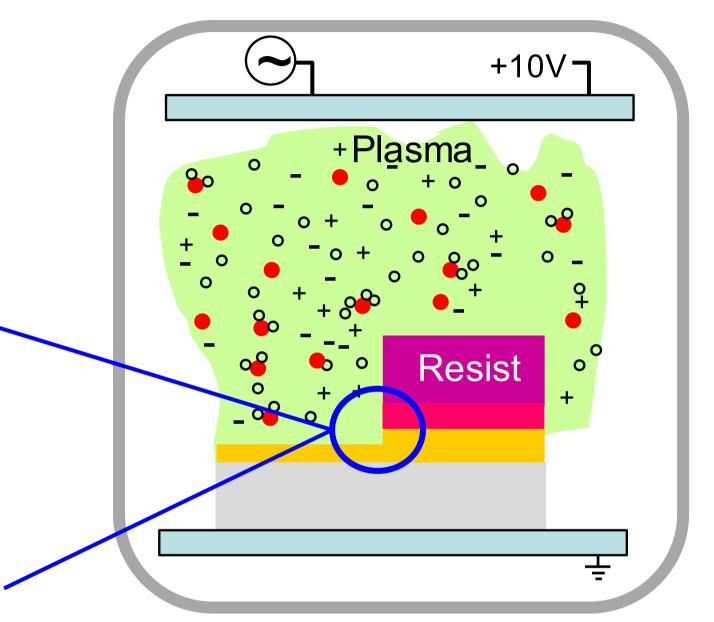

# Implants

- Halo implants block current from passing beneath the channel. This implant is the opposite type to the Source and Drain.

- Extension implants are used to "extend" the source and drain under the spacer. These are doped the same as the S/D (n-type for NMOS, p-type for PMOS).

- Transistors require several different doping / resistance levels

| Implant   | Dose (cm <sup>-2</sup> ) | Doping Cond |

|-----------|--------------------------|-------------|

| Wells     | ~5E12                    | ~58         |

| Halo      | ~5E13                    | ~58         |

| Extension | ~5E14                    | ~58         |

| S/D       | ~5E15                    | ~5E         |

<u>ıc'n (cm<sup>-3</sup>)</u>

5E17

E18

E19

E20

<u>Resistivity</u> High

45

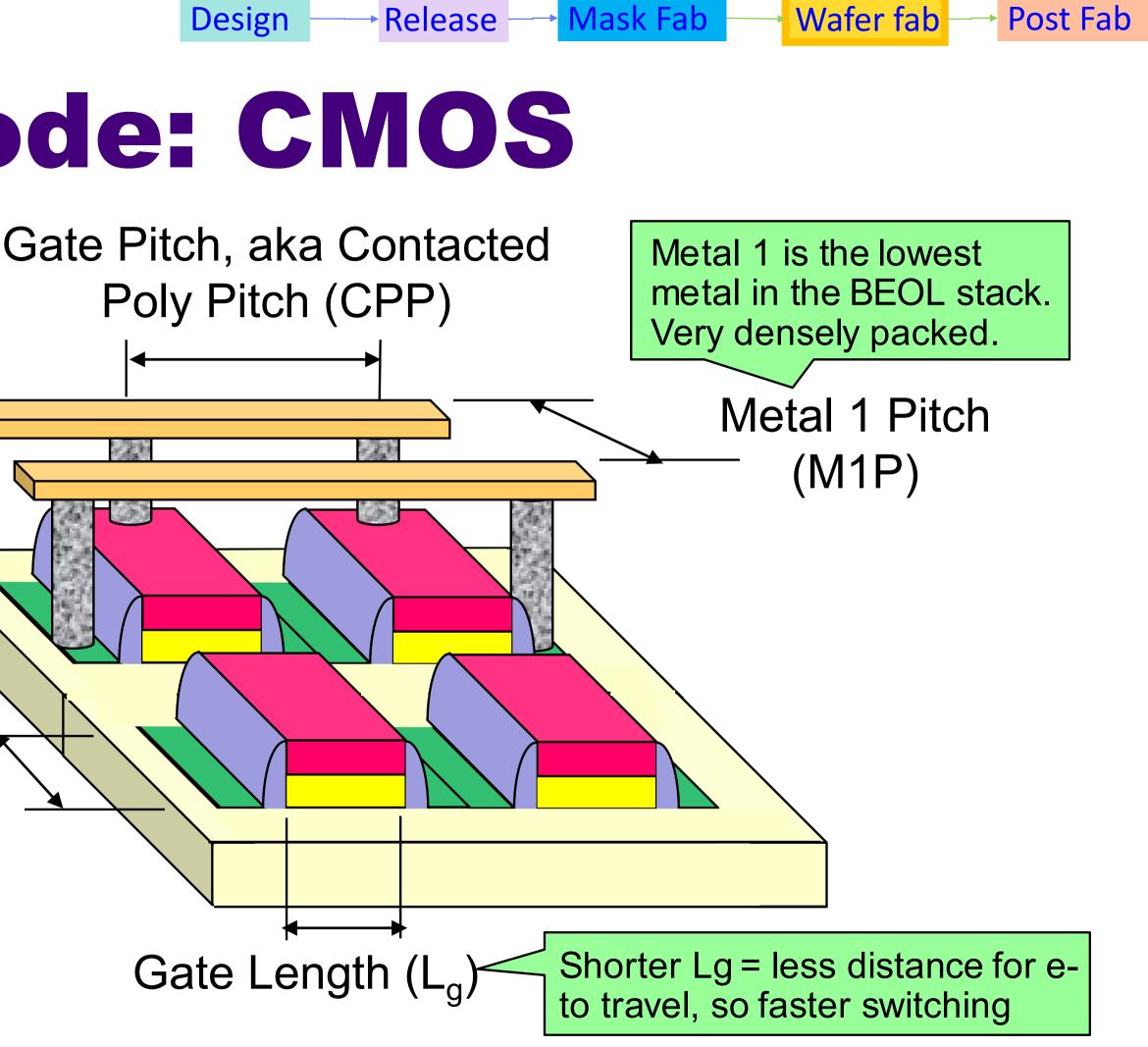

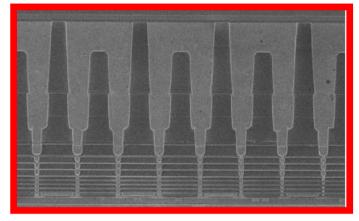

# Technology Node: CMOS

For so many years, we made gates from polysilicon, that we started calling gates "poly."

Active' Si is means the electrically active (doped) regions, where we're building devices. Essentially, whatever is NOT isolation.

> Active Si Pitch

Gate Width (W)

Here we show a Planar Technology – the X'tors are in the plane of the wafer.

Design

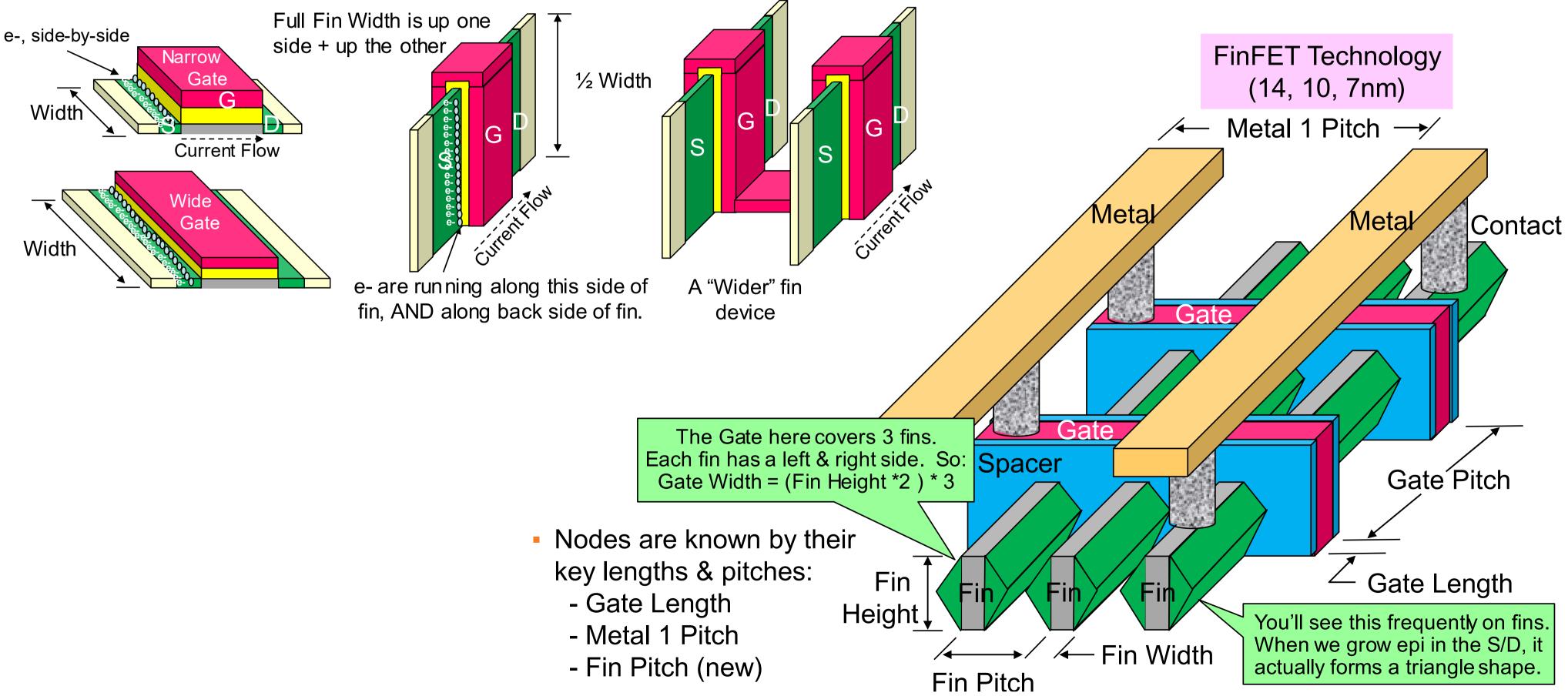

# **Technology Node: CMOS FinFET**

Release

lask Fab

Wafer fab

Post Fab

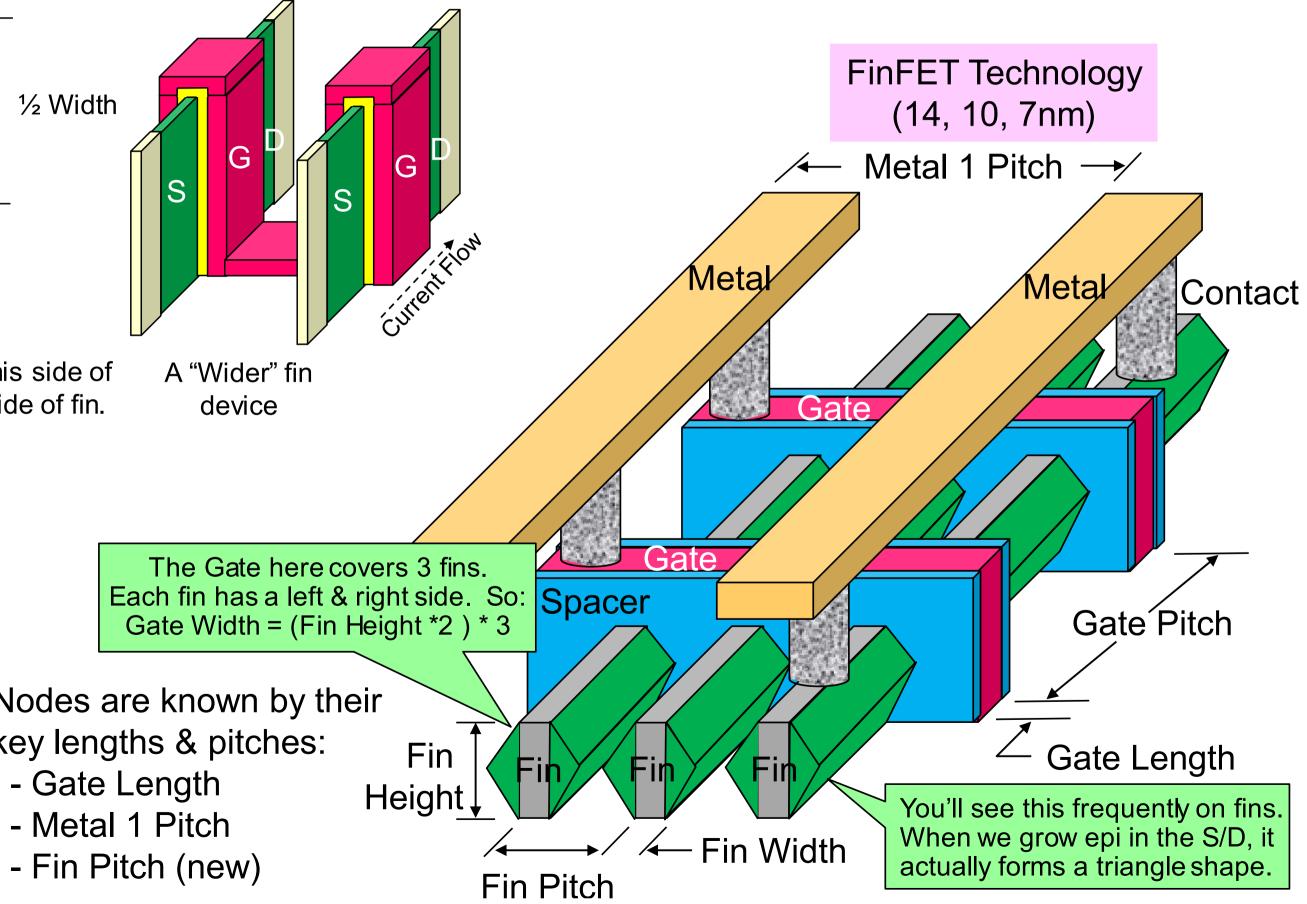

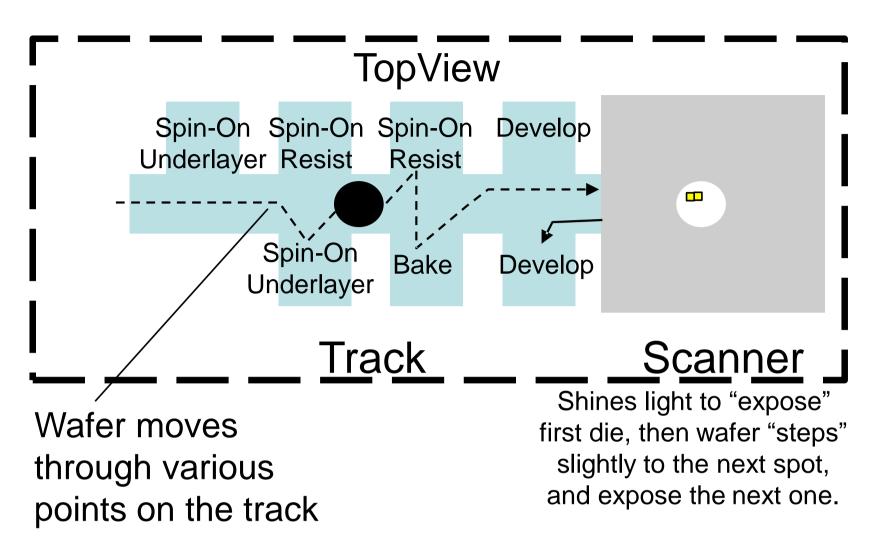

# Litho: Track and Scanner

Side View

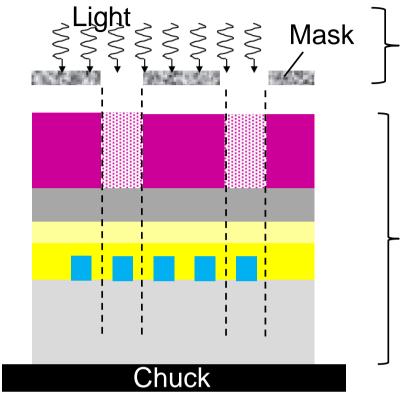

# Litho: Overlay

- When I shine my light, how well am I lined up with the underlying structures?

- Overlay on current tools ~5nm, meaning the tool says: "I can always come back to within 5nm (~20 atoms) of where I was last time"

... Amazing

- We have created 2 distinct regions of different doping N and P.

- Together these form a Diode. We've made a device!

ifferent doping – N and P. ade a device!

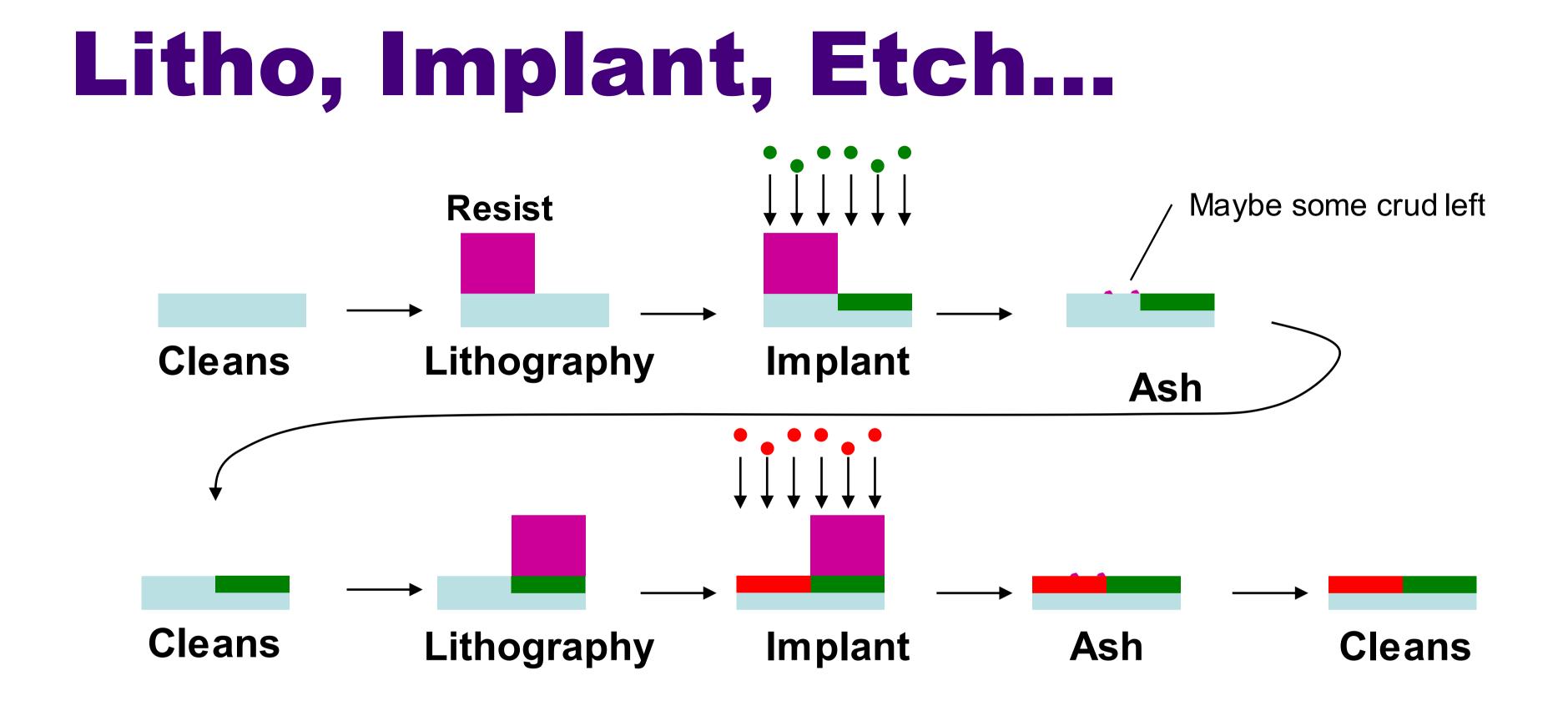

## Etch: Reactive Ion Etch

There are 2 voltages happening here. - High Frequency Alternating (13MHz) This creates the plasma by tearing apart the atoms in the gas, creating ions - Constant (DC) voltage drives the charged ions down to the surface Isotropic

**Etch Mechanisms**

Many Etches are used in semiconductor fabrication ... RIE is the most common and controlled

An-isotropic

### Chemical Reactions **Physical Impact**

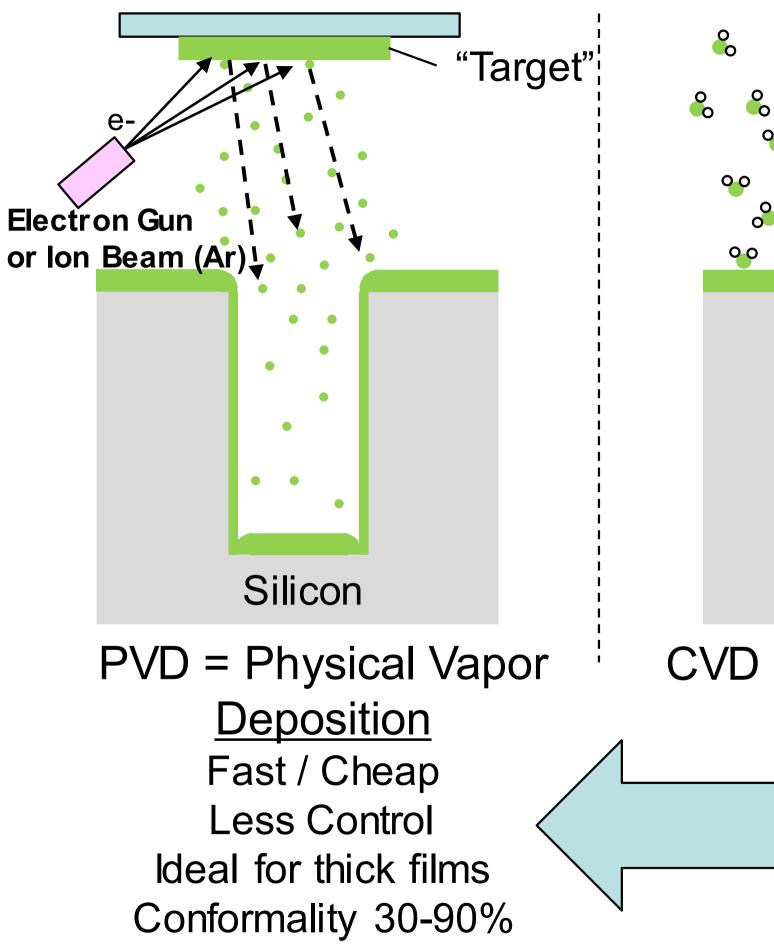

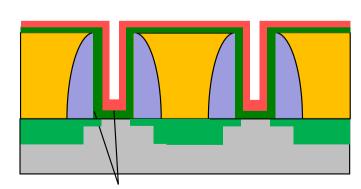

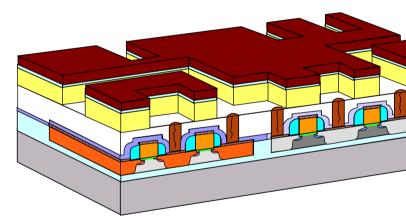

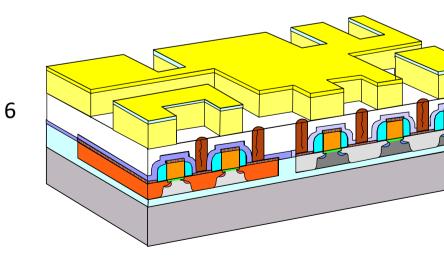

# **Deposition Methods**

### CVD = Chemical Vapor <u>Deposition</u>

## **Chemical Mechanical Planarization**

These 2 layers done by Atomic Layer Deposition (HiK & TiN, for example)

Remaining gap is filled by Chemical Vapor Deposition (Tungsten). "Over-fill" is OK.

Chemical reaction won't occur on this oxide, so polishing stops!

Polish (CMP) to remove undesired excess material.

Features that are too wide can dish...

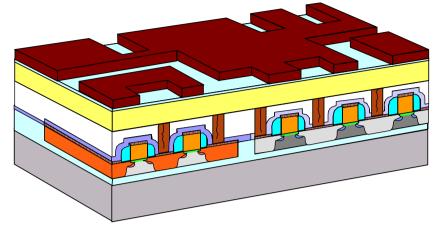

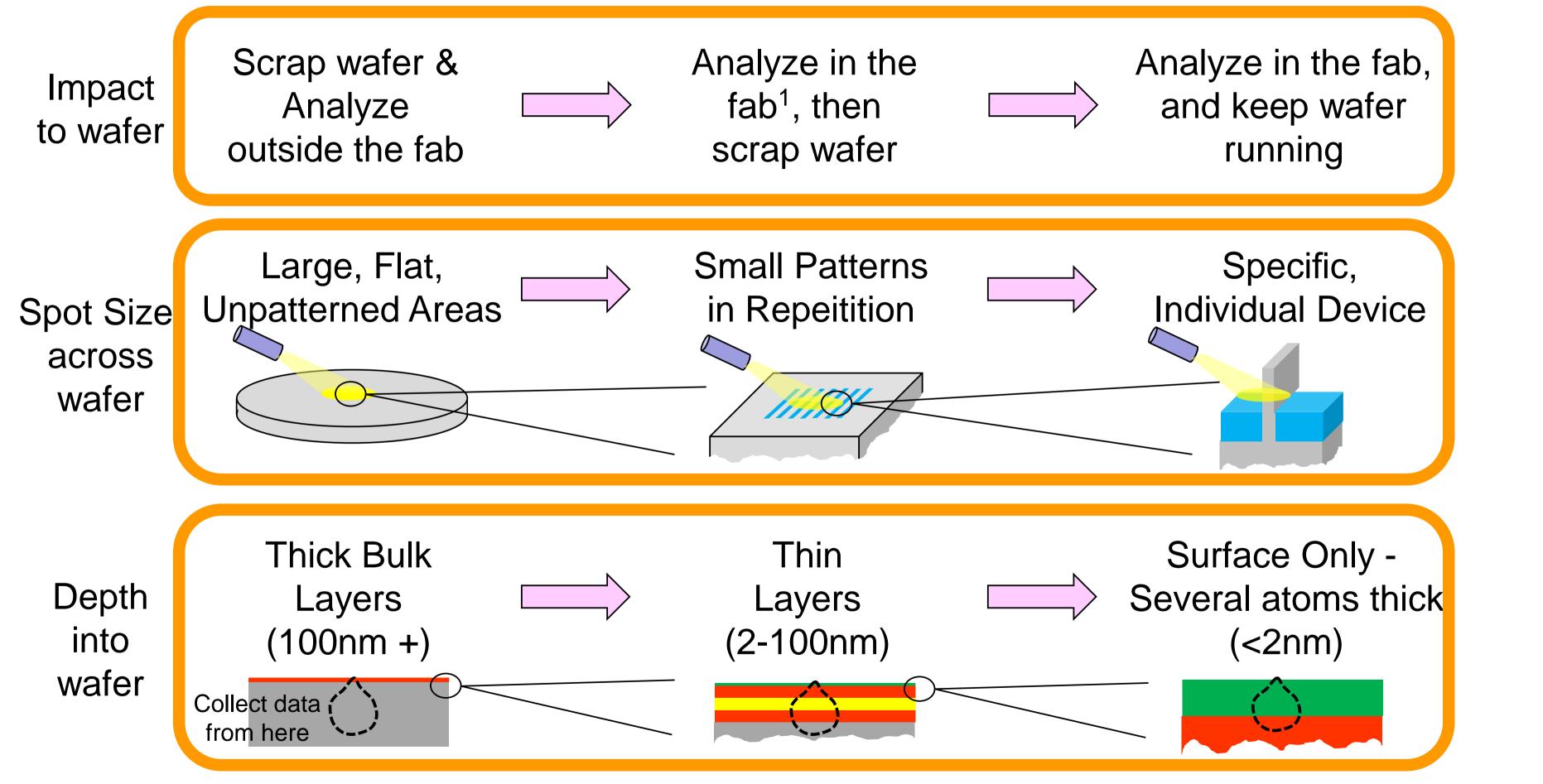

## **Back End : Metal 1**

4

5

**Reveal Vias to transistors**

**Deposit oxide dielectric**

**Deposit photoresist**

Pattern photoresist

#### **Etch oxide dielectric**

Strip photoresist

2

3

1

7

8

9

#### **Deposit liner & plate copper**

#### **Chemical Mechanical Planarize to liner**

#### **Remove liner**

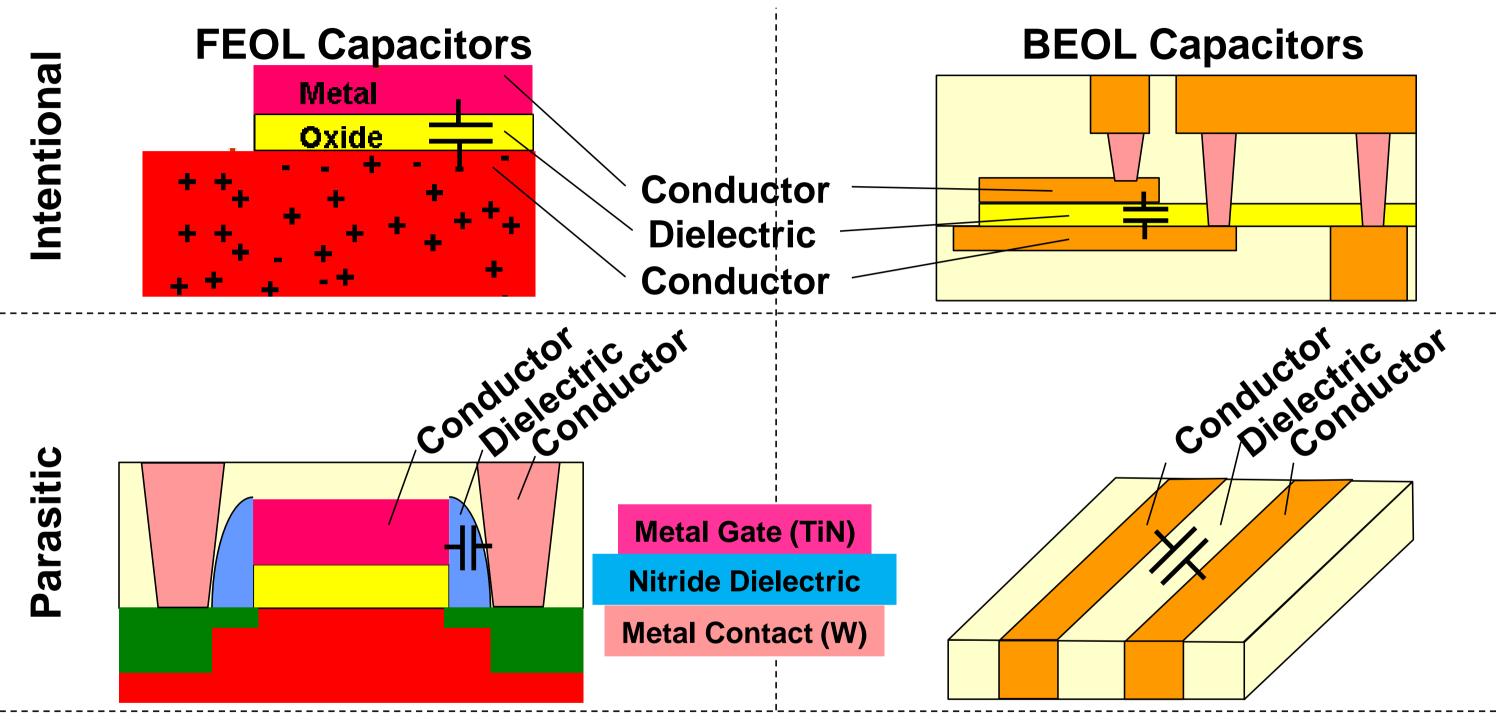

- A capacitor is simply a stack: Conductor / Dielectric / Conductor

- Some capacitors we build intentionally so we can store charge in our circuit.

- Others occur unavoidably. These are referred to as "Parasitic" capacitors.

- BEOL capacitors are often called "MIMCaps" (Metal / Insulator / Metal).

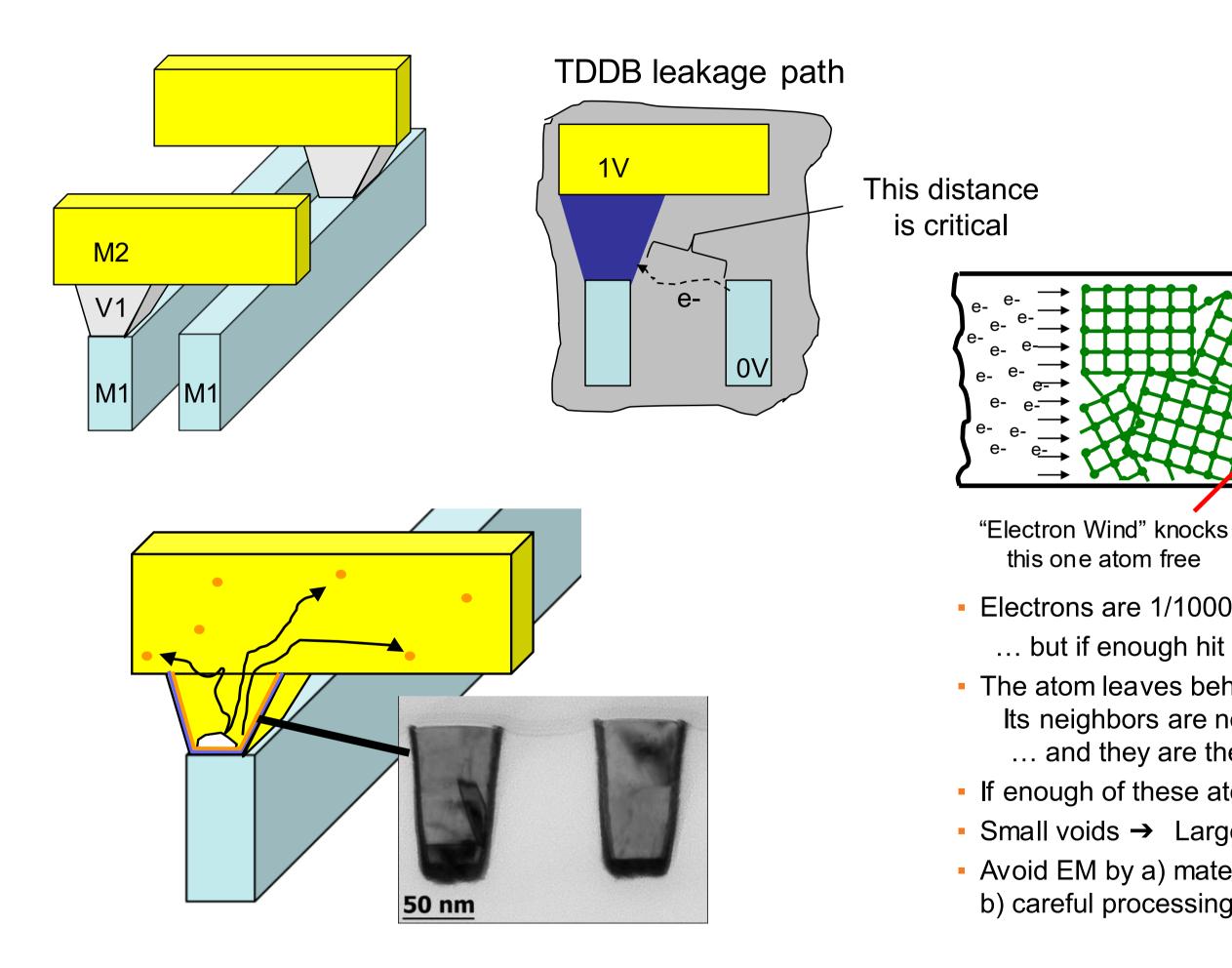

# Interconnect: Leakage & Voids

Avoid EM by a) material selection (interface layers);

b) careful processing & eliminating initial defects

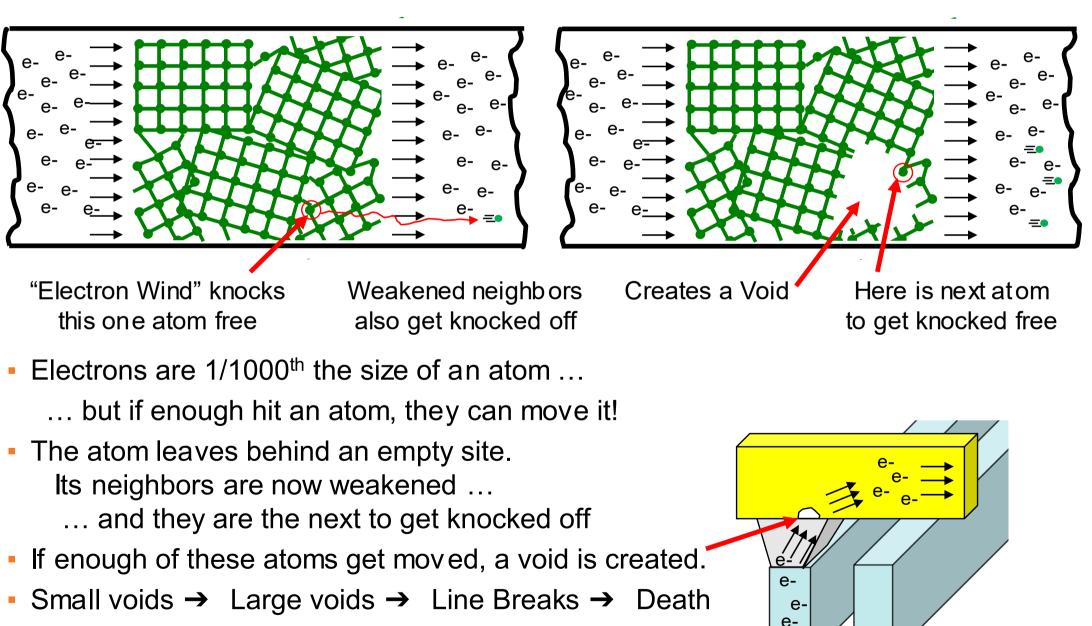

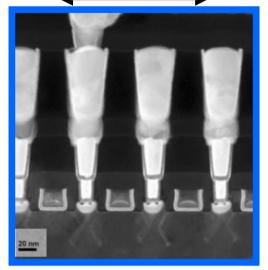

# Metrology Overview

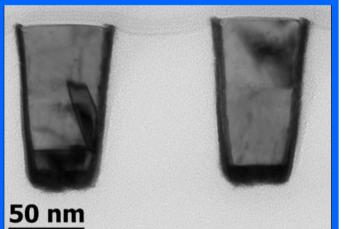

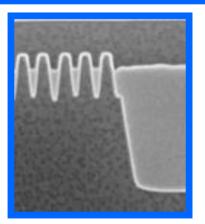

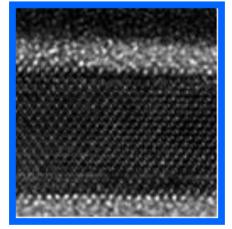

## **SEM and TEM**

## 10,000nm ▲ 10 u m

### **Multiple Layers**

1000nm 1 u m

### Single Layer

#### 100nm

10nm

Single Structure

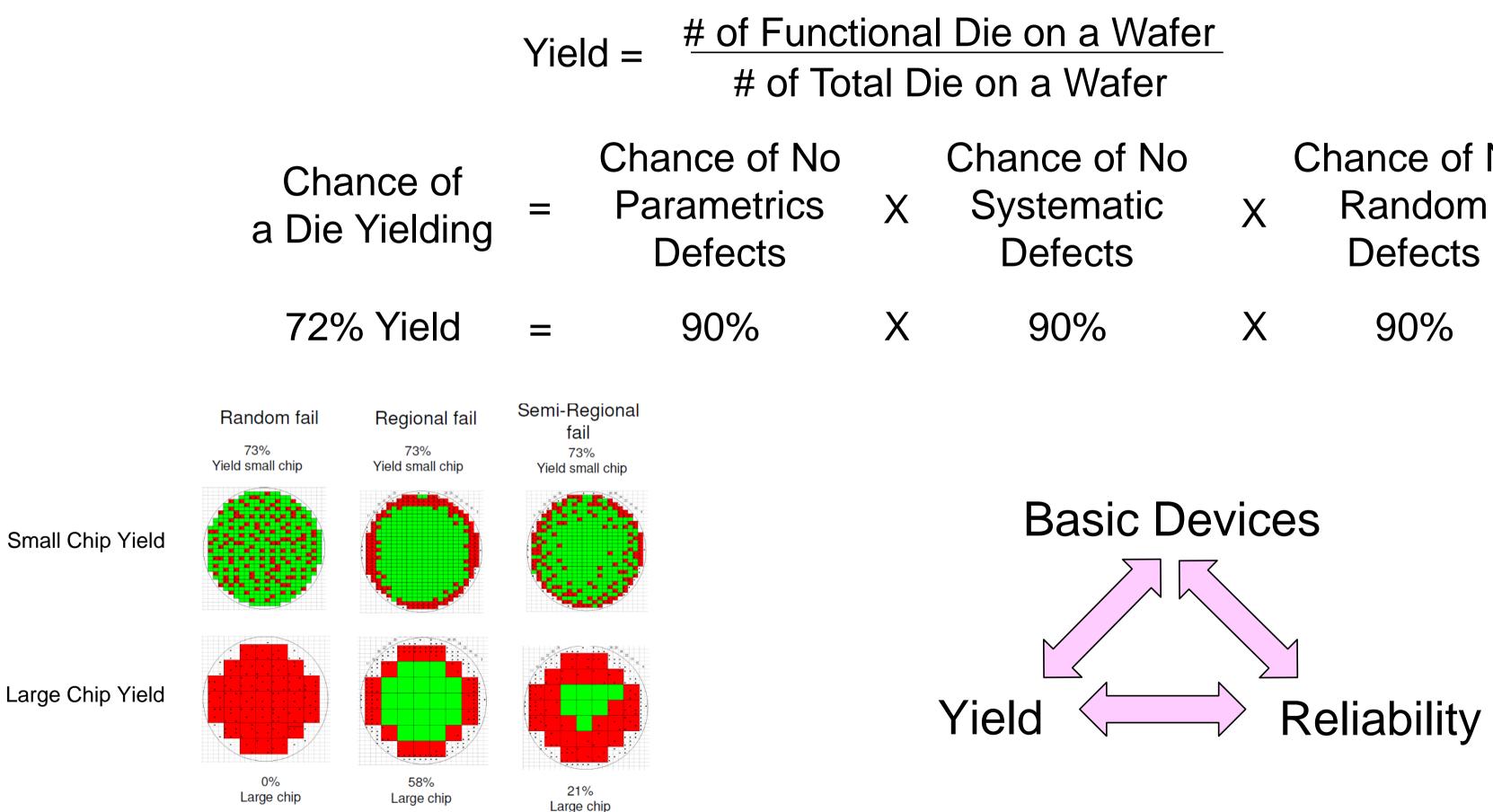

# **Yield is King**

Yield requires volume and constant battle with physics... ...volume requires commercial markets and investments

| on a Water                    |   |                                   |

|-------------------------------|---|-----------------------------------|

| a Wafer                       |   |                                   |

| ce of No<br>tematic<br>efects | Х | Chance of No<br>Random<br>Defects |

| 90%                           | Х | 90%                               |

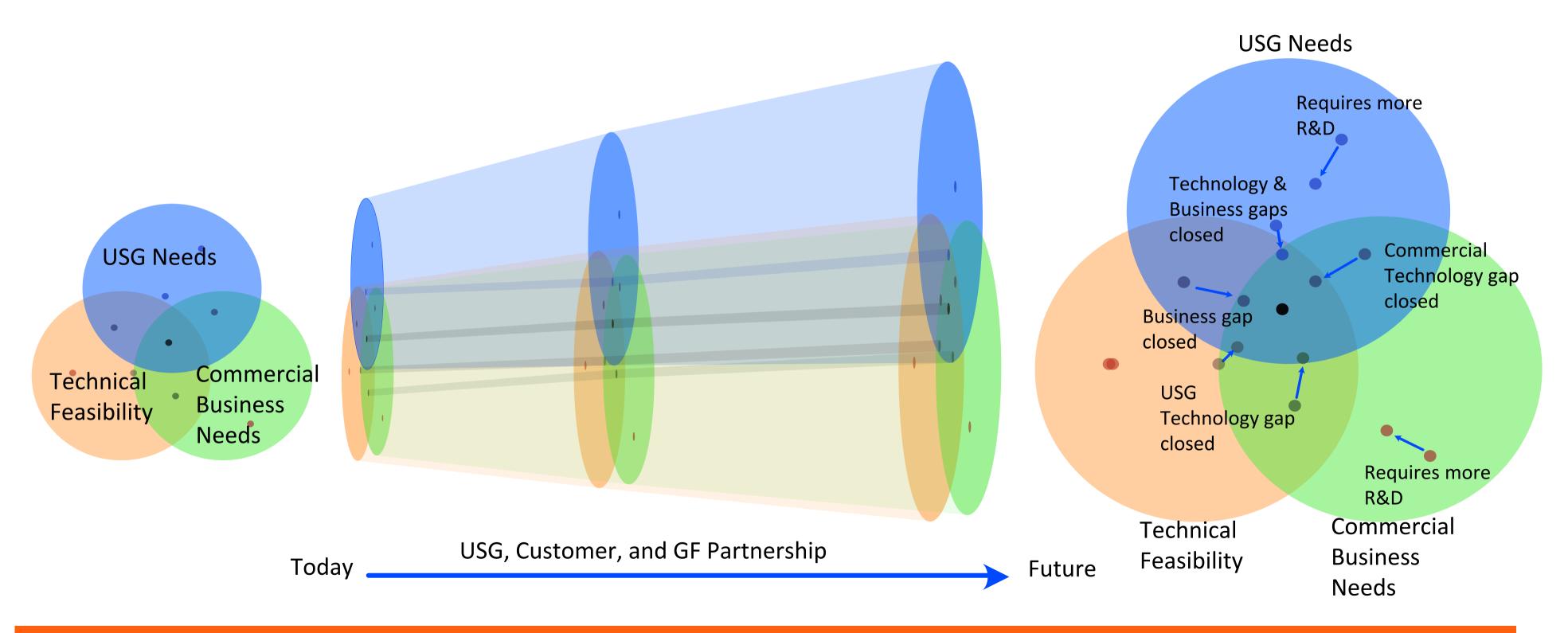

# **Aligned Futures Roadmap**

Opportunity for Maximizing technology alignment through Industrial Policy

Dual-use technology initiatives with USG partnership and funding to deliver domestic production capabilities and capacity for Critical Infrastructure and Specialized Defense needs

# Summary

Foundry Ecosystem and Technology is complex and at the edge of physics

- Foundry Ecosystem is the way that ideas are transformed to technology through differentiated microelectronics platforms driven by commercial market forces

- Systems require a diverse set of advanced technologies (majority >12nm): digital, analog, rf, mixed-signal, power, photonic, etc., to enable specialized capabilities

- Foundry Ecosystem requires design infrastructure, IP, and fabrication for masks and wafers, and advanced packaging for a diverse set of technologies and applications

- Yield and quality are the focus of foundry manufacturing and requires very high volume and a talented workforce looking at the finest of details

- Technologies optimized for dual use will require an alignment of roadmaps and funding from the USG and Customers

\*Thank you to Bill Taylor for a number of slides throughout the presentation.

BACKUP